**My First Altera® SoC FPGA

Exercise Manual

(Atlas-SoC / DE10-Nano board version)**

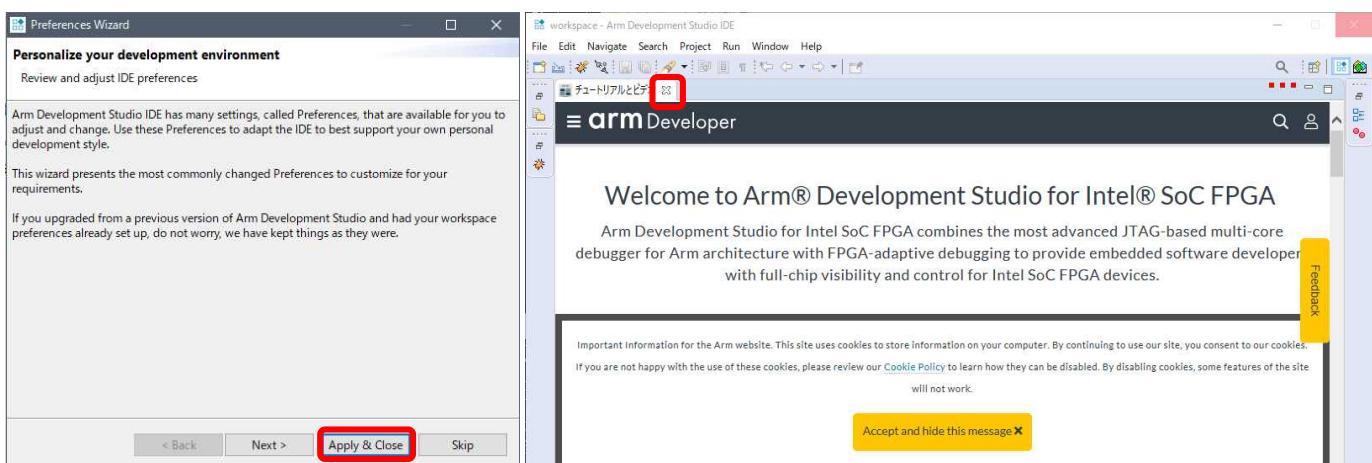

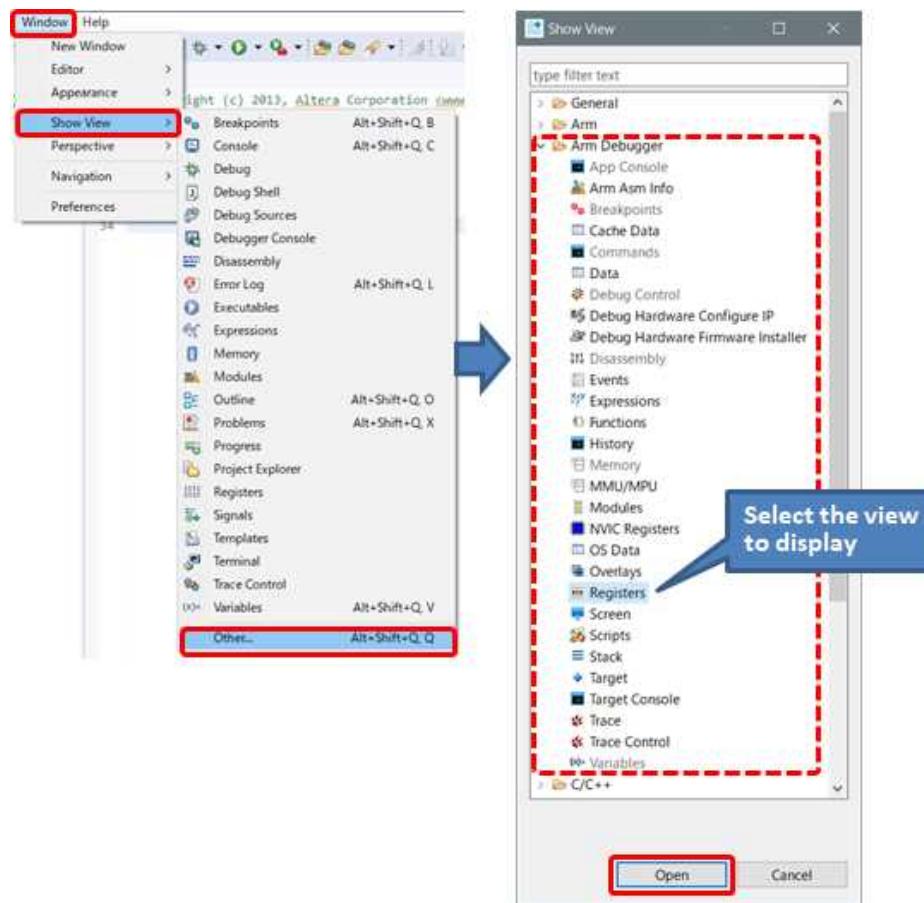

Ver.20.1

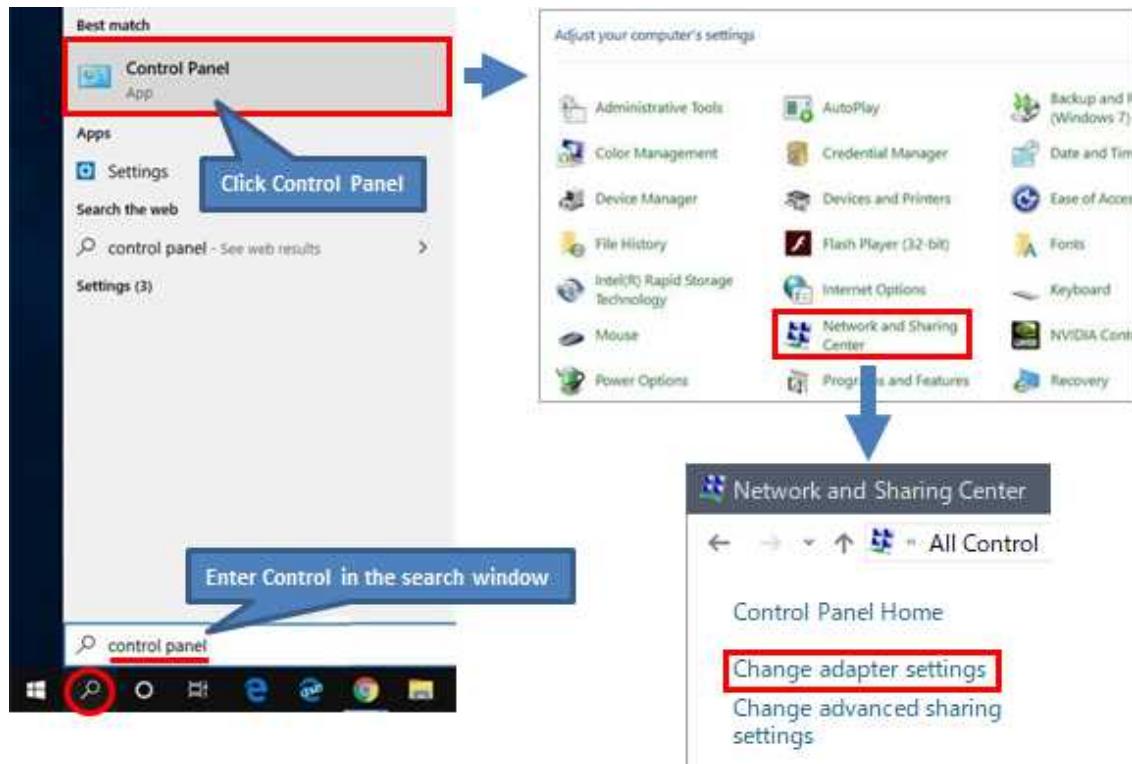

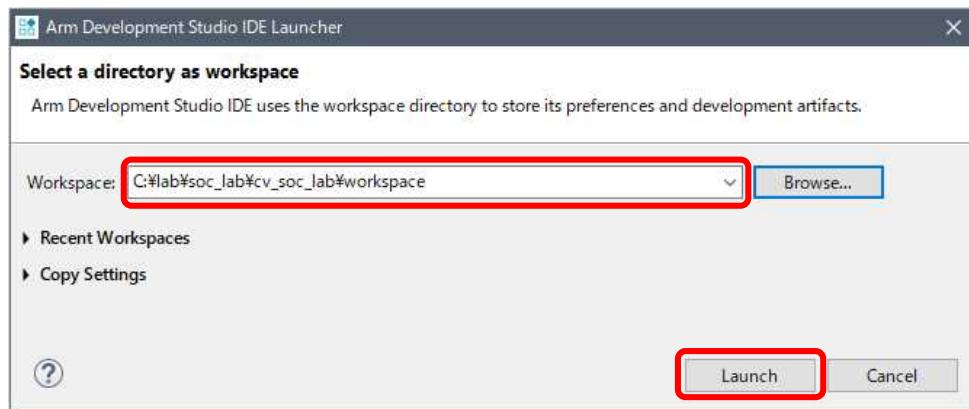

## Contents

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| <b>Before Reading This Manual</b>                                     | 4  |

| 1. Overview                                                           | 5  |

| 1-1. Requirements                                                     | 6  |

| 2. Board Setup                                                        | 7  |

| 2-1. Board Layout                                                     | 7  |

| 2-2. Power and cable connections                                      | 7  |

| 2-3. SW10 settings                                                    | 7  |

| 3. Lab 1: Hardware Exercise                                           | 8  |

| 3-1. Step 1: Hardware Exercise Open the design project                | 9  |

| 3-2. Step 2: Adding HPS Components                                    | 14 |

| 3-3. Step 3: HPS Peripheral Settings (MAC, UART, I2C, SDIO, USB)      | 20 |

| 3-4. Step 4: Set the HPS Clock                                        | 25 |

| 3-5. Step 5: Configuring SDRAM                                        | 27 |

| 3-6. Step 6: Setting the HPS Clock and Export Signal                  | 33 |

| 3-7. Step 7: Connecting HPS Components to Other Components            | 35 |

| 3-8. Step 8: Connect Resets and Assign Base Addresses                 | 37 |

| 3-9. Step 9: Checking the Platform Designer System                    | 38 |

| 3-10. Step 10: Generate the Platform Designer system                  | 40 |

| 3-11. Step 11: Set pin assignments and compile Quartus® Prime project | 44 |

| 3-12. Step 12: Verify the output file                                 | 48 |

| 4. Lab 2 - Software Exercise (1) Generate Preloader                   | 49 |

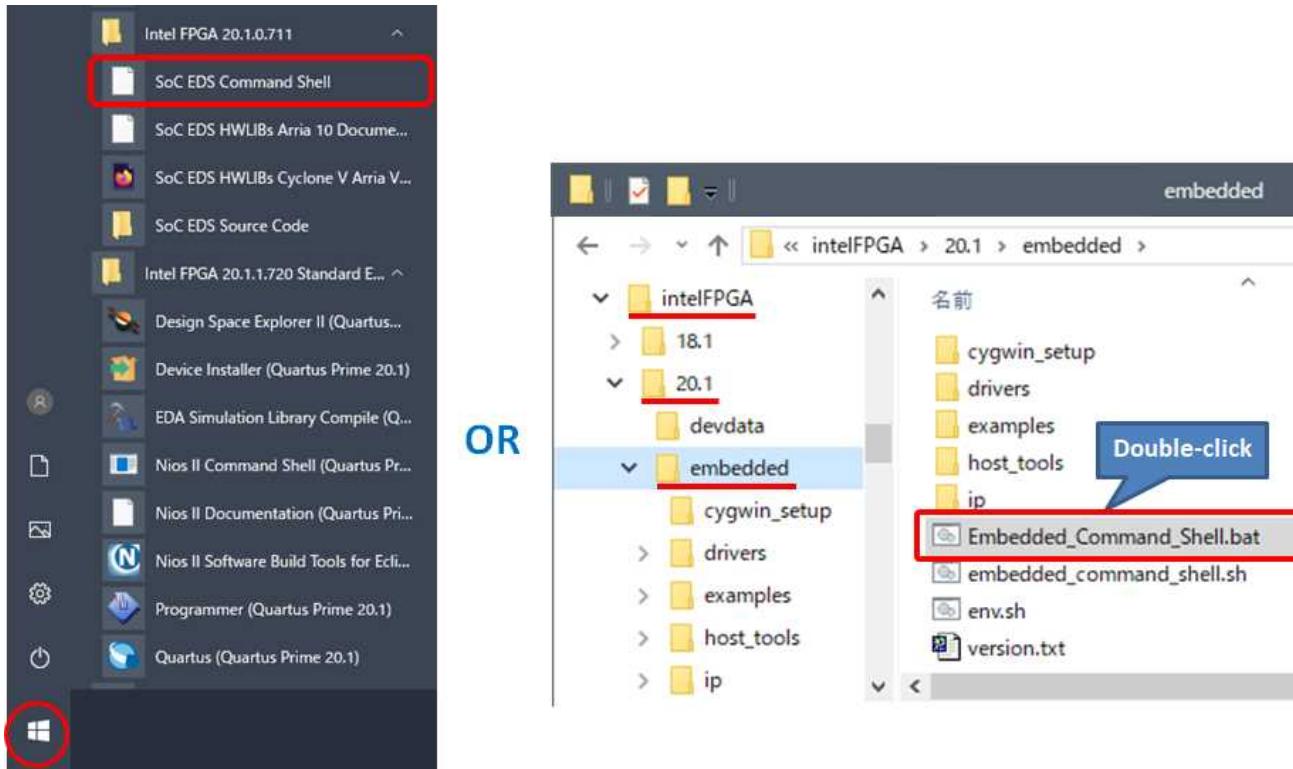

| 4-1. Step 1: Launch Embedded Command Shell                            | 50 |

| 4-2. Step 2: Generate the bsp project                                 | 51 |

| 4-3. Step 3: Launch Preloader Build Environment                       | 53 |

| 4-4. Step 4: Build Preloader                                          | 55 |

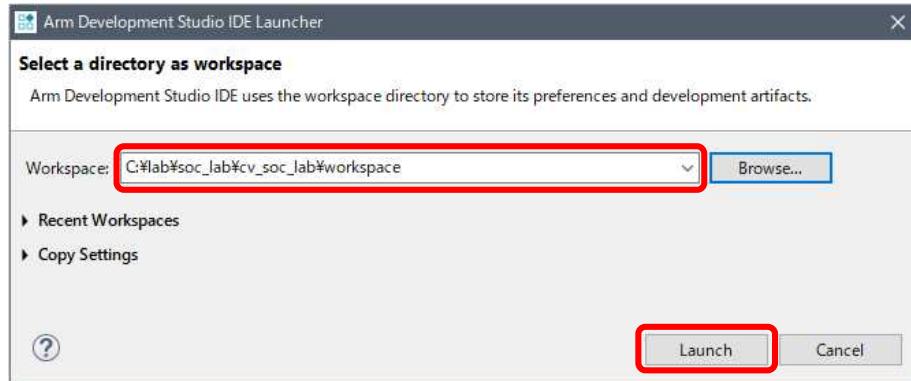

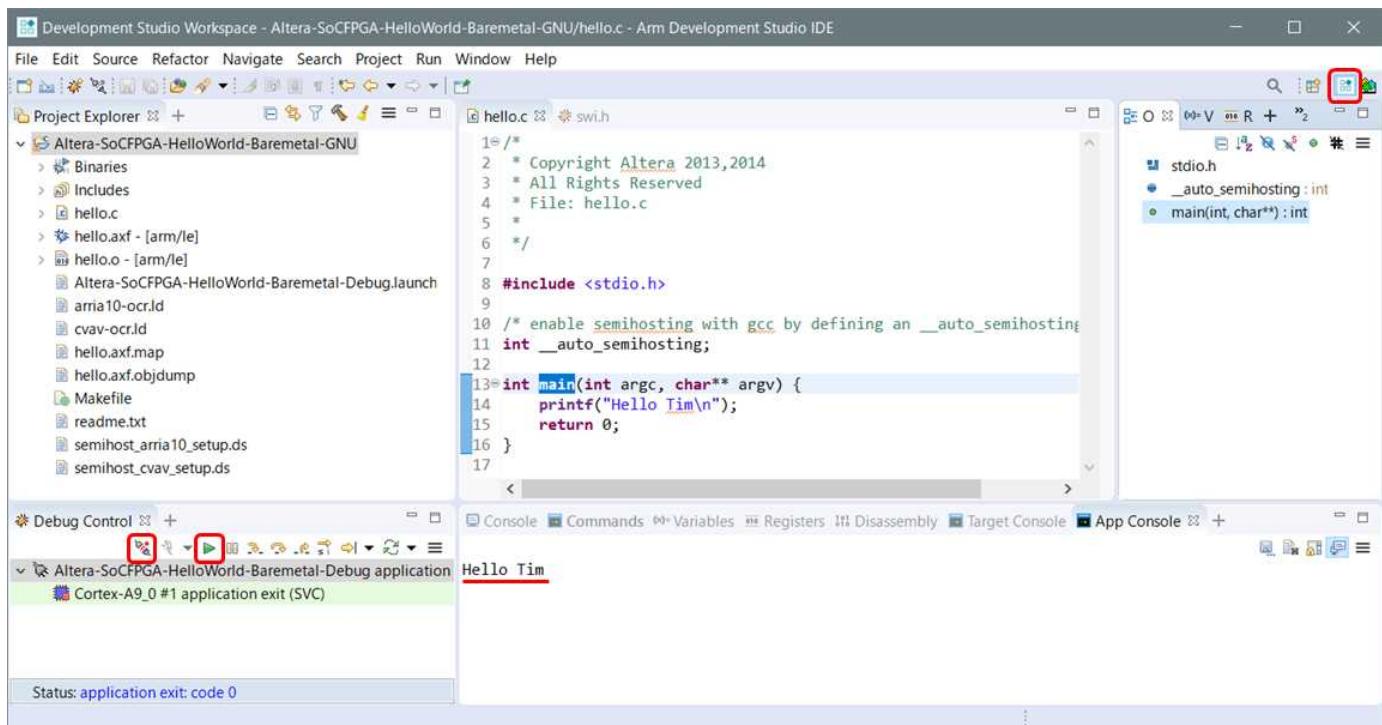

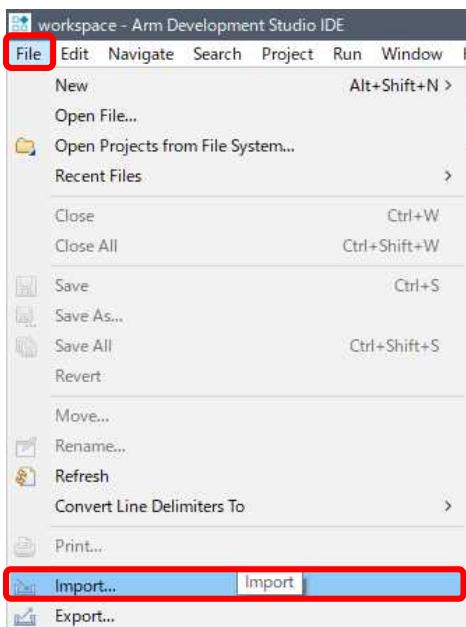

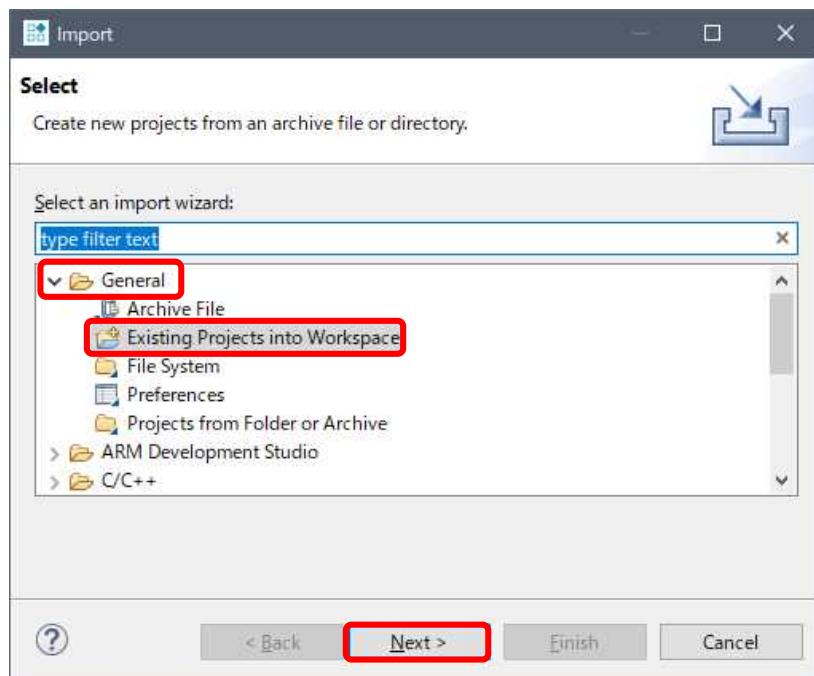

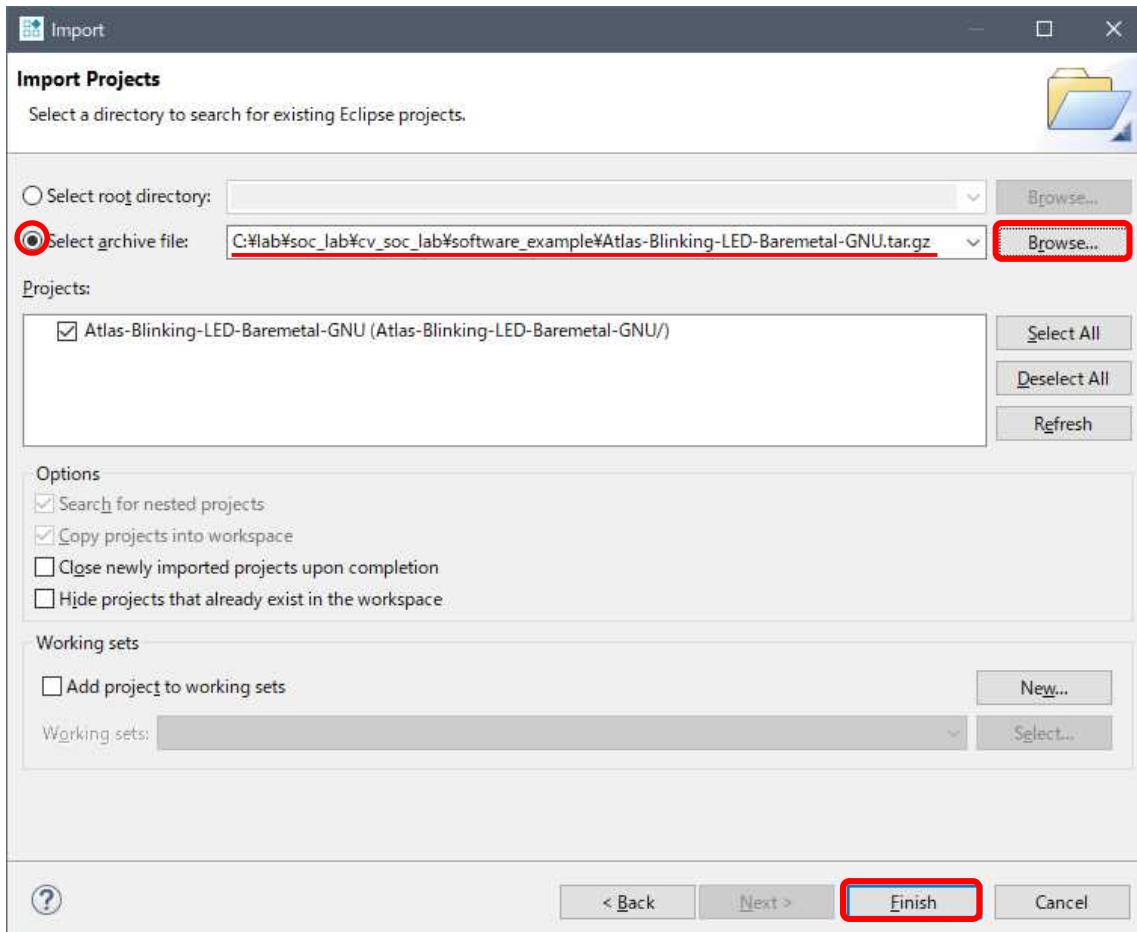

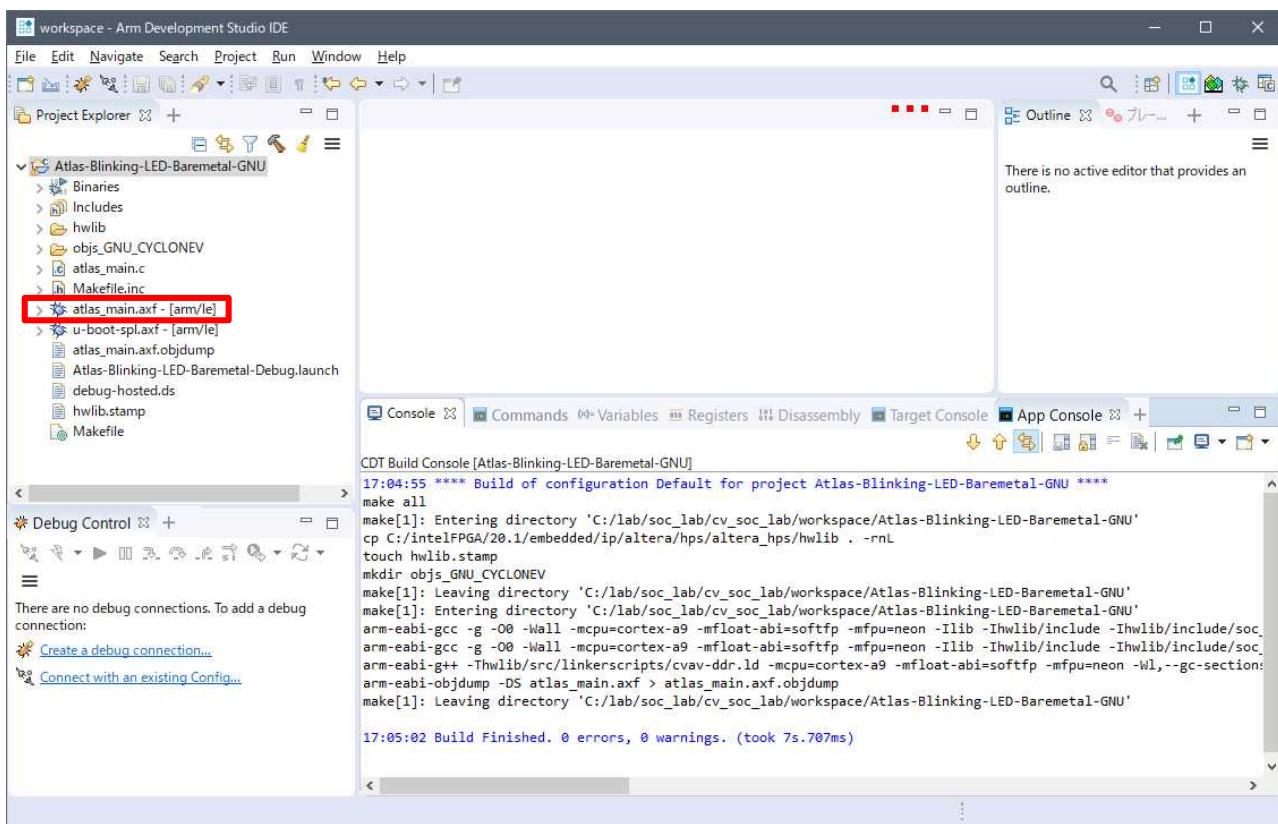

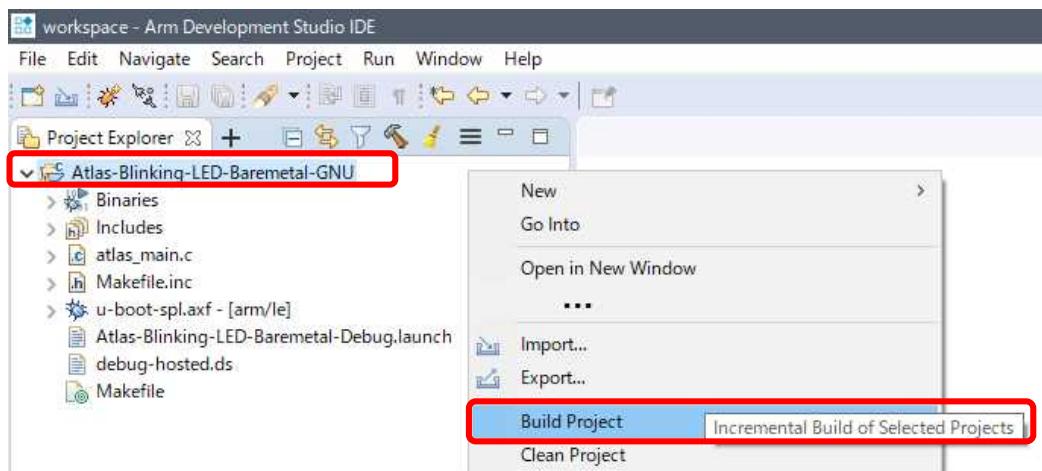

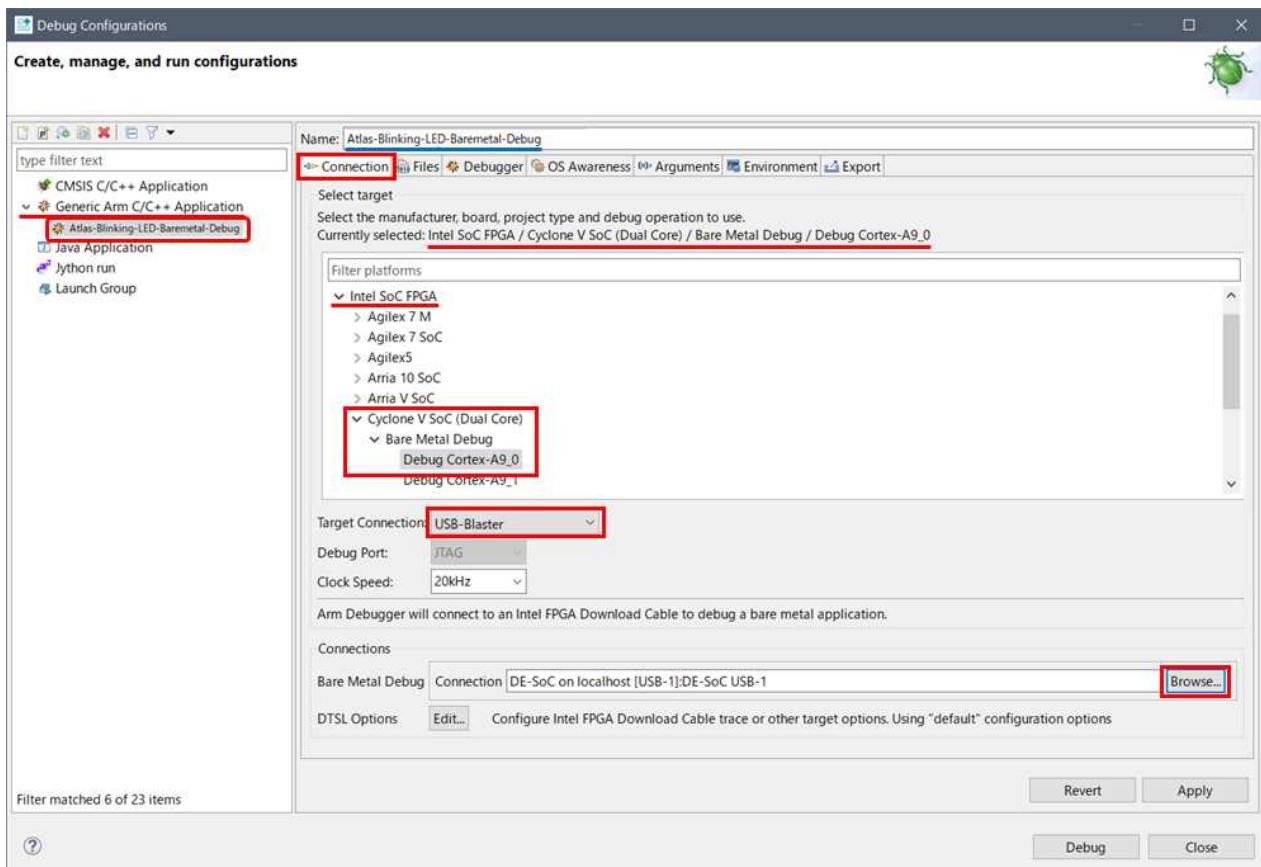

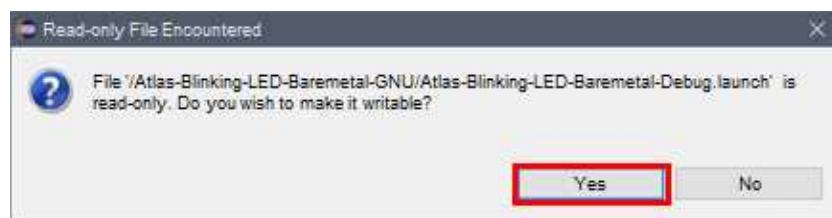

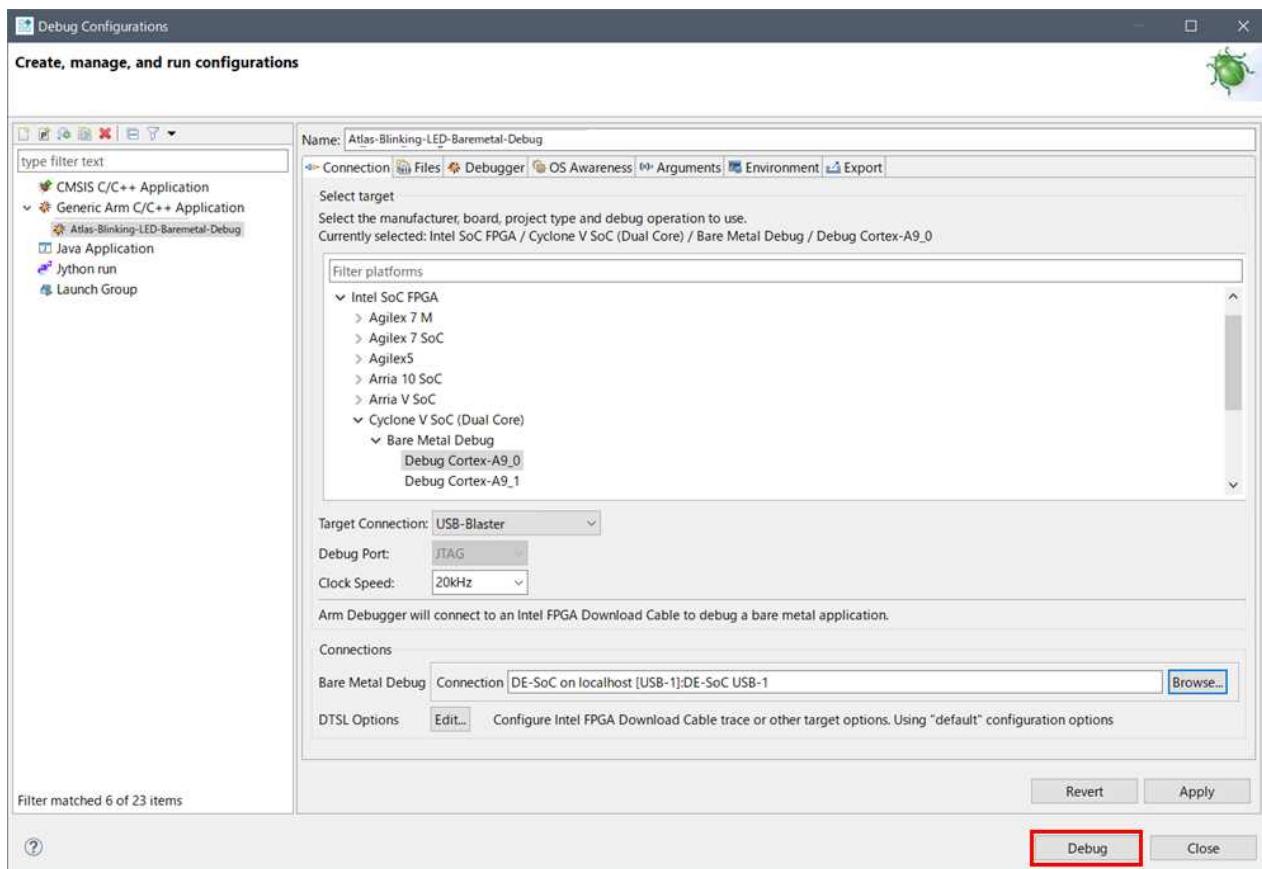

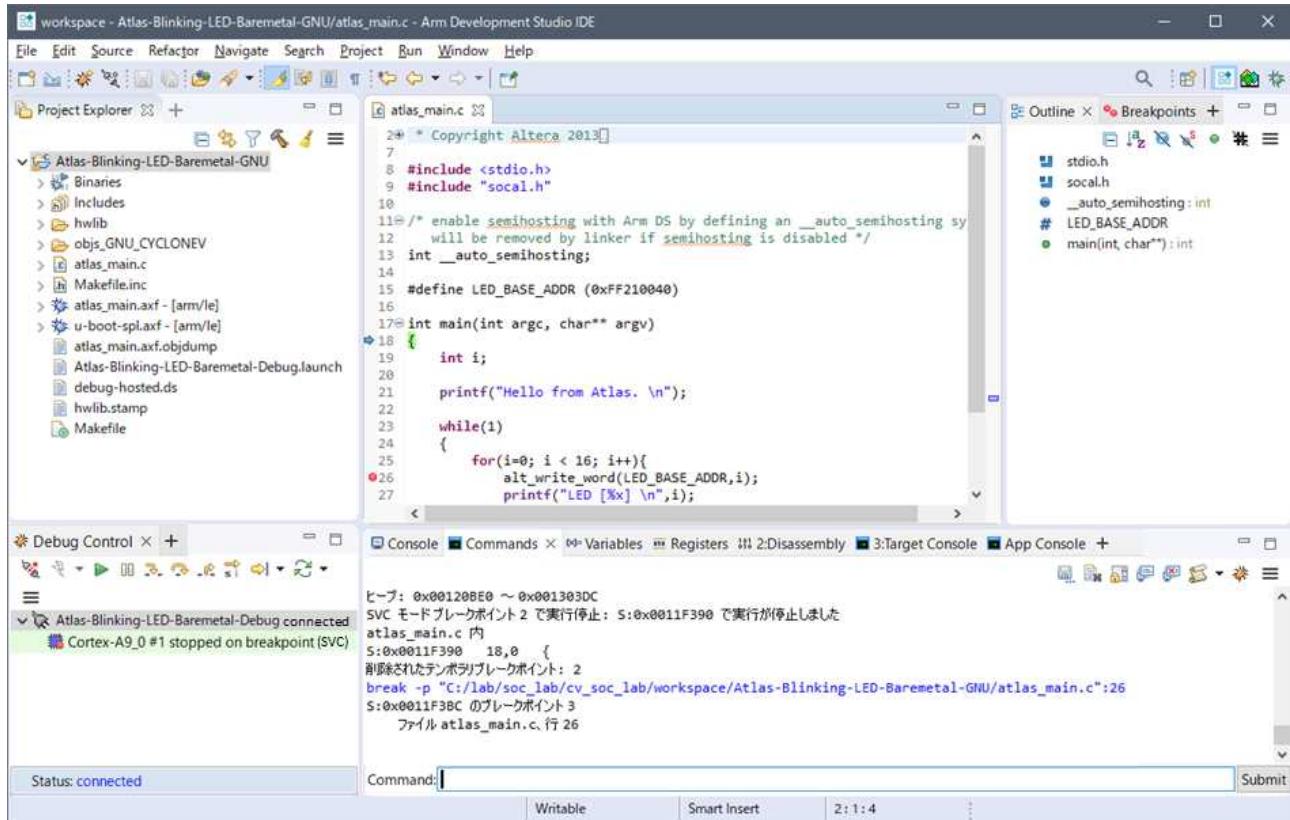

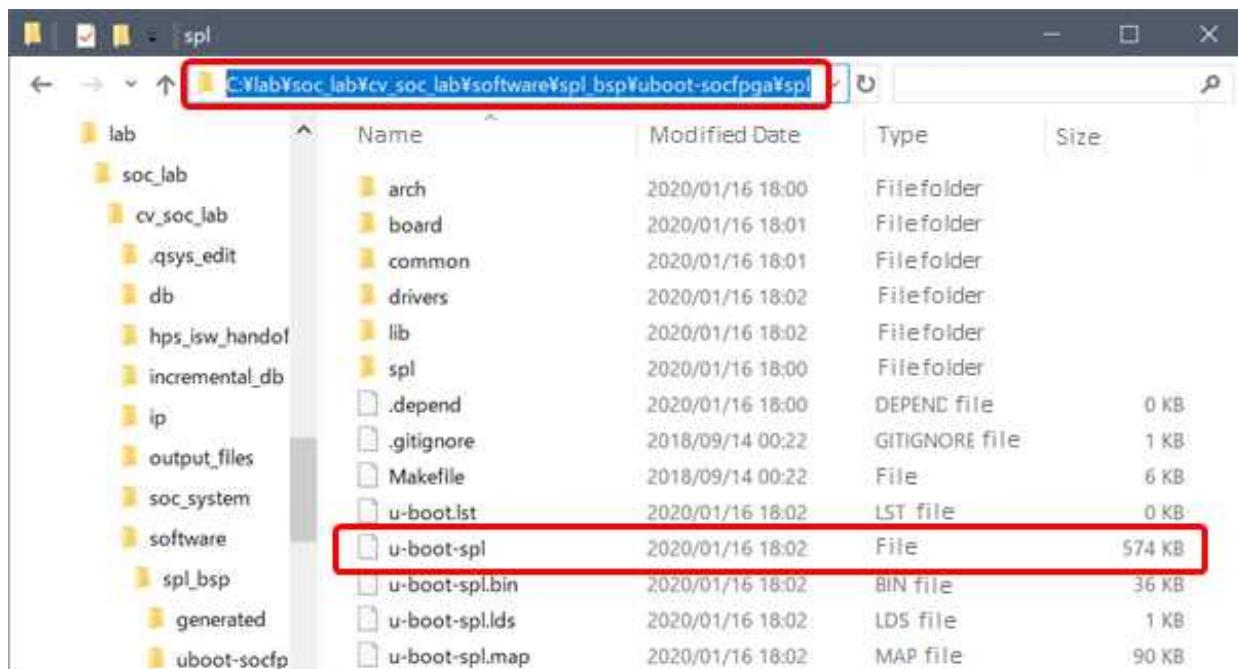

| 5. Lab 3: Software Exercise (2) Bare Metal Application                | 59 |

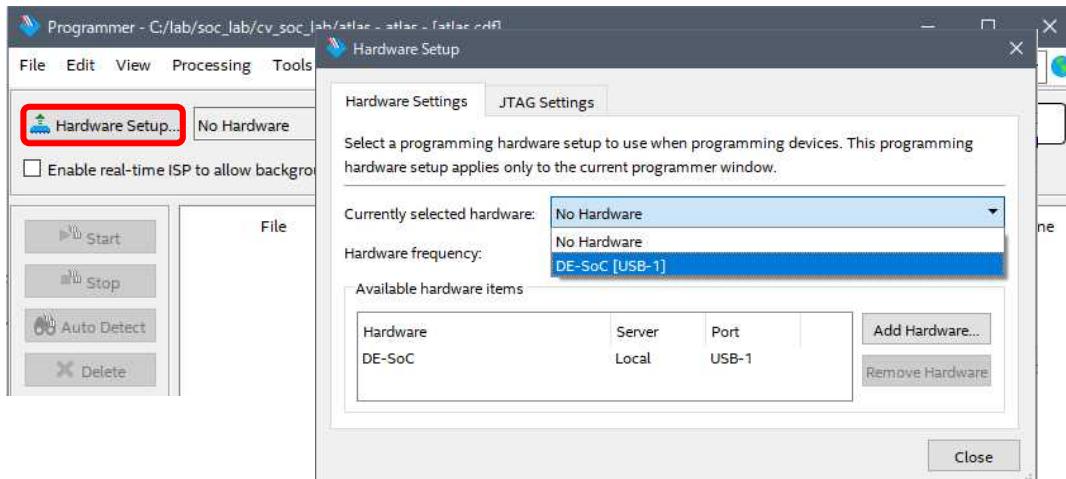

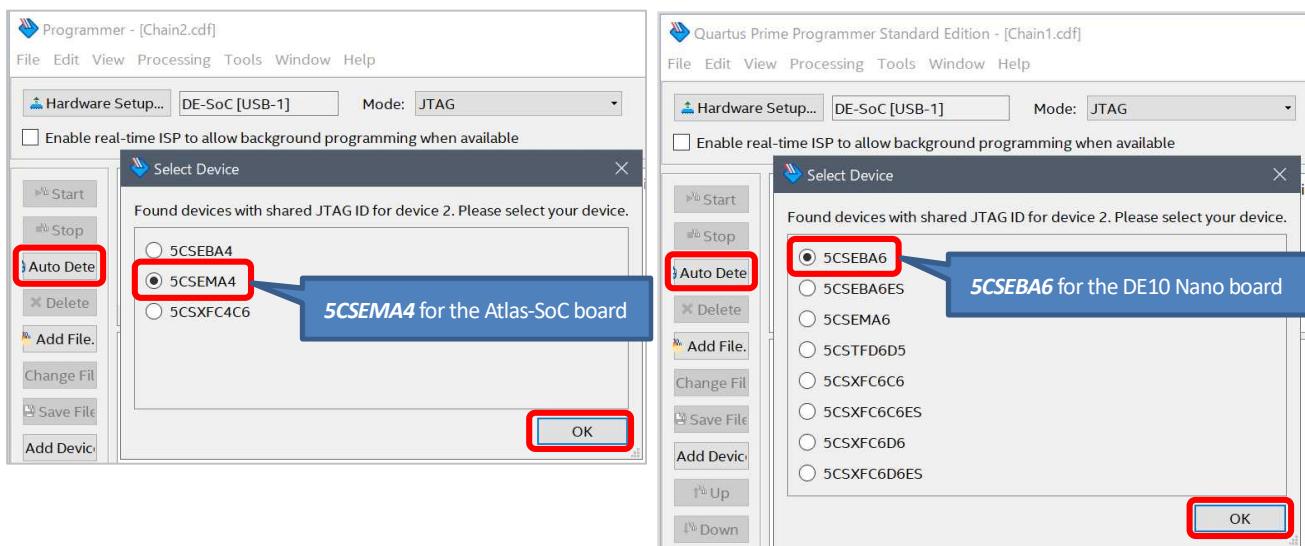

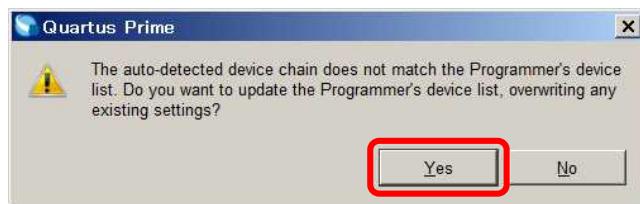

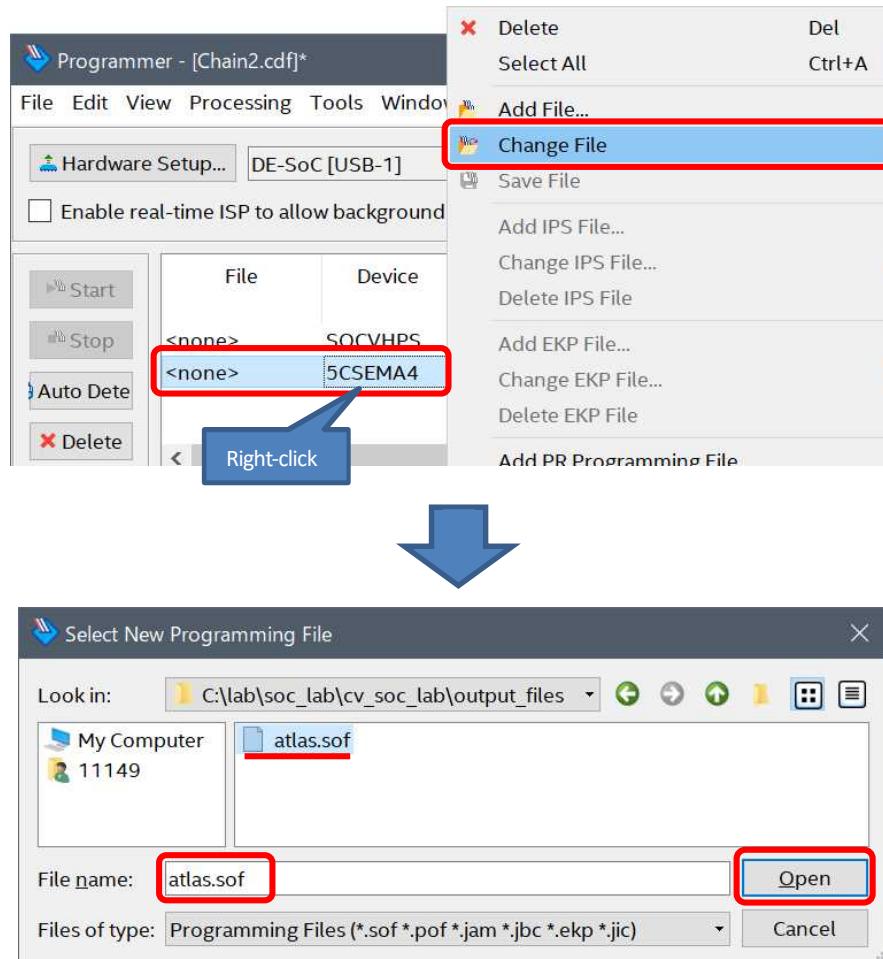

| 5-1. Download the FPGA Design                                         | 60 |

|                                                                            |     |

|----------------------------------------------------------------------------|-----|

| 5-2. Run the Hello World sample application.....                           | 63  |

| 5-3. Running the LED Blink Sample Application .....                        | 72  |

| 5-4. Initialize with Preloader created in Lab 2 (optional exercise).....   | 79  |

| 5-5. Address resolution using system header files (optional exercise)..... | 81  |

| 6. Lab 4: Linux Application Exercise (optional exercise).....              | 84  |

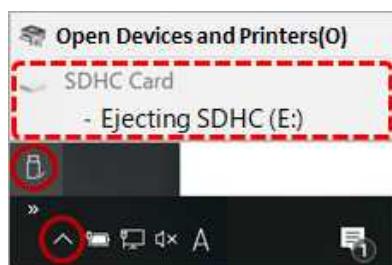

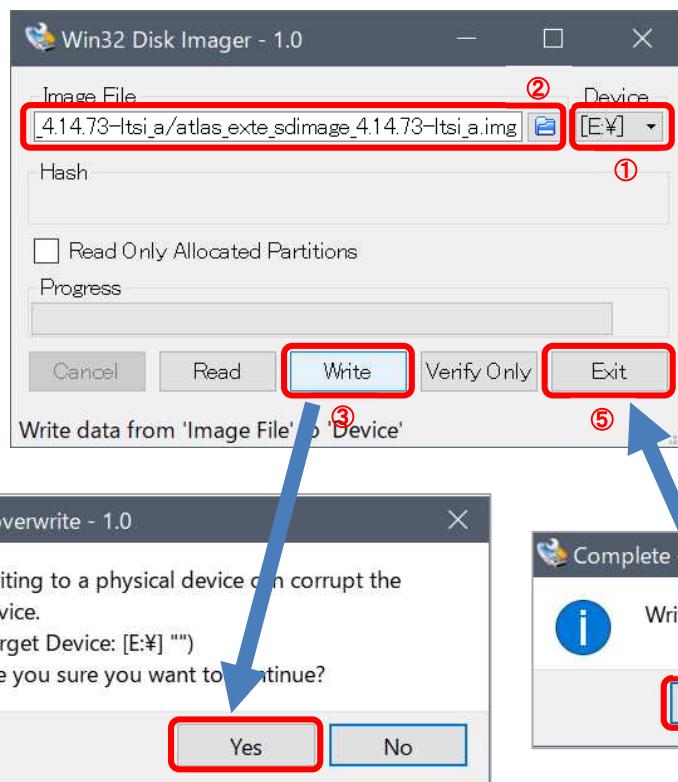

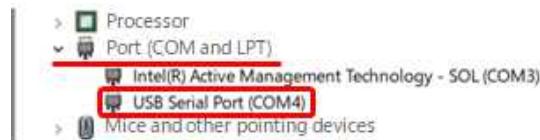

| 6-1. Preparing the microSD card .....                                      | 84  |

| 6-2. Linux Boot and Login .....                                            | 86  |

| 6-3. Setting the IP Address and Password on Linux.....                     | 88  |

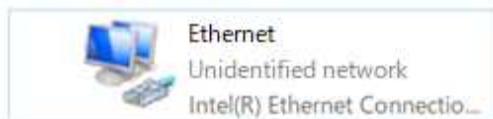

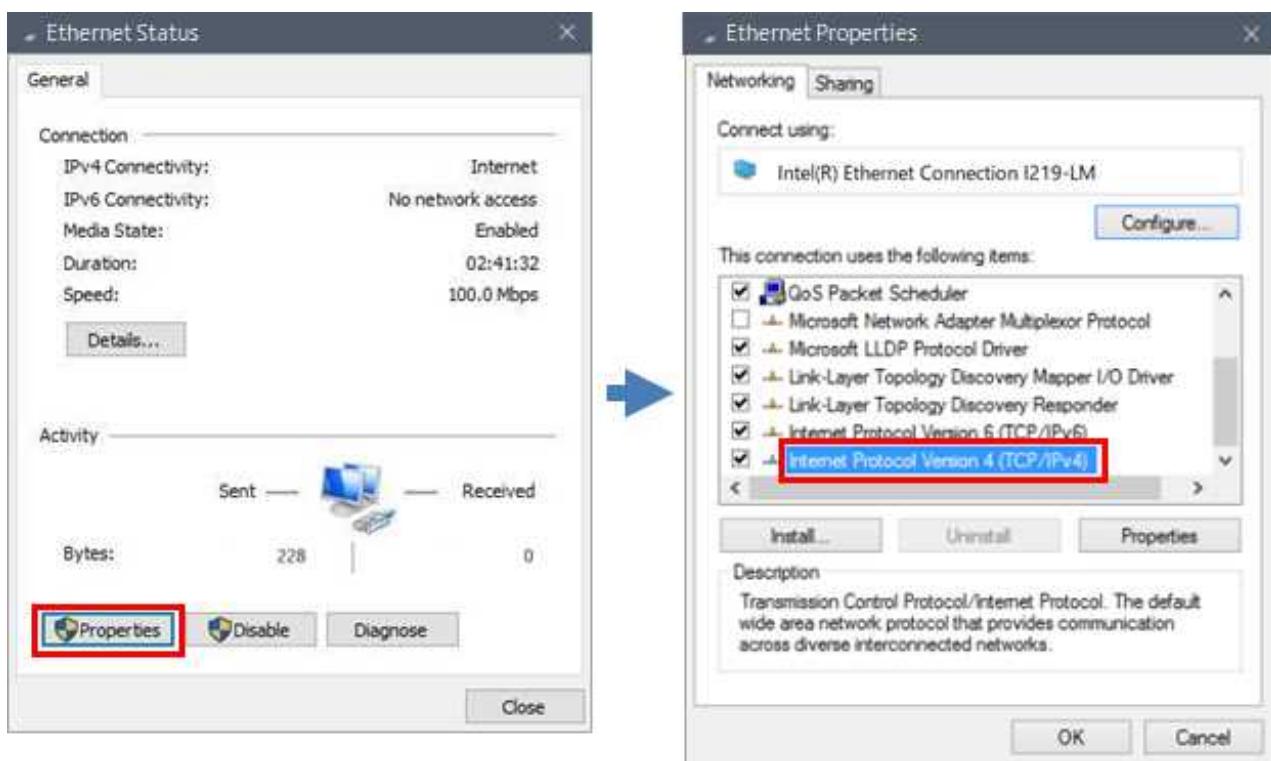

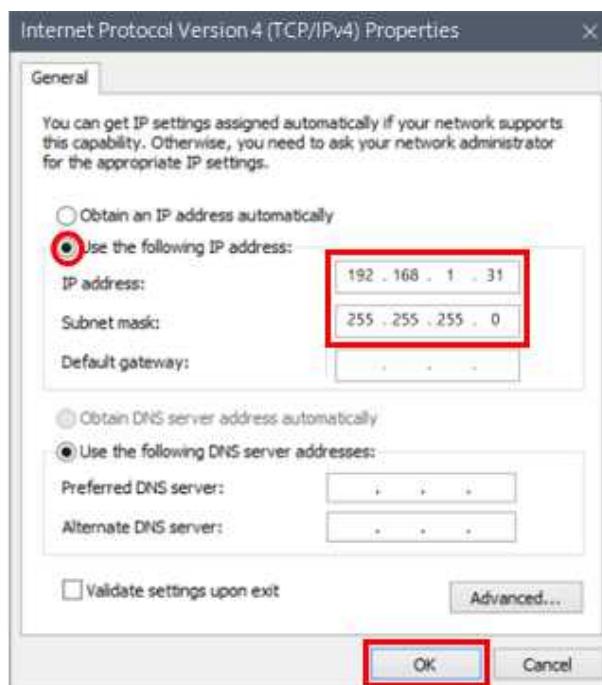

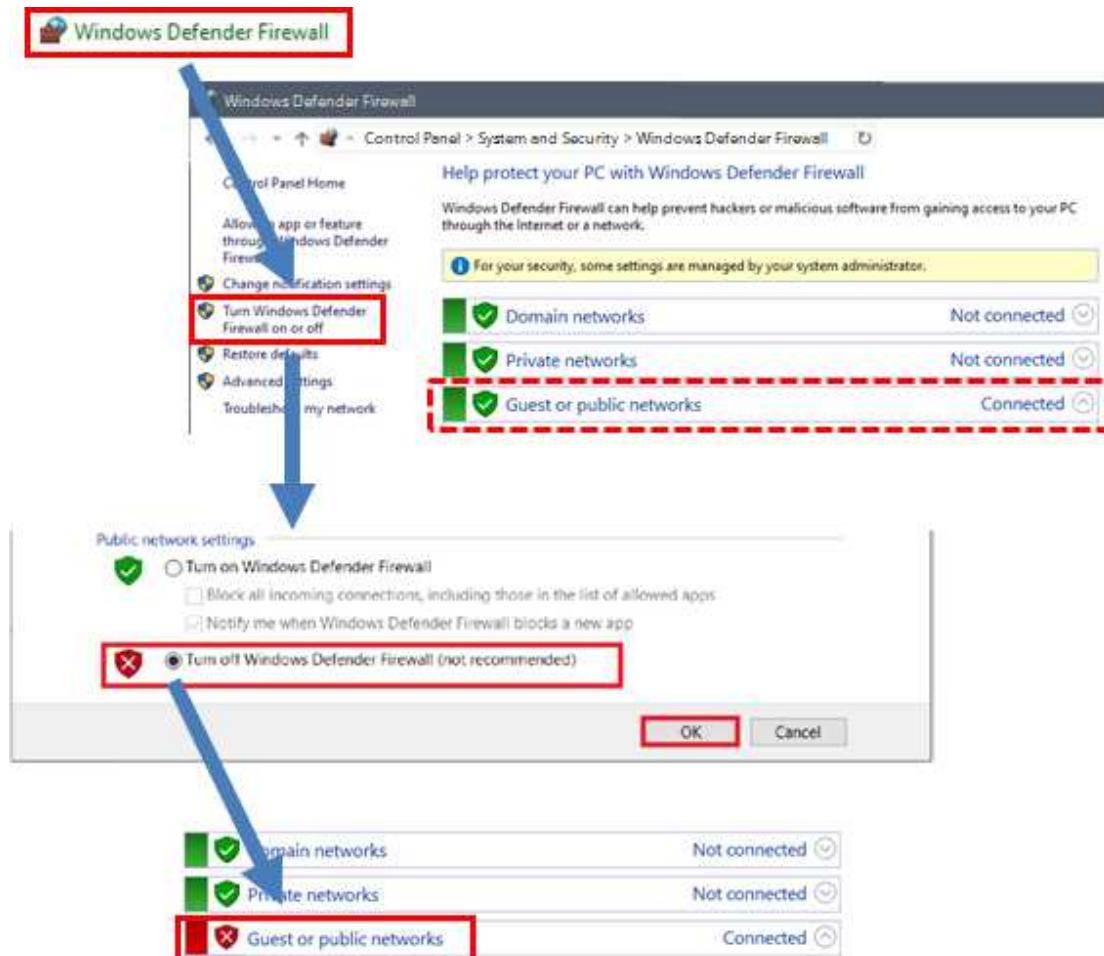

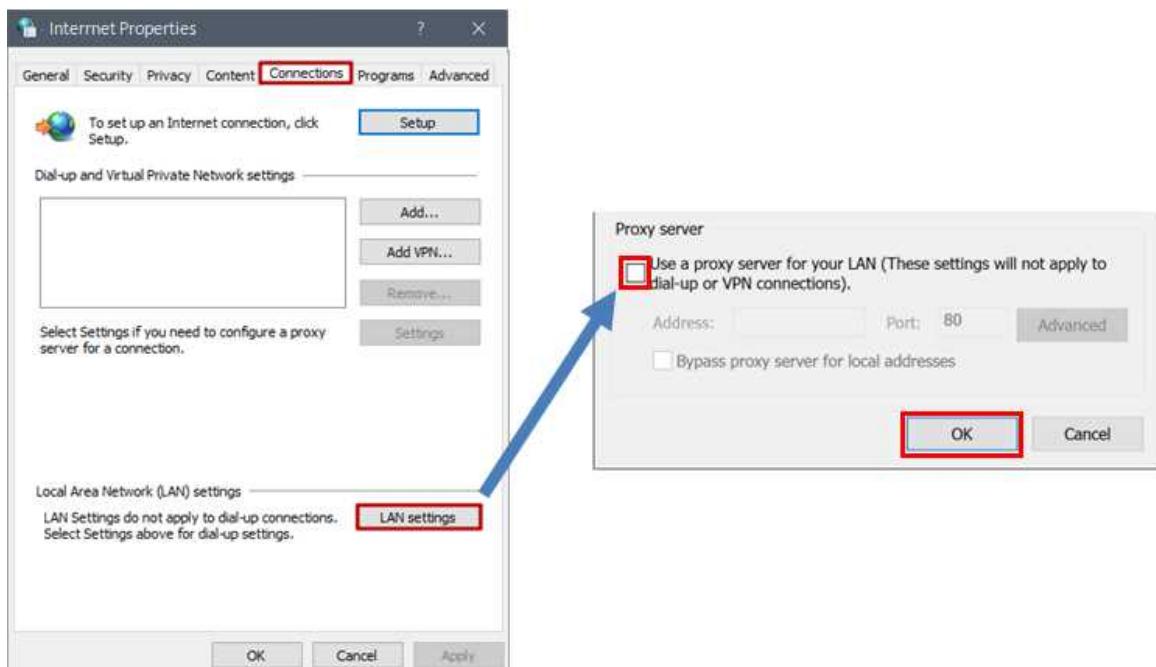

| 6-4. Network Settings on the Host PC .....                                 | 89  |

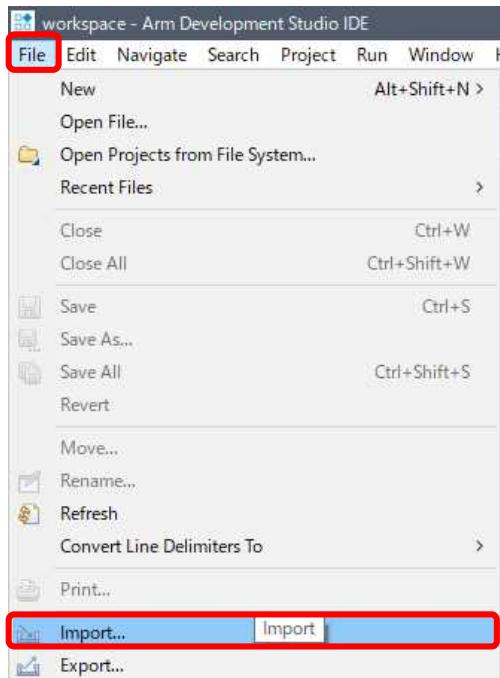

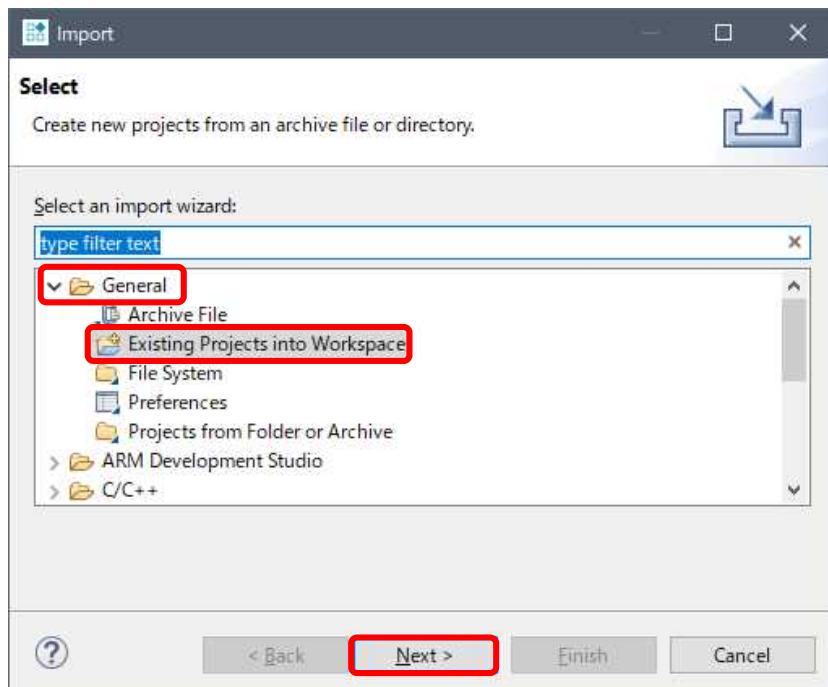

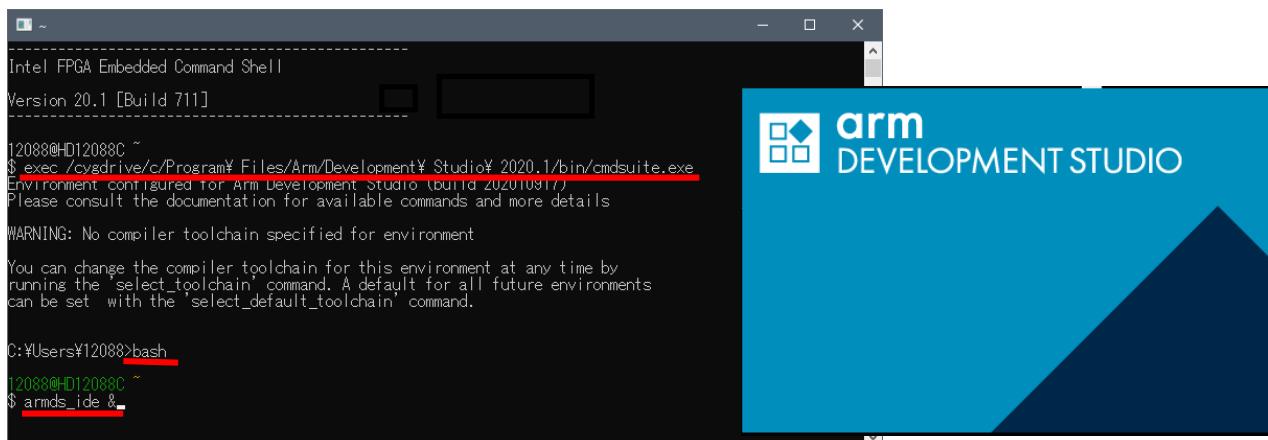

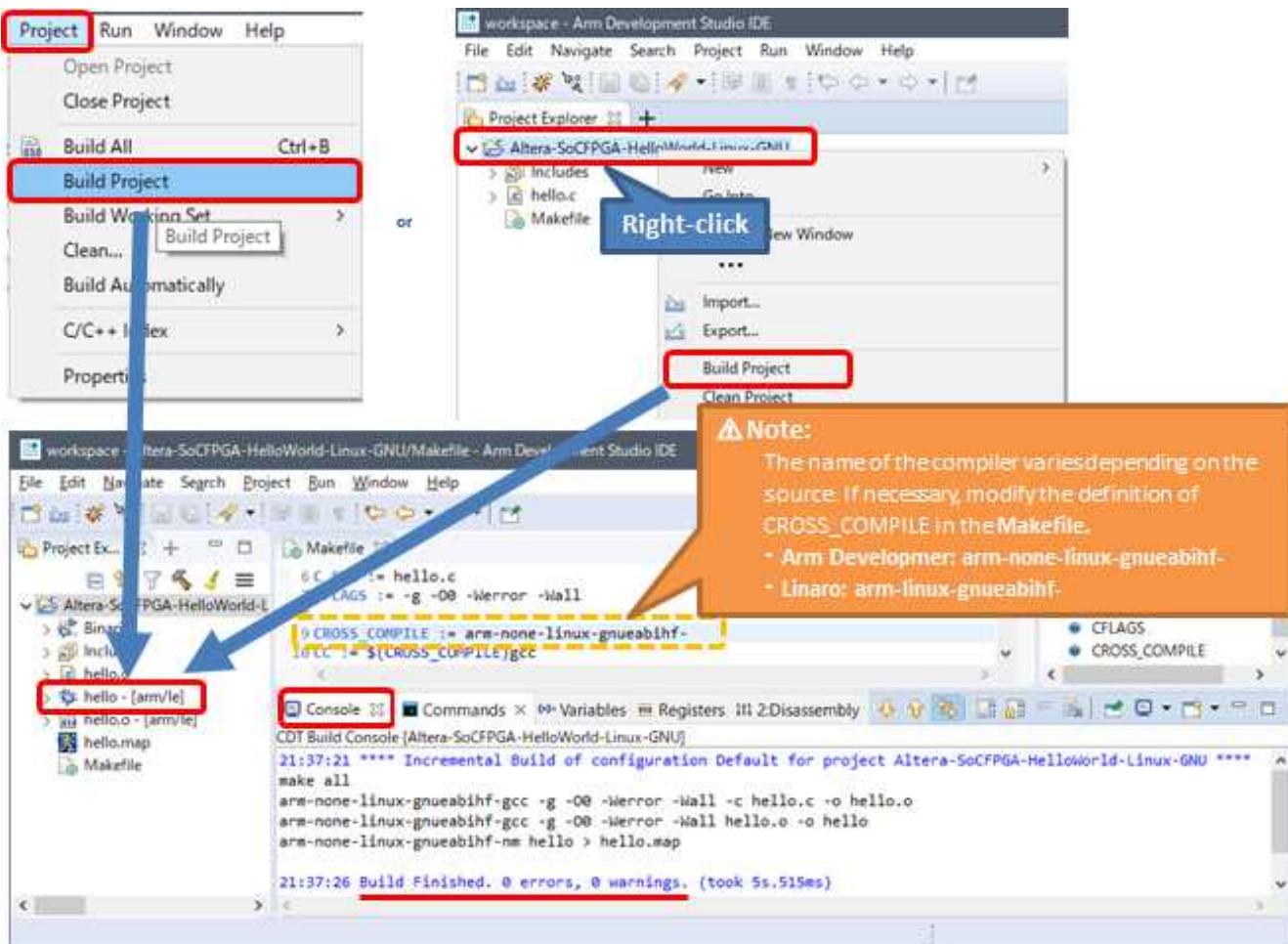

| 6-5. Start Arm® DS and import and build the Linux sample application ..... | 92  |

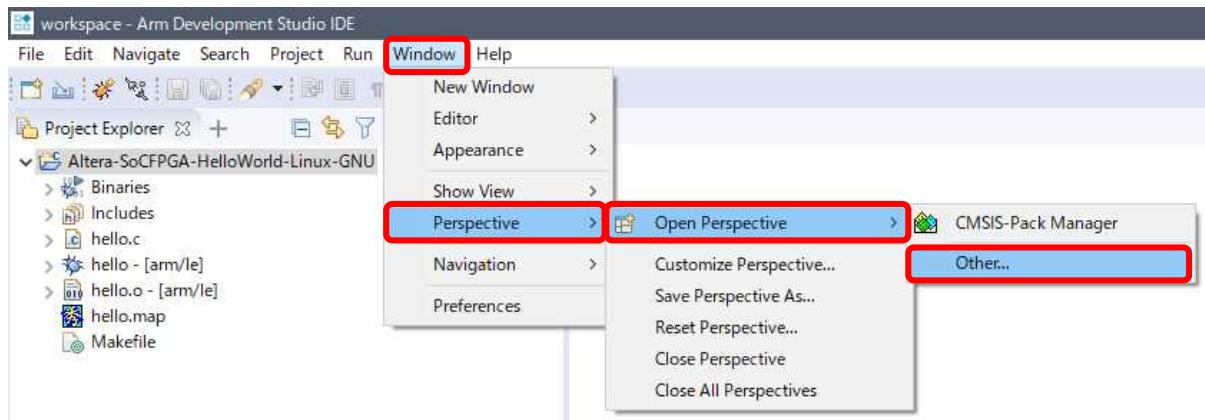

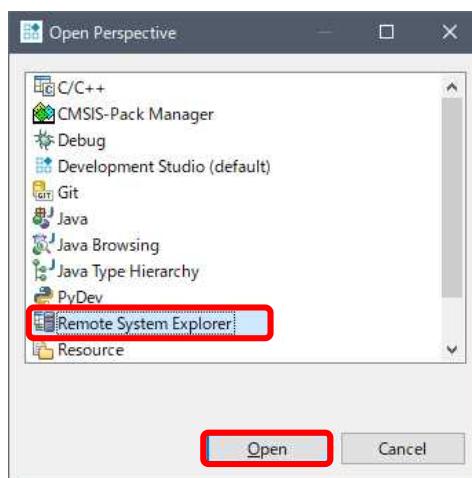

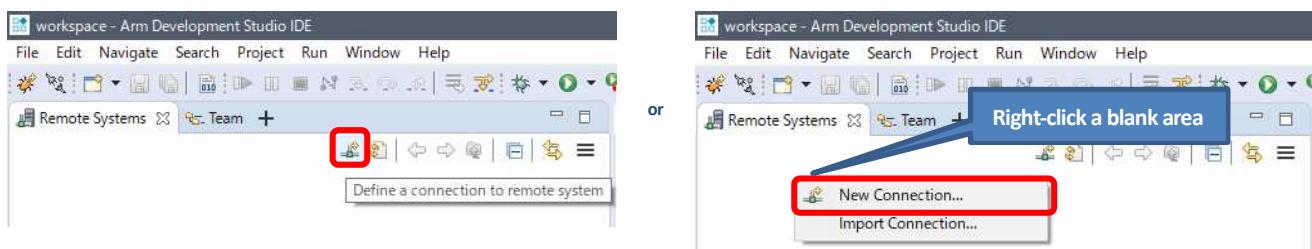

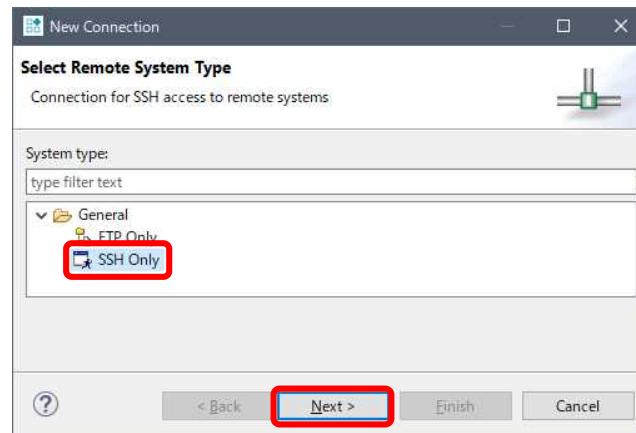

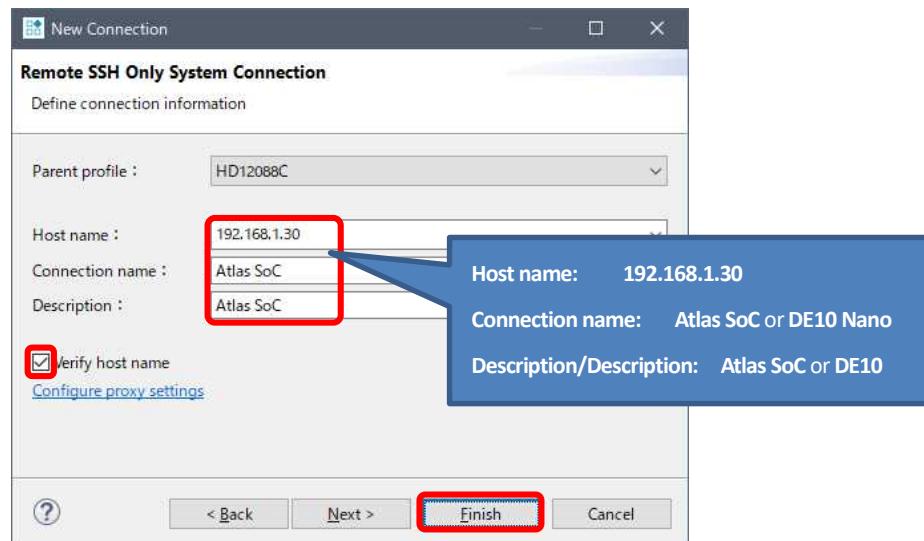

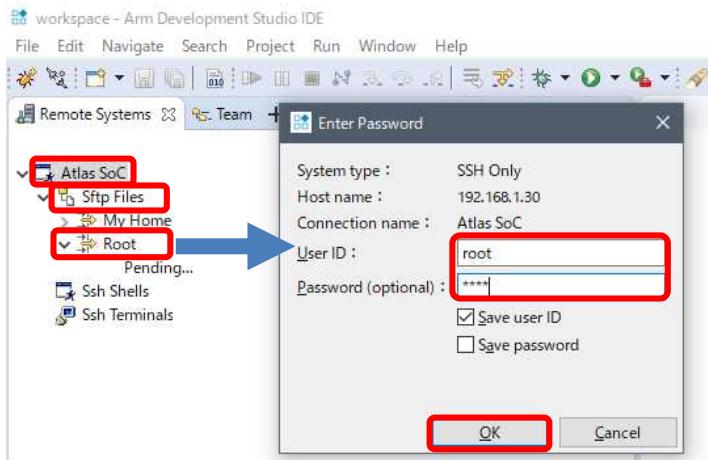

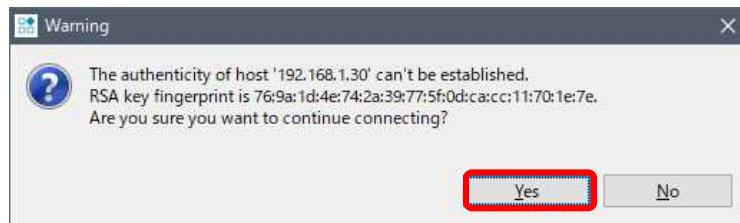

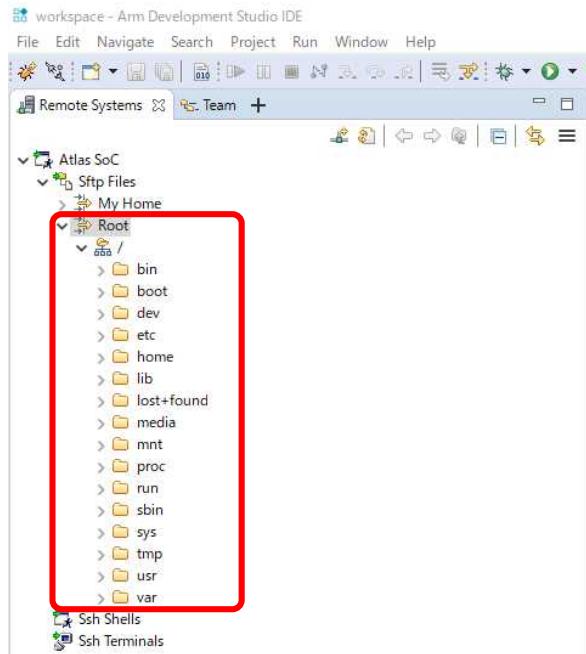

| 6-6. Setting up Remote System Explorer (RSE).....                          | 99  |

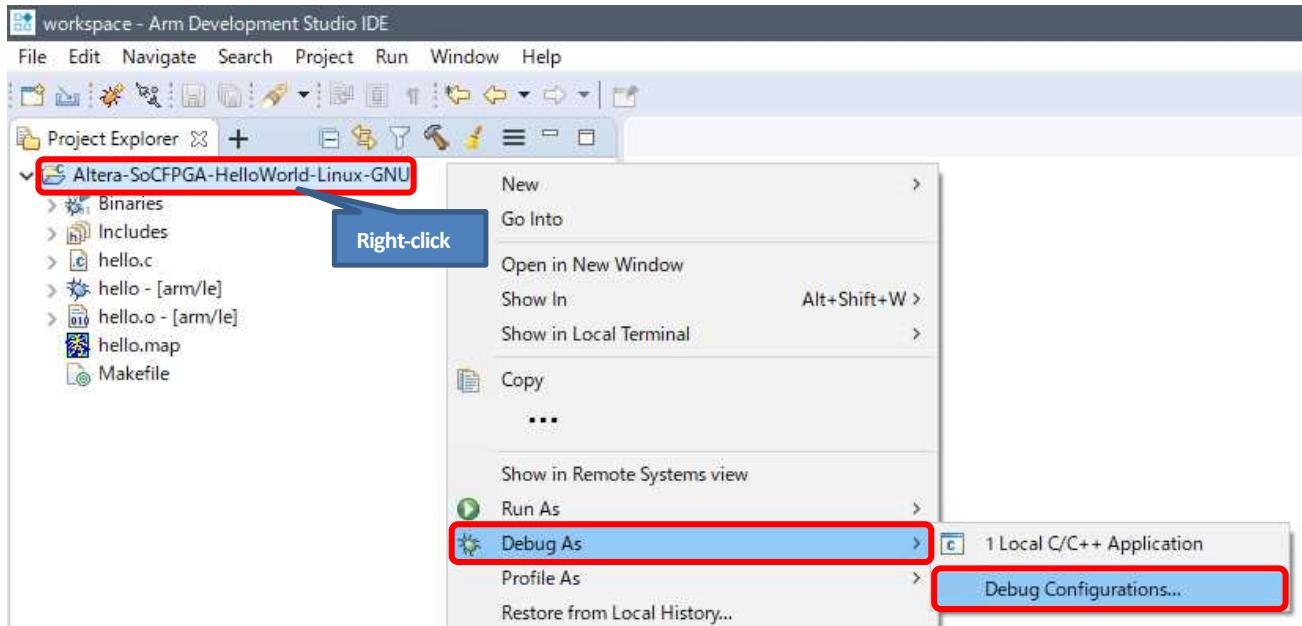

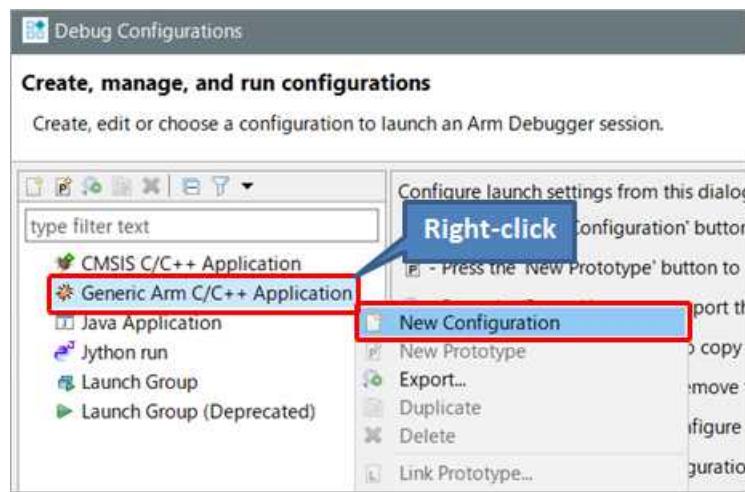

| 6-7. Running and Debugging Linux Applications .....                        | 103 |

| 7. Future reference materials .....                                        | 110 |

| Revision History .....                                                     | 111 |

## Before Reading This Manual

The contents of this manual are current as of February 2025.

Some of the software, hardware, and operating procedures described in this manual are common even if they are not the specified versions or devices, but some of them may not be common.

### Symbols in Documentation

|                                                                                                     |                                                                                                        |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|  <b>Info</b>       | Provides supplementary information.                                                                    |

|  <b>Point</b>      | Important points are included.                                                                         |

|  <b>Reference</b>  | Reference materials and sites are introduced to deepen your understanding.                             |

|  <b>Note</b>       | Although not discussed in detail in this document, the information and knowledge required is provided. |

|  <b>Prohibited</b> | Notes and what not to do are provided.                                                                 |

### Notations in sentences

|                                                                                                 |                                                                                       |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <u><b>Underline</b></u>                                                                         | Click to jump to another chapter in the document or to an external site.              |

| <b><i>Bold italic</i></b>                                                                       | Indicates the characters displayed on menus and windows when operating on the screen. |

|  <b>xxxxxx</b> | Indicates the command string to be entered.                                           |

| <b>Shaded</b>                                                                                   | Indicates the tool to be used.                                                        |

## 1. Overview

In this exercise, you will learn how to develop Cyclone® V SoC hardware and software using the Cyclone® V SoC FPGA evaluation kit DE0-Nano-SoC Kit/Atlas-SoC Kit (Atlas-SoC board below) or DE10-Nano Kit (DE10 Nano board below).

By completing this exercise, you will learn the basic operations of the Quartus® Prime development software, the development environment for Altera® SoC FPGA, the Platform Designer system configuration tool (formerly known as Qsys System Integration Tool), and the SoC FPGA Embedded Development Suite (SoC EDS) software development environment.

This exercise consists of the following 4 parts:

- Lab 1: Hardware Exercise

- Lab 2: Software Exercise (1)

- Lab 3: Software Exercise (2)

- Lab 4: Linux Application Exercise (optional exercise)

Lab 1 uses Quartus® Prime to configure the hardware including the Arm® processor and design a simple SoC system.

Lab 2 uses the SoC EDS tool to generate the 28 nm generation boot loader, Preloader.

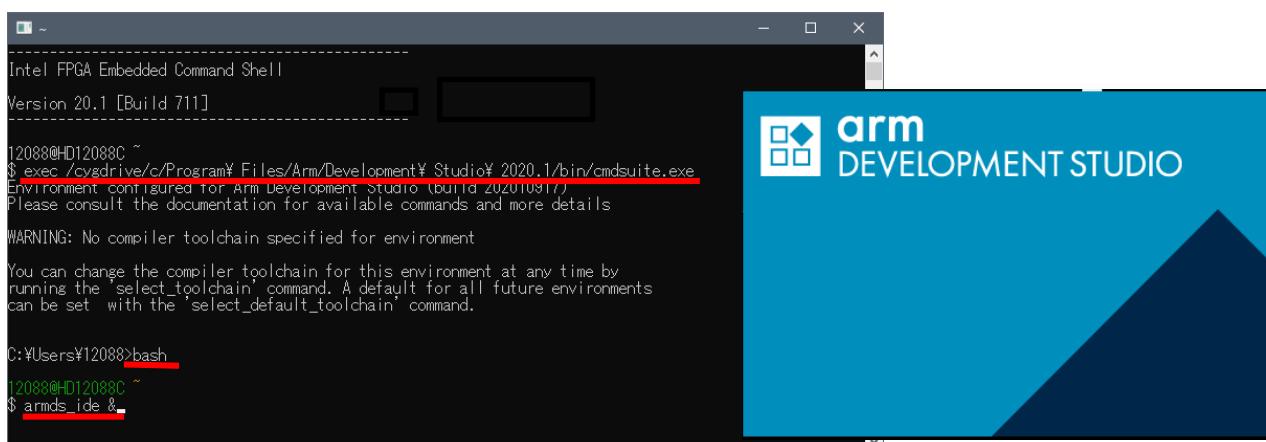

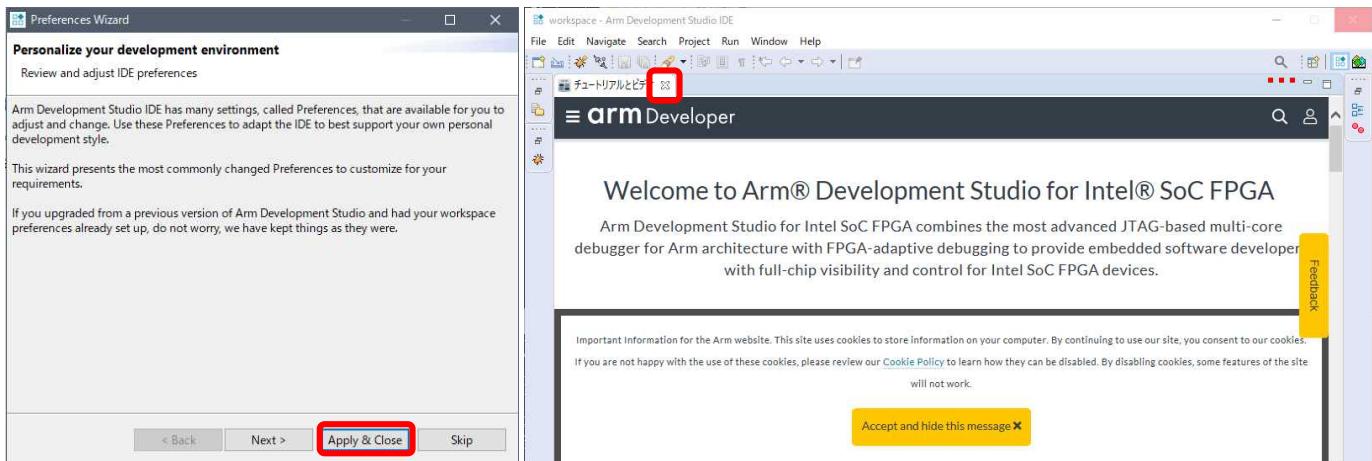

Lab 3 uses Arm® Development Studio for Intel® SoC FPGA Edition (Arm® DS below) to develop software and debug bare metal applications.

Lab 4 uses an SD card image to run Linux on the SoC device and then runs and debugs the application using Arm® DS.

**ⓘ Info:**

Lab 4 is an optional exercise that will not be available at our company SoC Startup Trial Seminar due to time constraints.

**ⓘ Info:**

Starting with version 20.1, the SoC EDS standard integrated development environment tool is Arm® Development Studio (Arm® DS). The previous product, Arm® Development Studio 5 (DS-5™), is available for pre-version 19.4 environments.

## 1-1. Requirements

The following software is used in this exercise.

- Quartus® Prime Standard Edition v20.1 (Lite Edition is also available)

You will also need to register Cyclone® V as Device Data.

Download and installation instructions are available at:

[How to Download Intel® Quartus® Prime Development Software and Questa® - Intel® FPGA Edition](#)

[How to Install Intel® Quartus® Prime Development Software and Questa® - Intel® FPGA Edition](#)

- SoC FPGA Embedded Development Suite Standard Edition v20.1 (SoC EDS)

For installation instructions, refer to the following website:

[How to install SoC FPGA Embedded Development Suite \(SoC EDS\) ver. 20.1](#)

- Exercise Data (SoC-Trial\_Seminer\_Lab\_data\_atlas\_de10nano\_v20.1\_r2.exe)

When you double-click the exercise data .exe file, it will be expanded to the following location by default:

**C:\¥lab¥soc\_lab¥cv\_soc\_lab**

This document assumes that the exercise data is expanded to the above location.

- Host PC OS: Windows® 10 Enterprise

This exercise uses Windows® 10 Enterprise (version 1803) to verify operation.

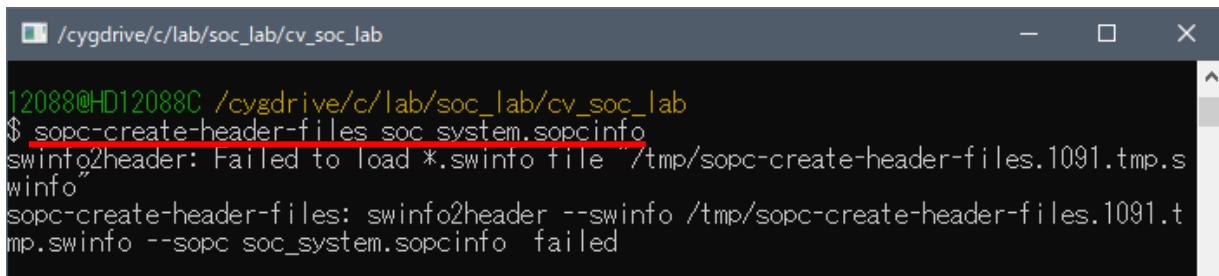

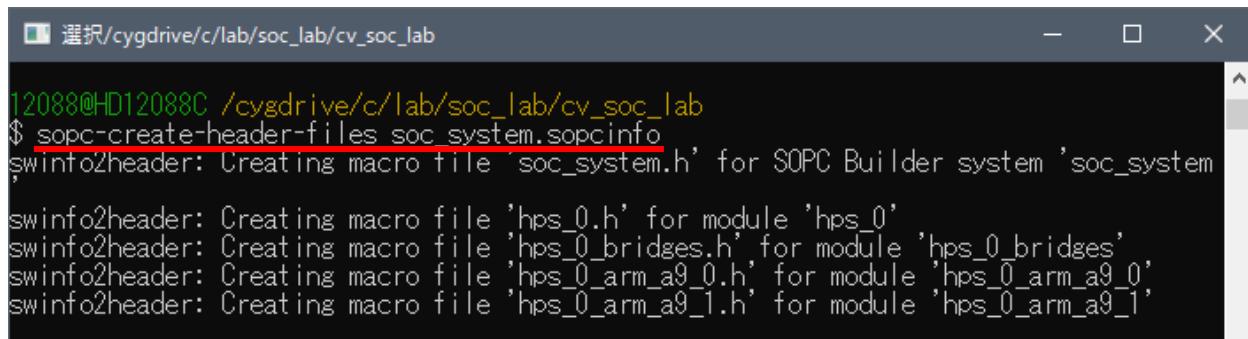

**⚠ Notes:**

When using SoC EDS v20.1std in a Windows® 10 environment, the tools **bsp-create-settings** and **sopc-create-header-files** must be resolved before running.

After setting up SoC EDS, you should also review the following reference sites:

**📄 Reference:**

Macnica Altera FPGA Insights "[Workaround for bsp-create-settings execution error in SoC EDS environment](#)"

**📄 Reference:**

Macnica Altera FPGA Insights "[Workaround for sopc-create-header-files execution error in SoC EDS environment](#)"

\* This exercise uses these two tools, so both of these should be addressed.

## 2. Board Setup

This section describes the board setup required to complete exercises 1, 2, and 3.

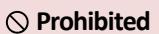

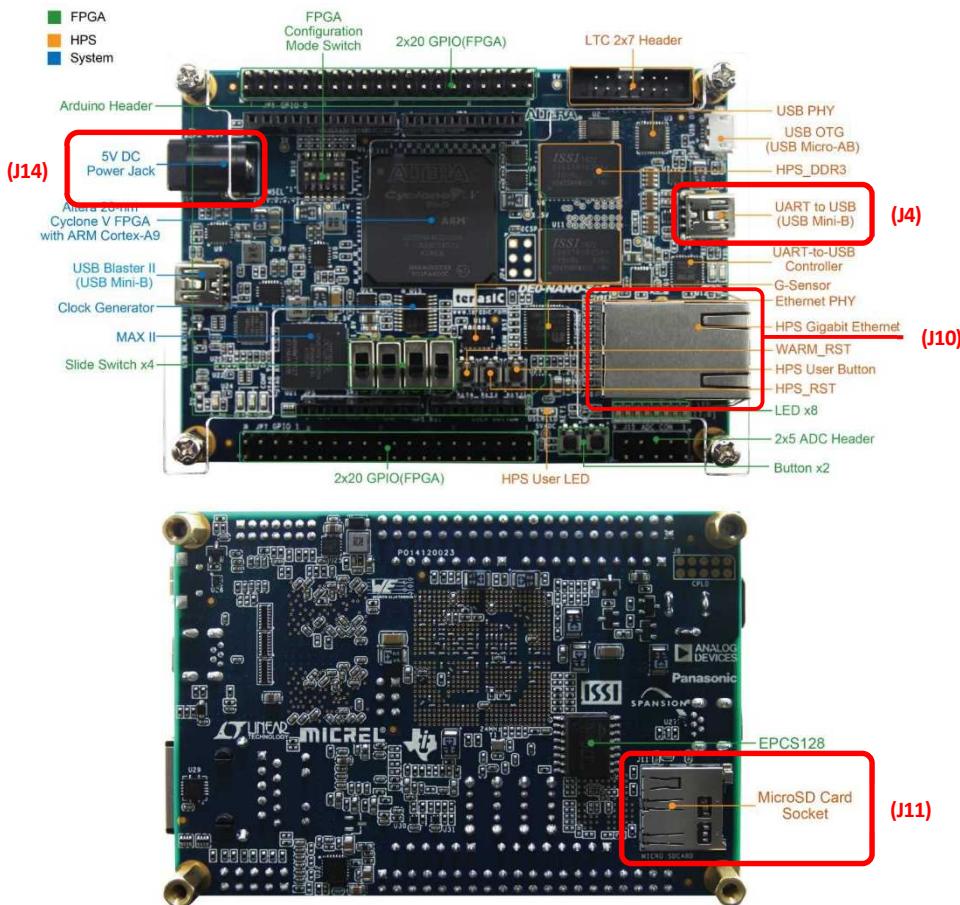

### 2-1. Board Layout

The following diagram illustrates the layout of the Atlas-SoC board used in this exercise.

The DE10 Nano board is basically the same.

Figure 2-1. Atlas-SoC board layout diagram

### 2-2. Power and cable connections

Connect the AC adaptor and cables as follows.

- Connect the power (AC adaptor) to the DC input (J14).

- Use the Mini USB cable to connect the work PC to the onboard USB-Blaster™ II connector (J13).

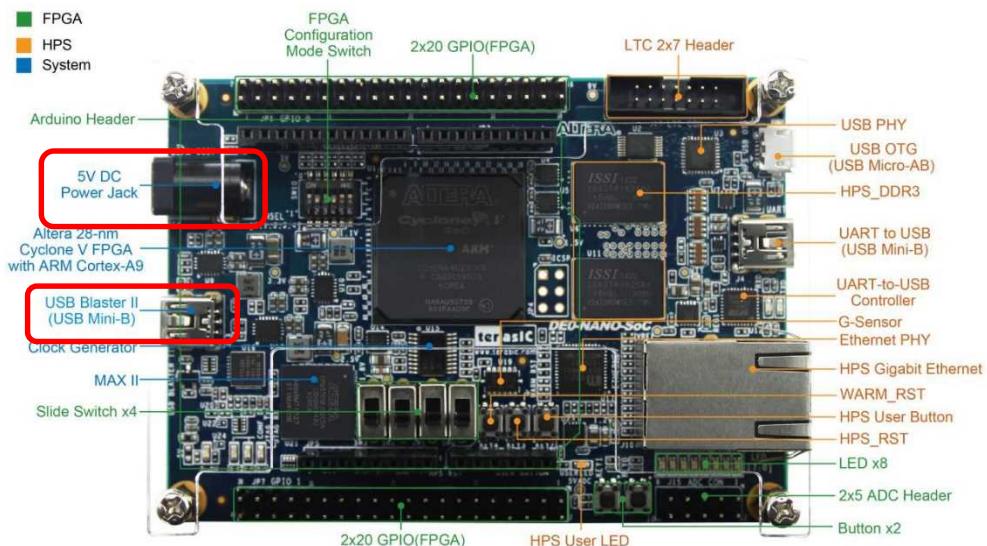

### 2-3. SW10 settings

Make sure that the SW10 (MSEL setting switch) is set as follows.

This setting puts the FPGA in FPPx32 mode.

Table 2-1. SW10 Settings

| Board Reference | Signal Name | Settings  |

|-----------------|-------------|-----------|

| SW10. 1         | MSEL0       | ON ("0")  |

| SW10. 2         | MSEL1       | OFF ("1") |

| SW10. 3         | MSEL2       | ON ("0")  |

| SW10. 4         | MSEL3       | OFF ("1") |

| SW10. 5         | MSEL4       | ON ("0")  |

| SW10. 6         | N/A         | N/A       |

Figure 2-2. Jumper settings

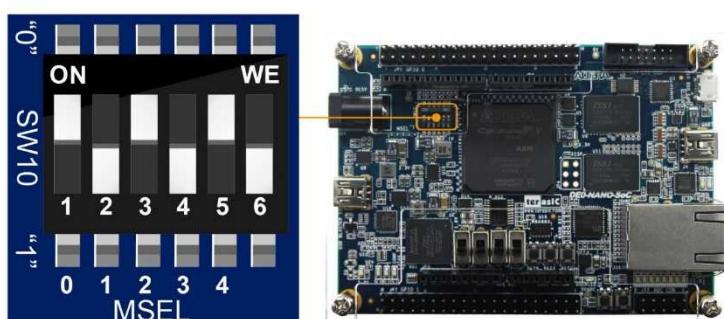

### 3. Lab 1: Hardware Exercise

In this section, you will use Quartus® Prime and Platform Designer to design the hardware including the following Arm® processors.

Altera® SoC FPGA is not limited to Cyclone® V, but uses a tool called Platform Designer included in Quartus® Prime to configure the system. Platform Designer provides a set of components that can be implemented on the FPGA side, including Hard Processor System (HPS) blocks, and allows you to optimize resources by implementing only the desired components. In addition, since the created system can be easily ported to other devices if the peripherals are supported, you can use the system itself as a design asset.

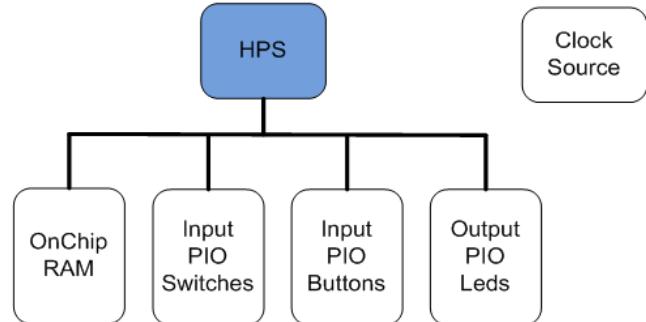

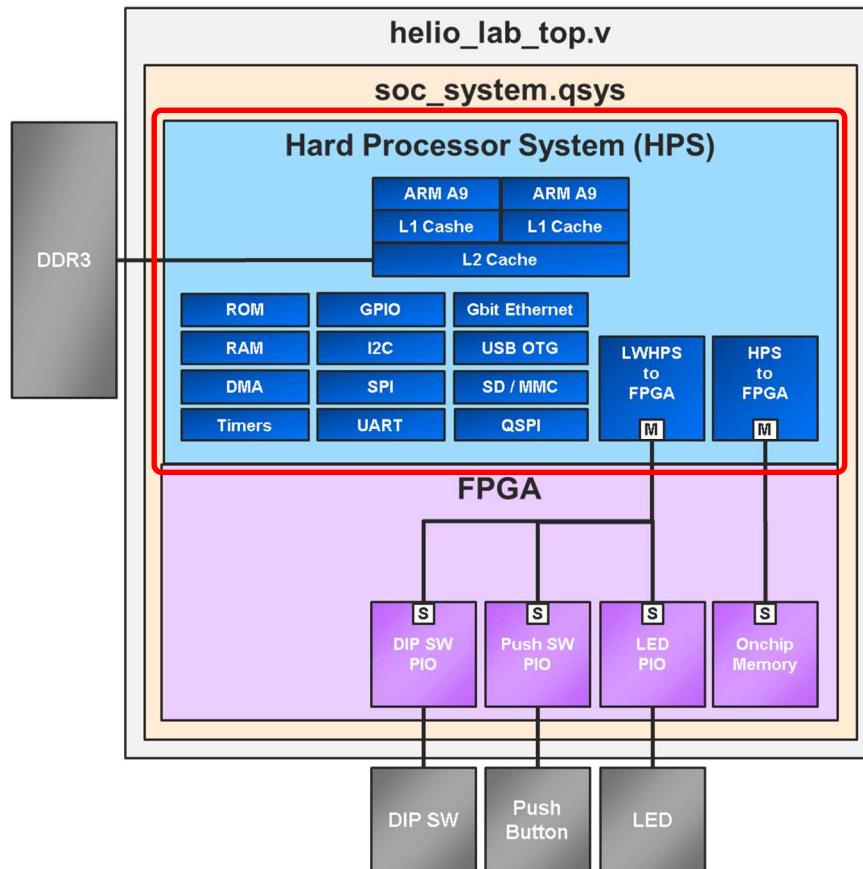

In this exercise, several components and clock source components are already implemented in the Platform Designer system to shorten the exercise time. To do this, you will add an HPS block (the blue block in the bold box) and connect the existing components. You will perform the following exercises:

Exercise:

- Add an HPS component to an existing Platform Designer system

- Configure the HPS interface and other parameters

- Connect existing components to HPS

- Generate the Platform Designer system

Figure 3-1. Block diagram of the SoC system designed in Lab 1

### 3-1. Step 1: Hardware Exercise Open the design project

As you proceed with the exercises, carefully read all the instructions in each step of this manual.

In this manual, the working directory is described as C:\lab\soc\_lab folder. If you have changed the working folder, read it again according to your environment.

Let's get started.

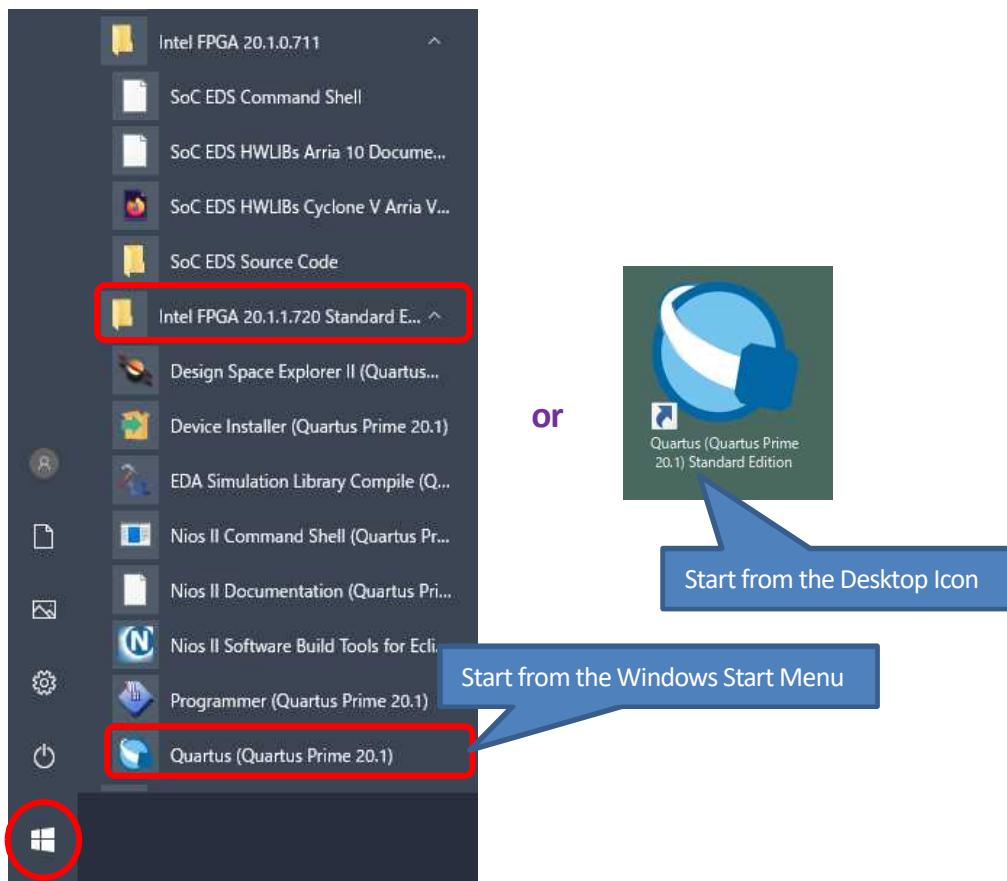

1. Start Quartus® Prime from the installed Quartus® Prime 20.1 Standard Edition (or Lite Edition) development software. If you leave the default, you can find it below.

**Windows Start => Intel FPGA 20.1.1.720 Standard Edition/Lite Edition => Quartus (Quartus Prime 20.1)**

Figure 3-2. Start Quartus® Prime

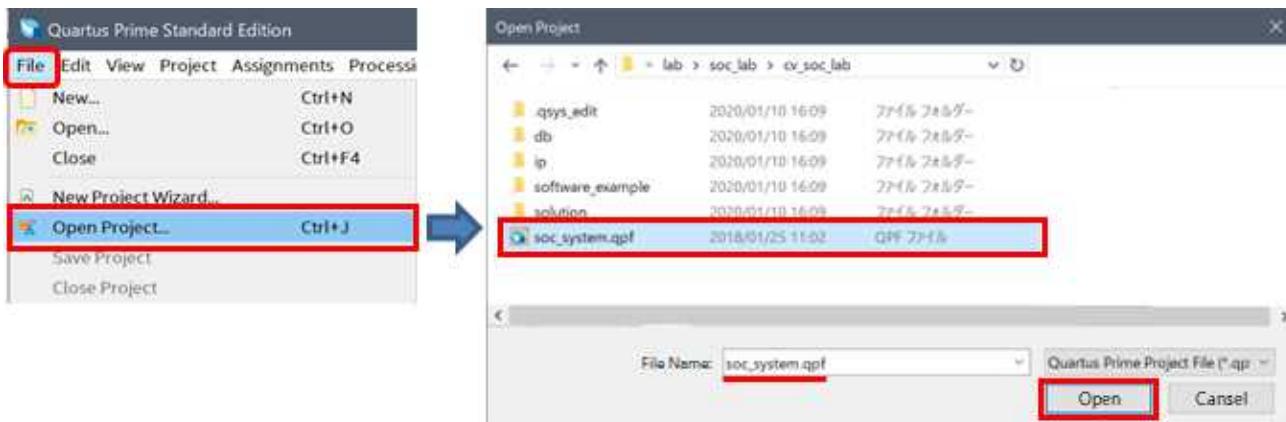

2. From the **Quartus® Prime** menu bar, select **File => Open Project** and select **soc\_system.qpf** located in **C:\lab\soc\_lab\cv\_soc\_lab**.

This qpf file is the project file in Quartus® Prime.

Figure 3-3. Opening the Quartus® Prime Project

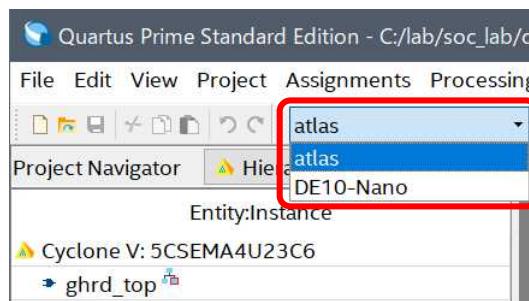

3. Select the board. Refer to the figure to set the board to be used.

- For DE0 Nano-SoC/Atlas-SoC boards: select [atlas](#)

- For DE10 Nano boards: select [DE10 Nano](#)

By making this setting, you will be able to use the pre-set information such as pin placement and device to be used for the board to be used this time.

Figure 3-4. Selecting the board to be used

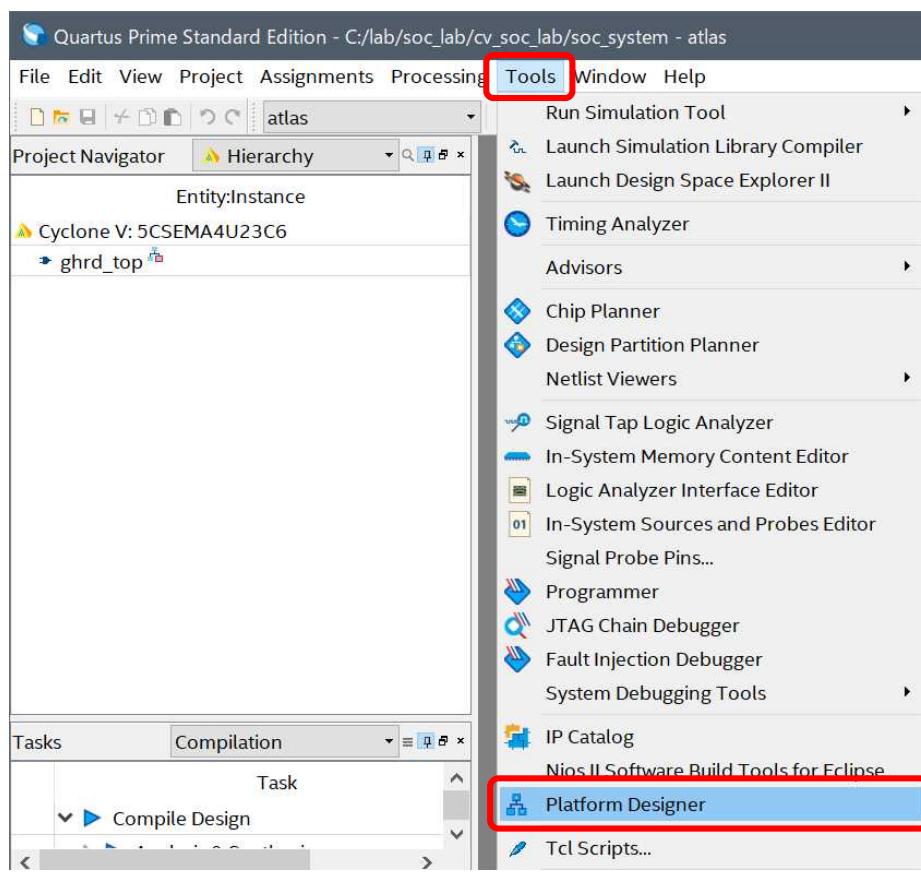

4. Launch **Platform Designer** from **Tools** in Quartus® Prime. Alternatively, click the Platform Designer icon in the toolbar to launch Platform Designer.  Click to launch Platform Designer.

Figure 3-5. Starting the Platform Designer

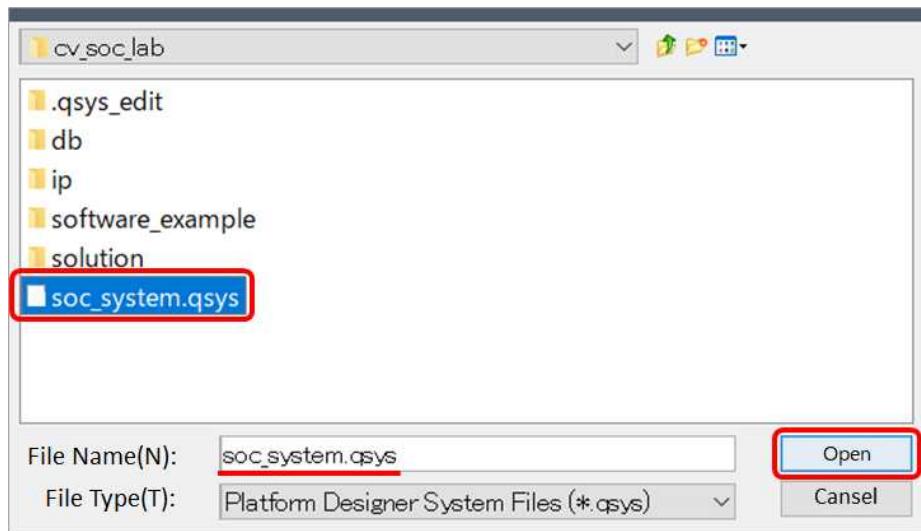

5. Open the soc\_system.qsys file.

Figure 3-6. Opening the Platform Designer File

Let's first briefly explain how to use Platform Designer.

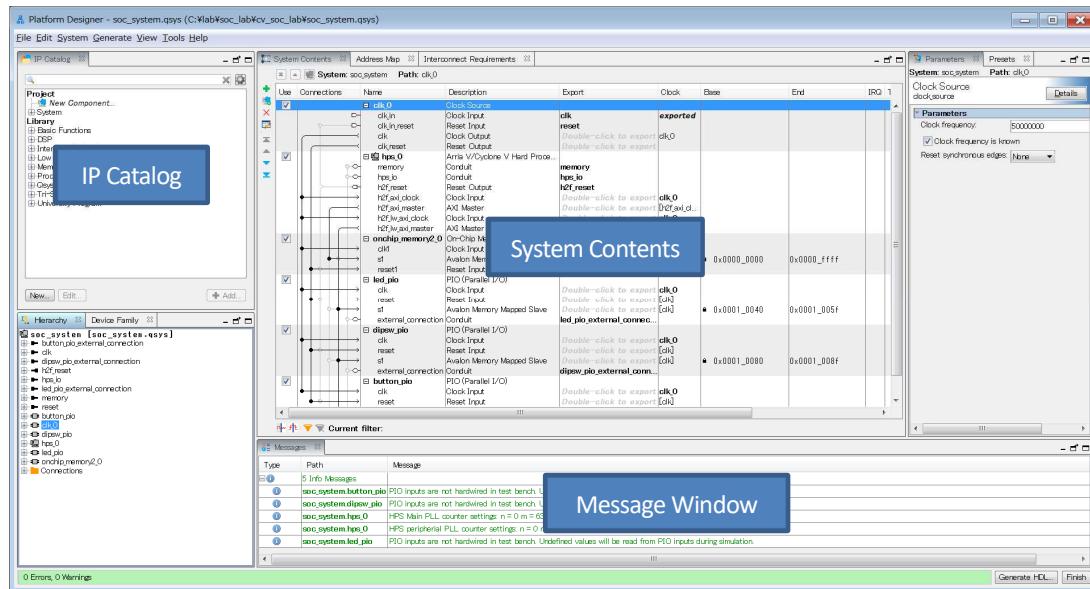

There are 3 main screens in Platform Designer: IP Catalog, System Contents, and Message Window.

The IP Catalog contains components that can be used by Platform Designer. You add the components you want to implement to System Contents. You then connect the components in System Contents to create a system.

The hard macroized part of the chip called HPS is also available as a software component in IP Catalog. By implementing this component in the Platform Designer system, you can use it on the HPS side of SoC devices.

Figure 3-7. Platform Designer Screen

The following components (white) have been installed in the opened Platform Designer system. Add and configure the HPS block (blue) for this system, and connect the installed components.

■ Implemented component (white):

- Clock source

- On-chip memory

- PIO peripheral for LED/Button control

- DIP switch PIO

- Button PIO

- LED PIO

■ Components to be added in the exercise (blue):

- HPS

Platform Designer provides a setting screen for each IP. Double-click a component in System Contents to open the setting screen for that component.

Figure 3-8. Platform Designer system to be designed

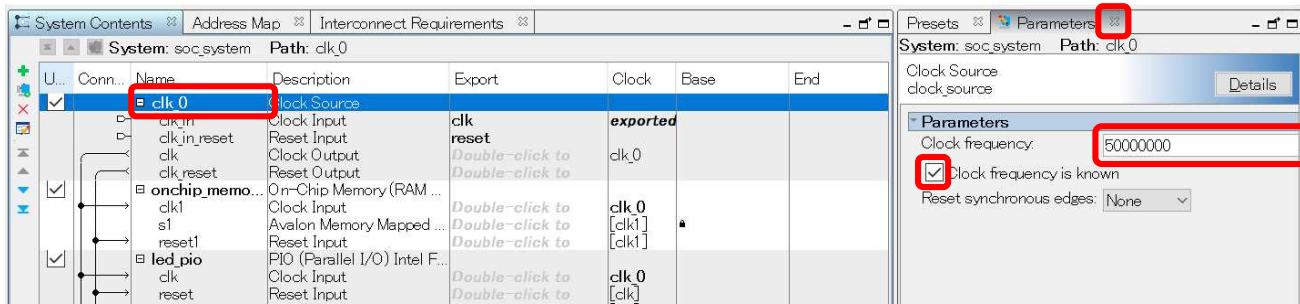

6. Double-click the Clock Source component (clk\_0) and make sure that the **Clock Frequency** is set to 50 MHz to match the oscillator on the development board.

7. Make sure that **Clock frequency is known** is checked.

Figure 3-9. Checking the Clock Source

8. Click **Close (X)** on the Parameters tab to close the **Parameters** tab.

The settings of each Platform Designer component are retained when you close the **Parameters** tab, unless you close Platform Designer.

### 3-2. Step 2: Adding HPS Components

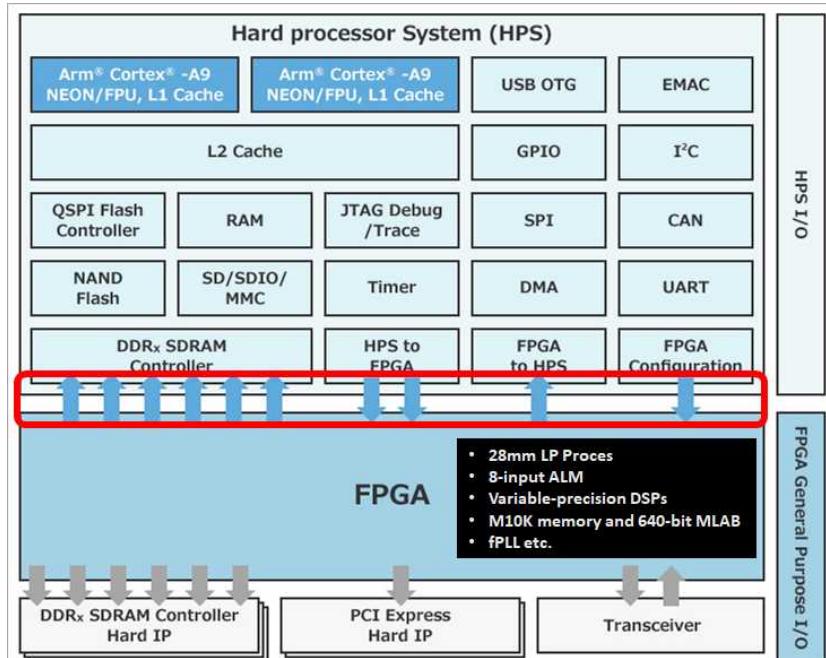

The HPS consists of Dual-core Arm® Cortex™-A9 MP Core processors and various peripherals. As shown below, the Altera® SoC FPGA consists of two main blocks: the HPS block and the FPGA block.

In this step, you add and configure the HPS block in the Platform Designer system. You can configure the HPS block in the HPS block in the Platform Designer system.

The GUI used to configure the HPS provides multiple tabs (FPGA interfaces, Peripheral Pins, HPS Clocks, SDRAM), and you can configure settings for each of them.

Figure 3-10. HPS Block Added to the Platform Designer System

From the next page, add an HPS block to the Platform Designer system and make various settings.

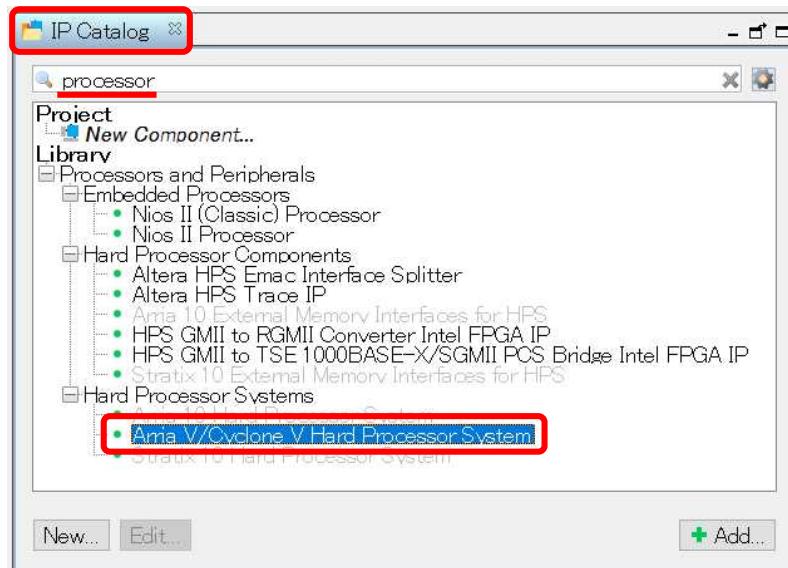

1. In the search box under the **IP Catalog** tab, enter **processor**.

Figure 3-11. IP Catalog Search Box

2. Double-click **Arria V/Cyclone V Hard Processor System**.

This component is the block for configuring HPS components. The dialog box for the HPS component to be configured appears. This window opens as a separate window only the first time. After clicking the **Finish** button, if you want to redisplay it the second time or later, double-click the HPS component from the **System Contents** tab.

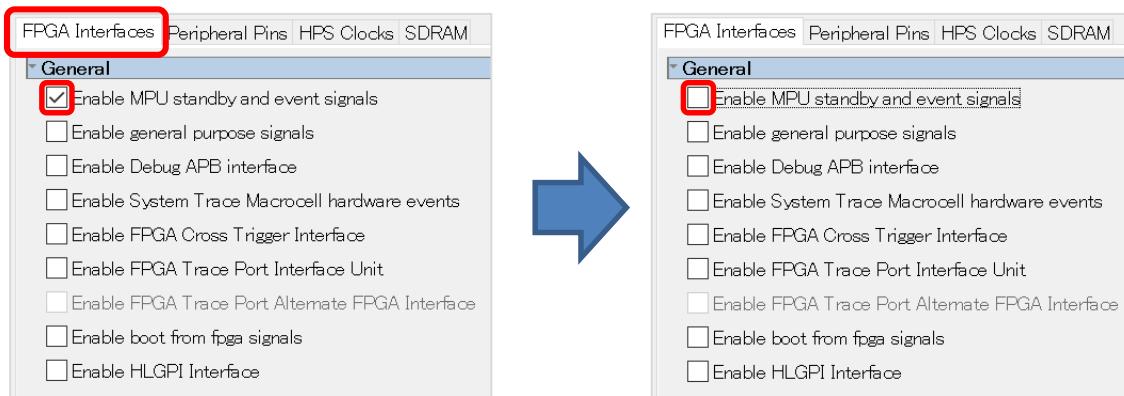

The **FPGA Interfaces** tab allows you to specify whether to use signals between the HPS and the FPGA connected inside the device. Depending on the settings, the status of the HPS side can be notified to the FPGA, or the FPGA side can control the HPS side.

Figure 3-12. Internal bus between the HPS peripheral and the FPGA

3. Click the **FPGA Interfaces** tab to disable **Enable MPU standby and event signals**, which are enabled by default.

Figure 3-13. FPGA Interface tab settings

**① Info:**

This is an internal signal that indicates whether the microprocessor is in standby mode or the CPU can wake up. You can connect this input signal to logic high for permanent effect, or as a processor event.

4. Make sure **Enable HLGPI Interface** is unchecked and disabled (default).

**① Info:**

This is an option to use an unused pin (14bit) on the SDRAM interface as a general-purpose input only pin. This signal is not required for this exercise.

Next, configure the bridge between the HPS and the FPGA.

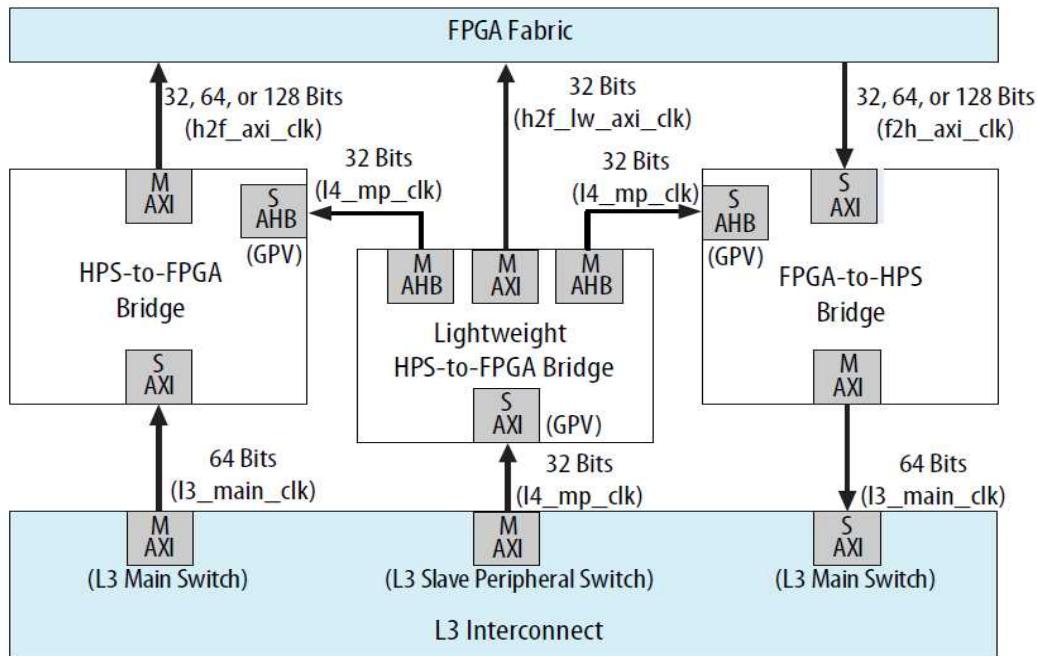

There are ports between the HPS and the FPGA that are master and slave respectively. There are two ports from the HPS to the FPGA and one port from the FPGA to the HPS. The two ports from the HPS to the FPGA are HPS-to-FPGA interface and lightweight HPS-to-FPGA interface respectively. The one port from the FPGA to the HPS is FPGA-to-HPS. For all ports, you can set the bus width and use or not use the port according to the path to be accessed.

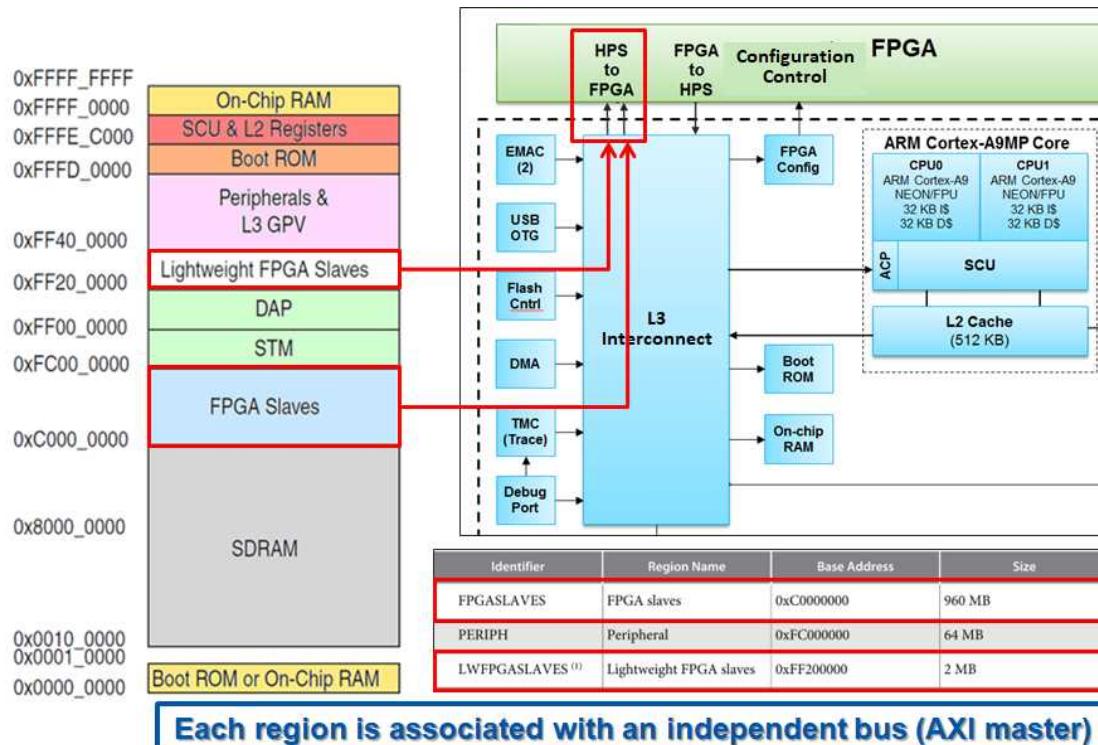

When accessing from the Arm® processor or the Master on the HPS side, you can access by specifying the address of "Bridge address + FPGA component offset address." The bridge address is as shown in the following figure.

**HPS-to-FPGA interface is 0xC000\_0000**

**Lightweight HPS-to-FPGA interface is 0xFF20\_0000**

Figure 3-14. HPS and FPGA internal bus and address map viewed from Arm

#### Reference:

For more information on the HPS to FPGA interface, please refer to the Macnica website technical information.

See also.

[Beginner's Guide to SoC - How to access between HPS-FPGA \(Cyclone® V SoC/Arria® V SoC\)](#)

Make the settings on the following page.

5. In the **AXI Bridges** section, set the **FPGA-to-HPS interface width** to **Unused**, the **HPS-to-FPGA interface width** to **64 bit**, and the **Lightweight HPS-to-FPGA interface width** to **32 bit**.

Figure 3-15. Configuring AXI Bridges

**① Info:**

Enabling FPGA-to-HPS interfaces allows the master in the FPGA to access the peripheral of the HPS. This exercise does not use it.

When HPS-to-FPGA interface is enabled, HPS becomes the master and can access the peripheral of the FPGA. HPS-to-FPGA interfaces can be 32/64/128 bit wide, but for this exercise we will use the middle 64bit width.

6. Scroll down the **FPGA interface** page to find more options, including **FPGA-to-HPS SDRAM interface**, **Resets** and **DMA Peripheral Request** sections.

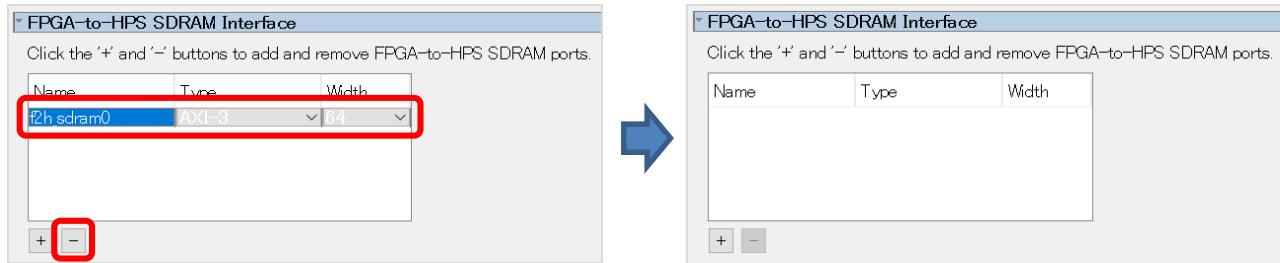

7. Scroll through the **FPGA interface** window until you see **FPGA to HPS SDRAM Interface**.

8. Click on the **F2h\_sdram0** interface and delete the interface by clicking the **-** button.

This is a broadband port that allows direct access from the FPGA to the SDRAM on the HPS side. It does not involve an interconnect and ACP (Accelerator Coherency Port) for fast access. On the other hand, data coherency is up to the user.

This is not going to be used, so I will delete the port.

Figure 3-16. FPGA-to-HPS SDRAM Interface Configuration

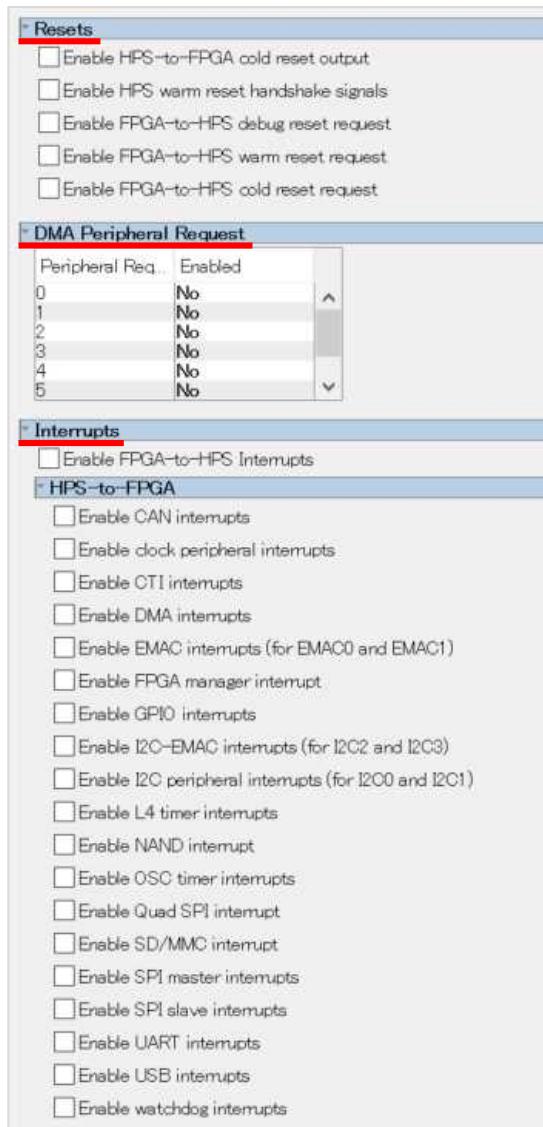

\_\_\_ 9. Scroll down to the **Resets** section.

\_\_\_ 10. In the **Resets** section, make sure all options for HPS reset are **disabled**.

\_\_\_ 11. In the **DMA Peripheral Request** section, make sure all lines under the **Enabled** column display **No**.

**ⓘ Info:**

Enabling DMA peripheral request allows the HPS DMA controller's Peripheral Request signal to be connected to the FPGA fabric.

Normally, this should be set to No, unless you are using the Peripheral Request signal for DMA transfer.

\_\_\_ 12. In the **Interrupts** section, make sure the **Enable FPGA-to-HPS interrupts** option is **disabled**.

In this case, the component implemented in the FPGA will not interrupt the Arm® processor.

The Resets/DMA/Interrupts settings are as follows (no changes from the default):

Figure 3-17. Resets/DMA/Interrupts Settings

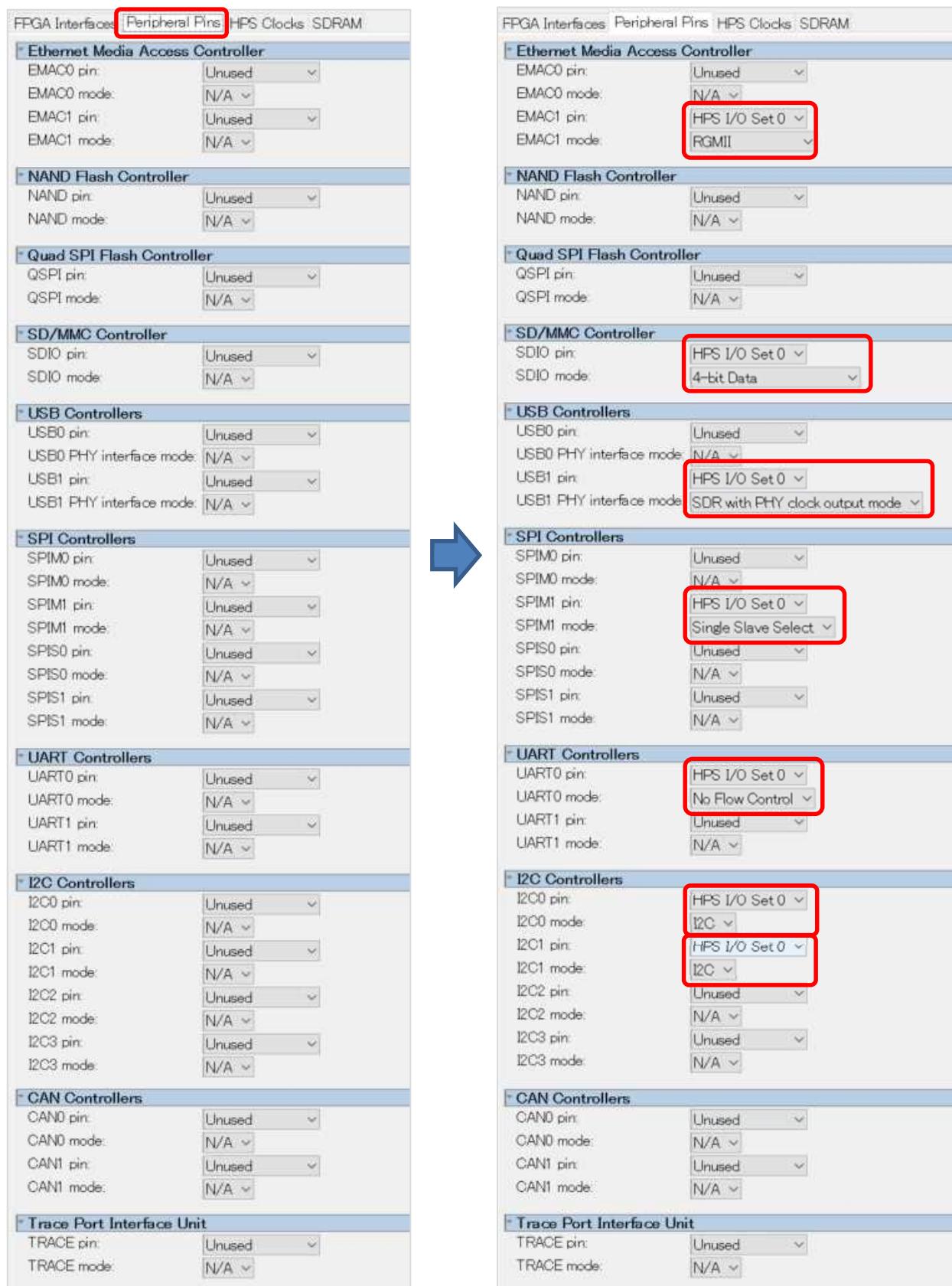

## 3-3. Step 3: HPS Peripheral Settings (MAC, UART, I2C, SDIO, USB)

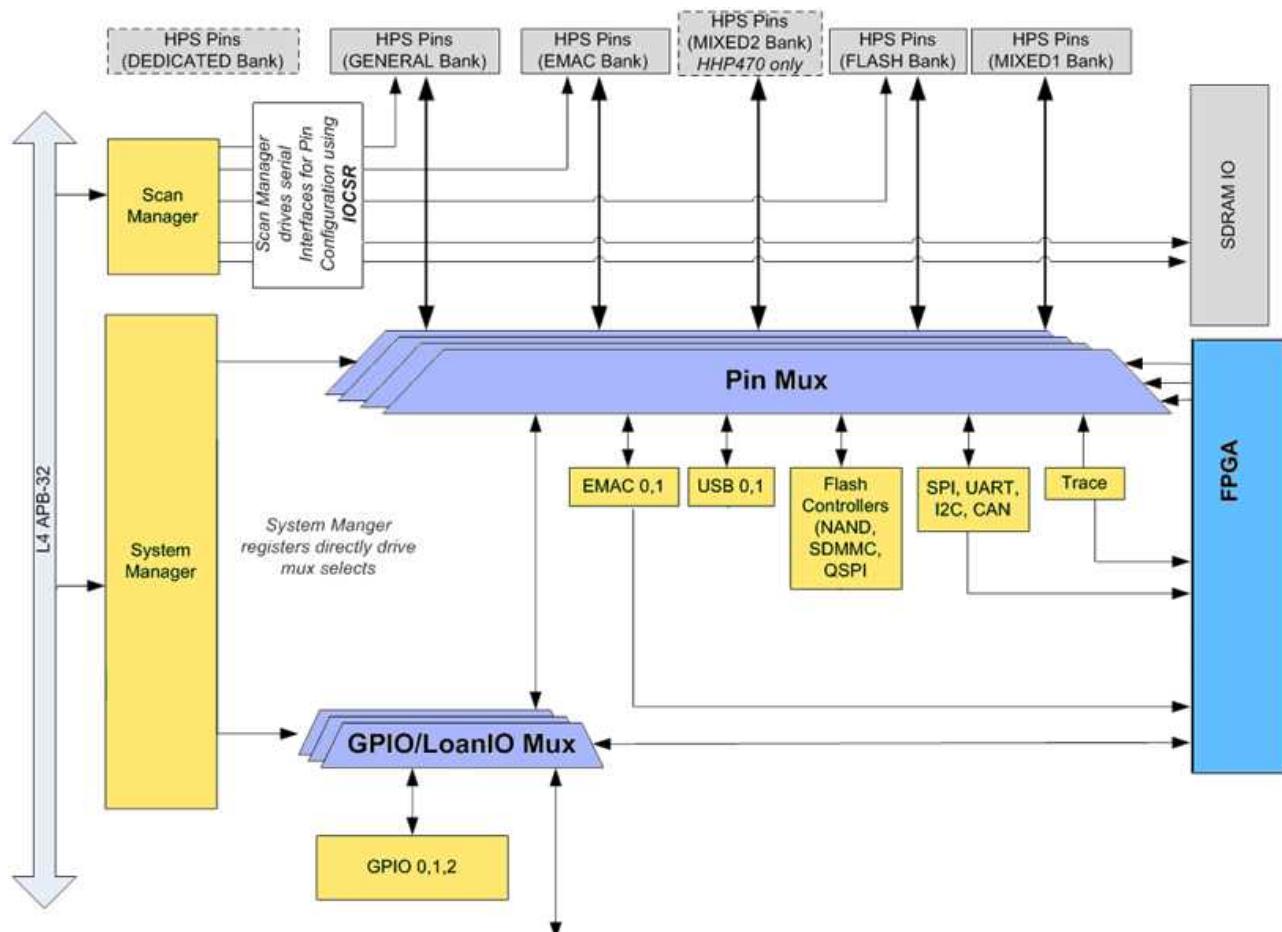

The **Peripheral Pins** tab enables HPS peripherals that are hardcoded inside HPS.

Many HPS pins are shared by up to 4 peripherals. However, only 1 peripheral can be used. Therefore, pin assignments must be specified so that the peripherals to be enabled do not conflict. Pin assignments can be selected from up to 3 different parameters (HPS I/O Set 0 ~ 3).

Figure 3-18. HPS I/O Pin Multiplexer

- \_\_\_\_\_ 1. Select the **Peripheral Pins** tab.

- \_\_\_\_\_ 2. Set the **EMAC1 pin** of the **Ethernet Media Access Controller** to **HPS I/O Set 0**.

- \_\_\_\_\_ 3. Set the **EMAC1 mode** of the **Ethernet Media Access Controller** to **RGMII**.

- \_\_\_\_\_ 4. Set the **SDIO pin** of the **SD/MMC Controller** to **HPS I/O Set 0**.

- \_\_\_\_\_ 5. Set the **SDIO mode** of the **SD/MMC Controller** to **4-bit Data**.

- \_\_\_\_\_ 6. Set the **USB1 pin** of the **USB Controllers** to **HPS I/O Set 0**.

- \_\_\_\_\_ 7. Set the **USB1 PHY interface mode** of the **USB Controllers** to **SDR with PHY clock output mode**.

- \_\_\_\_\_ 8. Set the **SPIM1 pin** of the **SPI Controllers** to **HPS I/O Set 0**.

- \_\_\_\_\_ 9. Set **SPIM1 mode** of **SPI controllers** to **Single Slave Select**.

- \_\_\_\_\_ 10. Set **UART0 pin** of **UART controllers** to **HPS I/O Set 0**.

- \_\_\_\_\_ 11. Set **UART0 mode** of **UART controllers** to **No Flow Control**.

- \_\_\_\_\_ 12. Set **I2C pin** of **I2C controllers** to **HPS I/O Set 0**.

- \_\_\_\_\_ 13. Set **I2C0 mode of I2C controllers** to **I2C**.

- \_\_\_\_\_ 14. Set **I2C1 pin** of **I2C controllers** to **HPS I/O Set 0**.

- \_\_\_\_\_ 15. Set **I2C1 mode of I2C controllers** to **I2C**.

Refer to the next page for the parameters after setting.

Figure 3-19. Configuring HPS Peripherals

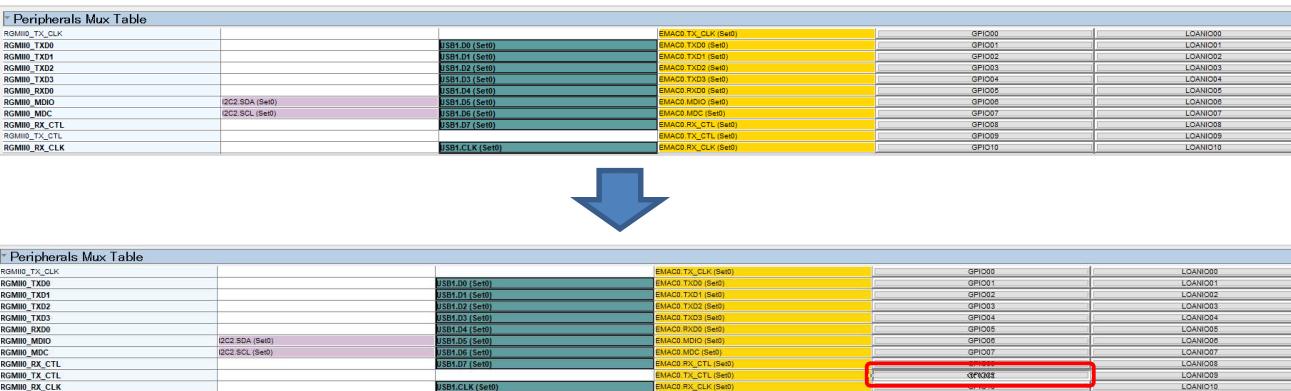

In the **Peripherals Mux Table** section, you can see the placement of the pins you set up.

A pin can only have one role. Therefore, multiple HPS peripherals cannot use the same pin, and the same pin cannot have the role of HPS Peripheral and GPIO. Therefore, use this **Peripherals Mux Table** section to see what each pin is used for.

The left column shows the pin name, and if the pin is used, it is bolded. Pins that are not used as peripheral pins can be used as HPS GPIO pins. In this case, you can activate them by pressing the respective GPIO button for each pin.

If there is a conflict for a pin, an **Error** is displayed in the **Message Window** and the pin field is highlighted in red so that you can see in real time which pin is causing the conflict.

Let's set the pins that are not used as GPIO pins.

16. Enable GPIO09 by clicking **GPIO09** in the **Peripherals Mux Table** section.

④ Point:

The response may take a while, so be careful not to press it too many times.

| Pin Name      | Pin Description | Peripheral      | GPIO Pin            | LoANIO Pin |          |

|---------------|-----------------|-----------------|---------------------|------------|----------|

| RGMMIO_TX_Clk |                 |                 |                     |            |          |

| RGMMIO_TXD0   |                 | USB1.00 (Set0)  | EMAC0 TXD0 (Set0)   | GPIO00     | LoANIO00 |

| RGMMIO_TXD1   |                 | USB1.01 (Set0)  | EMAC0 TXD1 (Set0)   | GPIO01     | LoANIO01 |

| RGMMIO_TXD2   |                 | USB1.02 (Set0)  | EMAC0 TXD2 (Set0)   | GPIO02     | LoANIO02 |

| RGMMIO_TXD3   |                 | USB1.03 (Set0)  | EMAC0 TXD3 (Set0)   | GPIO03     | LoANIO03 |

| RGMMIO_RXD0   |                 | USB1.04 (Set0)  | EMAC0 RXD0 (Set0)   | GPIO04     | LoANIO04 |

| RGMMIO_MDC    | Q22 SDA (Set0)  | USB1.05 (Set0)  | EMAC0 MDC (Set0)    | GPIO05     | LoANIO05 |

| RGMMIO_MDO    | Q22 SCL (Set0)  | USB1.06 (Set0)  | EMAC0 MDO (Set0)    | GPIO06     | LoANIO06 |

| RGMMIO_RX_CTL |                 | USB1.07 (Set0)  | EMAC0 RX_CTL (Set0) | GPIO07     | LoANIO07 |

| RGMMIO_TX_CTL |                 | USB1.08 (Set0)  | EMAC0 TX_CTL (Set0) | GPIO08     | LoANIO08 |

| RGMMIO_RX_CLK |                 | USB1.CLK (Set0) | EMAC0 RX_CLK (Set0) | GPIO09     | LoANIO09 |

|               |                 |                 | EMAC0 TX_CLK (Set0) | GPIO10     | LoANIO10 |

| Pin Name      | Pin Description | Peripheral      | GPIO Pin            | LoANIO Pin |          |

|---------------|-----------------|-----------------|---------------------|------------|----------|

| RGMMIO_TX_Clk |                 |                 |                     |            |          |

| RGMMIO_TXD0   |                 | USB1.00 (Set0)  | EMAC0 TXD0 (Set0)   | GPIO00     | LoANIO00 |

| RGMMIO_TXD1   |                 | USB1.01 (Set0)  | EMAC0 TXD1 (Set0)   | GPIO01     | LoANIO01 |

| RGMMIO_TXD2   |                 | USB1.02 (Set0)  | EMAC0 TXD2 (Set0)   | GPIO02     | LoANIO02 |

| RGMMIO_TXD3   |                 | USB1.03 (Set0)  | EMAC0 TXD3 (Set0)   | GPIO03     | LoANIO03 |

| RGMMIO_RXD0   |                 | USB1.04 (Set0)  | EMAC0 RXD0 (Set0)   | GPIO04     | LoANIO04 |

| RGMMIO_MDC    | Q22 SDA (Set0)  | USB1.05 (Set0)  | EMAC0 MDC (Set0)    | GPIO05     | LoANIO05 |

| RGMMIO_MDO    | Q22 SCL (Set0)  | USB1.06 (Set0)  | EMAC0 MDO (Set0)    | GPIO06     | LoANIO06 |

| RGMMIO_RX_CTL |                 | USB1.07 (Set0)  | EMAC0 RX_CTL (Set0) | GPIO07     | LoANIO07 |

| RGMMIO_TX_CTL |                 | USB1.08 (Set0)  | EMAC0 TX_CTL (Set0) | GPIO08     | LoANIO08 |

| RGMMIO_RX_CLK |                 | USB1.CLK (Set0) | EMAC0 RX_CLK (Set0) | GPIO09     | LoANIO09 |

|               |                 |                 | EMAC0 TX_CLK (Set0) | GPIO10     | LoANIO10 |

Figure 3-20. HPS GPIO09 settings

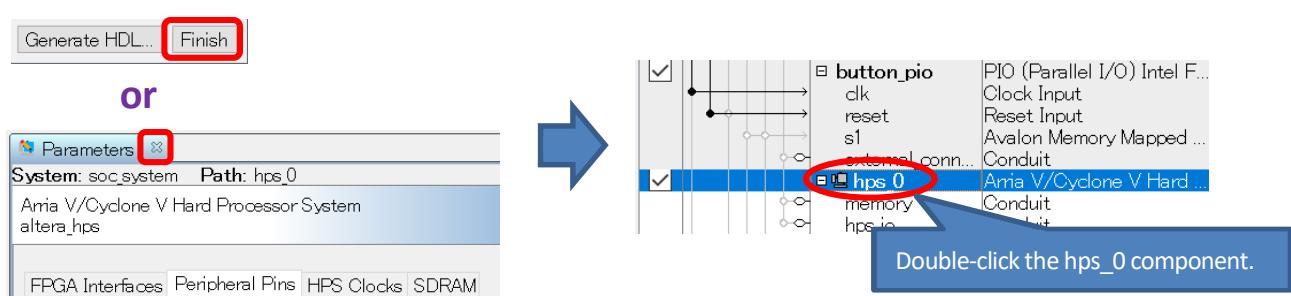

④ Point:

If you cannot click it, select **[Finish]** in the lower right corner of the HPS component dialog box, or click "x" in the Parameters tab to close the HPS component dialog box.

Double-click the **hps\_0** component again to open the parameters window and continue working.

Figure 3-21. What to do if you cannot click during GPIO settings

17. Similarly, enable **GPIO35**, **GPIO40**, **GPIO53**, **GPIO54**, and **GPIO61**.

|                |                  |  |                          |                 |                 |

|----------------|------------------|--|--------------------------|-----------------|-----------------|

| DBIPL_CLK      |                  |  | DBIPL_CLK (Set0) (Set0)  | GPIO34          | LOANIO24        |

| SDPFI_S5A      |                  |  | SDIO_S5A (Set0) (Set0)   | GPIO35          | LOANIO25        |

| SDMMC_CMD      |                  |  | SDIO_PVREN (Set0) (Set0) | GPIO37          | LOANIO37        |

| SDMMC_PVREN    |                  |  | SDIO_D1 (Set0) (Set0)    | GPIO38          | LOANIO38        |

| SDMMC_D0       |                  |  | SDIO_D0 (Set0) (Set0)    | GPIO39          | LOANIO39        |

| SDMMC_D1       |                  |  | SDIO_D2 (Set0) (Set0)    | GPIO40          | LOANIO40        |

| SDMMC_D4       |                  |  | SDIO_D3 (Set0) (Set0)    | GPIO41          | LOANIO41        |

| SDMMC_D5       |                  |  | SDIO_D4 (Set0) (Set0)    | GPIO42          | LOANIO42        |

| SDMMC_D6       |                  |  | SDIO_D5 (Set0) (Set0)    | GPIO43          | LOANIO43        |

| SDMMC_D7       |                  |  | SDIO_D7 (Set0) (Set0)    | GPIO44          | LOANIO44        |

| HPS_GPIO44     |                  |  | SDIO_MTX (Set0) (Set0)   | GPIO45          | LOANIO45        |

| SDMMC_CCLK_OUT |                  |  | SDIO_D0 (Set0) (Set0)    | GPIO46          | LOANIO46        |

| SDMMC_D3       |                  |  | SDIO_D1 (Set0) (Set0)    | GPIO47          | LOANIO47        |

| TRACE_CLK      |                  |  | TRACE_CLK (Set0) (Set0)  | GPIO48          | LOANIO48        |

| TRACE_D0       | MART0_RX (Set0)  |  | SPIS0_CLK (Set0) (Set0)  | TRACE_D0 (Set0) | GPIO49          |

| TRACE_D1       | MART0_TX (Set0)  |  | SPIS0_MOSI (Set0) (Set0) | TRACE_D1 (Set0) | GPIO50          |

| TRACE_D2       | ZC1_SDA (Set0)   |  | SPIS0_MISO (Set0) (Set0) | TRACE_D2 (Set0) | GPIO51          |

| TRACE_D3       | ZC1_SCL (Set0)   |  | SPIS0_SS0 (Set0) (Set0)  | TRACE_D3 (Set0) | GPIO52          |

| TRACE_D4       | CAN1_RX (Set0)   |  | SPIS1_CLK (Set0) (Set0)  | TRACE_D4 (Set0) | GPIO53          |

| TRACE_D5       | CAN1_TX (Set0)   |  | SPIS1_MOSI (Set0) (Set0) | TRACE_D5 (Set0) | GPIO54          |

| TRACE_D6       | ZC0_SDA (Set0)   |  | SPIS1_MISO (Set0) (Set0) | TRACE_D6 (Set0) | GPIO55          |

| TRACE_D7       | ZC0_SCL (Set0)   |  | SPIS1_SS0 (Set0) (Set0)  | TRACE_D7 (Set0) | GPIO56          |

| SDPFI_CLK      |                  |  | UART0_RX (Set0) (Set0)   | UART0_RX (Set0) | GPIO57          |

| SPIM0_MISO     |                  |  | UART0_TX (Set0) (Set0)   | UART0_TX (Set0) | GPIO58          |

| SPIM0_MISO     |                  |  | UART1_RX (Set0) (Set0)   | UART1_RX (Set0) | GPIO59          |

| SPIM0_SS0      |                  |  | UART1_TX (Set0) (Set0)   | UART1_TX (Set0) | GPIO60          |

| UART0_RX       | SPIM0_SS1 (Set0) |  | CAN0_RX (Set0) (Set0)    | CAN0_RX (Set0)  | UART0_RX (Set0) |

| UART0_TX       | SPIM1_SS1 (Set0) |  | CAN0_TX (Set0) (Set0)    | CAN0_TX (Set0)  | UART0_TX (Set0) |

Figure 3-22. HPS GPIO settings

## 18. After configuring, make sure that there are no errors other than the two errors shown below (these two errors will be resolved later).

| Type                        | Path | Message                                                                                                                       |

|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------------|

| 2 Errors                    |      |                                                                                                                               |

| soc_system.hps_0            |      | hps_0.h2f_axi_clock must be connected to a clock output                                                                       |

| soc_system.hps_0            |      | hps_0.h2f_lw_axi_clock must be connected to a clock output                                                                    |

| 7 Warnings                  |      |                                                                                                                               |

| soc_system.hps_0            |      | "Configuration/HPS-to-FPGA user 0 clock frequency" (desired_cfg_clk_mhz) requested 100.0 MHz, but only achieved 97.368421 MHz |

| soc_system.hps_0            |      | 1 or more output clock frequencies cannot be achieved precisely, consider revising desired output clock frequencies.          |

| soc_system.hps_0            |      | ODT is disabled. Enabling ODT (Mode Register 1) may improve signal integrity                                                  |

| soc_system.button_pio       |      | button_pio.s1 must be connected to an Avalon-MM master                                                                        |

| soc_system.dipsw_pio        |      | dipsw_pio.s1 must be connected to an Avalon-MM master                                                                         |

| soc_system.led_pio          |      | led_pio.s1 must be connected to an Avalon-MM master                                                                           |

| soc_system.onchip_memory2.0 |      | onchip_memory2.0.s1 must be connected to an Avalon-MM master                                                                  |

| 5 Info Messages             |      |                                                                                                                               |

| soc_system.button_pio       |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

| soc_system.dipsw_pio        |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

| soc_system.hps_0            |      | HPS Main PLL counter settings: n = 0 m = 3                                                                                    |

| soc_system.hps_0            |      | HPS peripheral PLL counter settings: n = 0 m = 39                                                                             |

| soc_system.led_pio          |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

Figure 3-23. Example of display when there is no pin conflict error

For example, if the error shown in [Figure 3-24](#). appears, there is a conflict between the pins of **SPISO** and **UART0**. Check whether there is an error in the setting and correct it.

In this example, an error occurs because **SPISO**, which should not be used, is to be used. If the setting is **Unused**, the error disappears.

|                                |                                                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------|

| System: soc_system Path: hps_0 | Amiga V/Cyclone V Hard Processor System<br>altera_hps                                                          |

| <b>SPI Controllers</b>         |                                                                                                                |

| SPIM0 pin:                     | Unused                                                                                                         |

| SPIM0 mode:                    | N/A                                                                                                            |

| SPIM1 pin:                     | HPS I/O Set 0                                                                                                  |

| SPIM1 mode:                    | Single Slave Select                                                                                            |

| SPISO pin:                     | HPS I/O Set 0                                                                                                  |

| SPISO mode:                    | SPI                                                                                                            |

| SPIS1 pin:                     | Unused                                                                                                         |

| SPIS1 mode:                    | N/A                                                                                                            |

| <b>UART Controllers</b>        |                                                                                                                |

| UART0 pin:                     | HPS I/O Set 0                                                                                                  |

| UART0 mode:                    | No Flow Control                                                                                                |

| UART1 pin:                     | Unused                                                                                                         |

| UART1 mode:                    | N/A                                                                                                            |

| <b>Messages</b>                |                                                                                                                |

| Type                           | Path                                                                                                           |

| 3 Errors                       |                                                                                                                |

| soc_system.hps_0               | Refer to the Peripherals Mux Table for more details. The selected peripherals SPISO and UART0 are conflicting. |

| soc_system.hps_0               | hps_0.h2f_axi_clock must be connected to a clock output                                                        |

| soc_system.hps_0               | hps_0.h2f_lw_axi_clock must be connected to a clock output                                                     |

Figure 3-24. Example of display with a pin conflict error

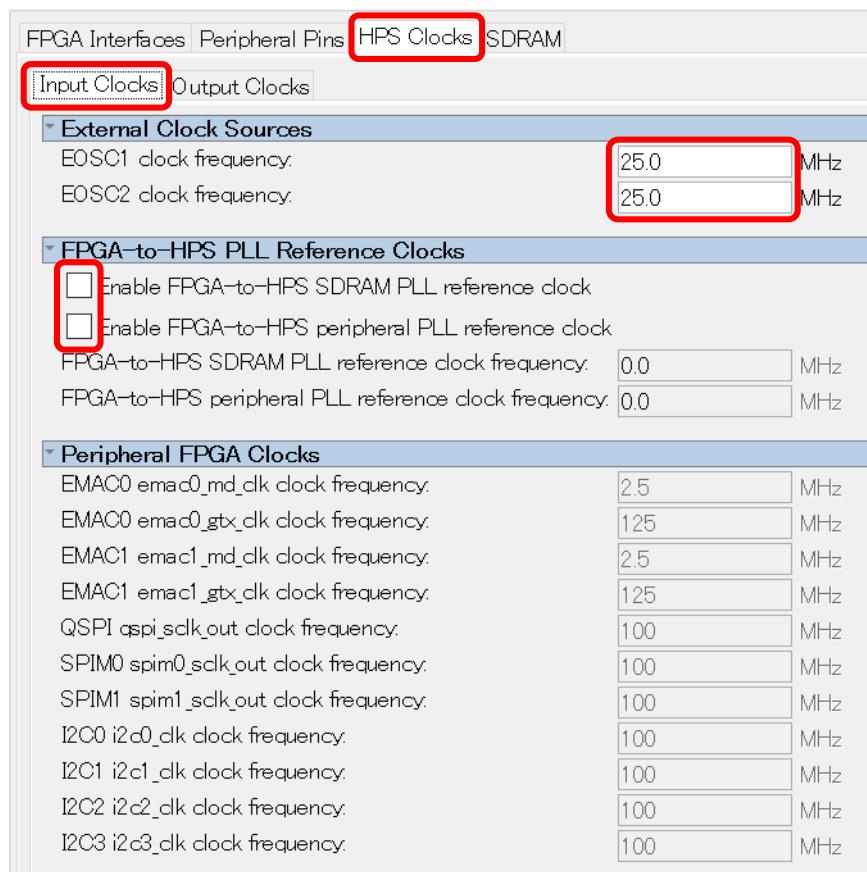

## 3-4. Step 4: Set the HPS Clock

The **HPS Clocks** tab sets the Clock source and frequency. All of these parameters are managed by the Clock Manager Component.

The parameters set in this tab are used when the boot loader (Preloader software) is generated. The Preloader is generated by "[4. Lab 2 - Software Exercise \(1\) Generate](#) Preloader."

1. Select the **HPS Clocks** tab.

2. Select the **Input Clocks** tab.

3. Ensure that the **EOSC1/EOSC2 clock frequency** is set to **25 MHz**. Also ensure that all **FPGA-to-HPS PLL Reference clocks** are **disabled**. The EOSC1 is a dedicated pin on the HPS side and is the clock source required to generate the clock for the HPS MPU. The Atlas-SoC board and the DE10 Nano board used in this article are set to 25 MHz.

Figure 3-25. HPS to FPGA Clock Settings

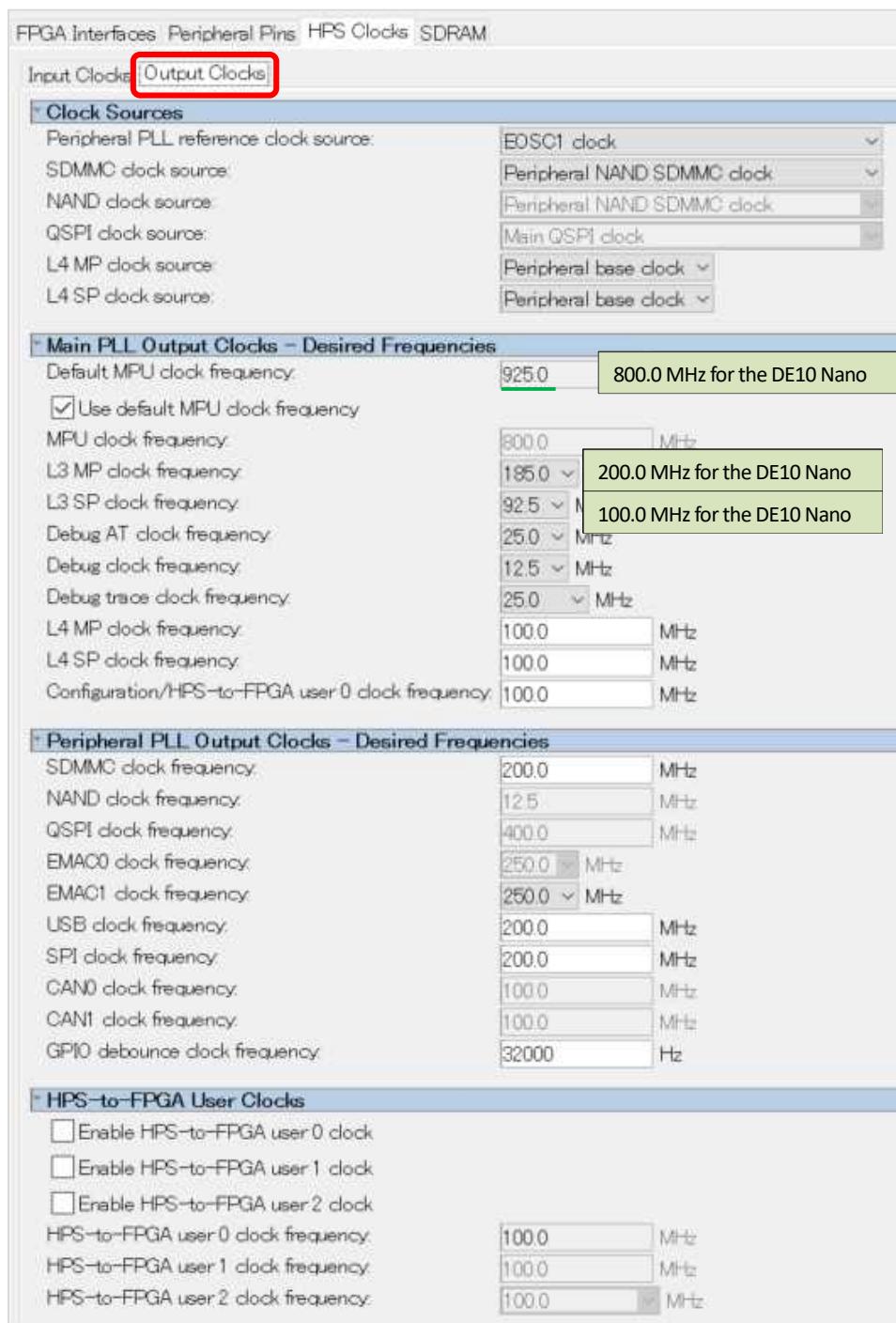

4. Select the **Output Clocks** tab.

5. Make sure that the settings are as shown below (no change from the default). This tab allows you to set the operating frequency of each HPS peripheral. The PLL setting is automatically calculated according to the set value.

Figure 3-26. Configuring HPS to FPGA Clock

### 3-5. Step 5: Configuring SDRAM

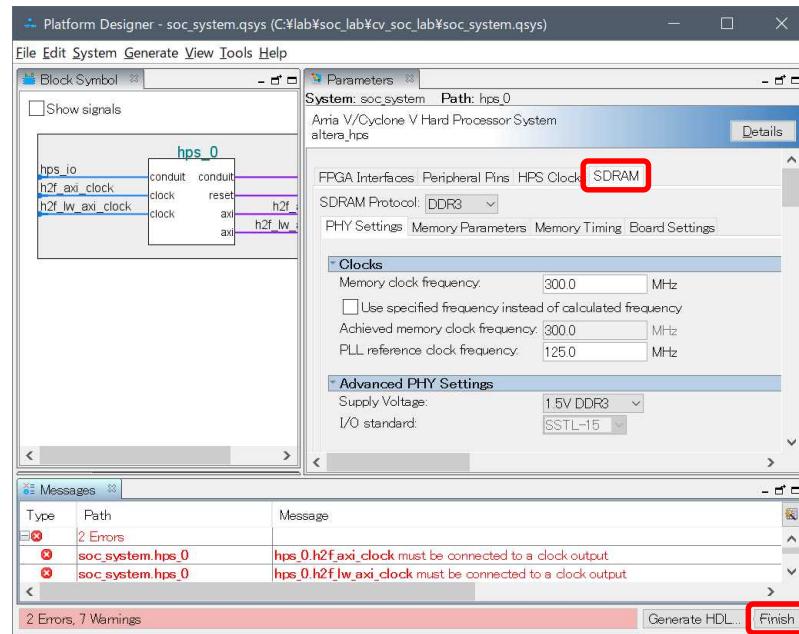

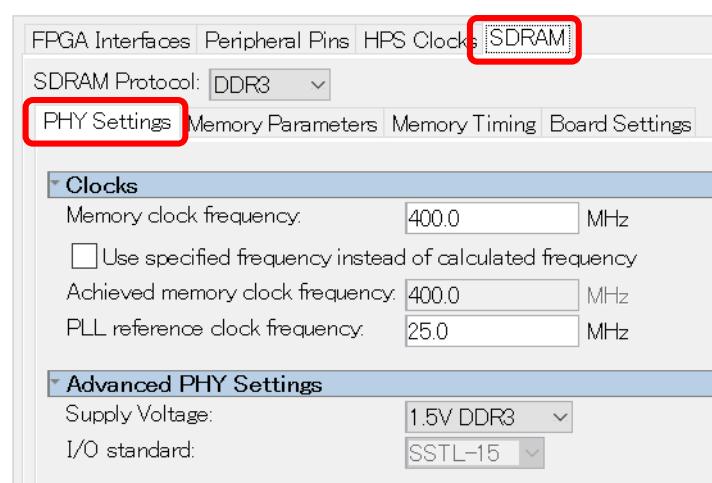

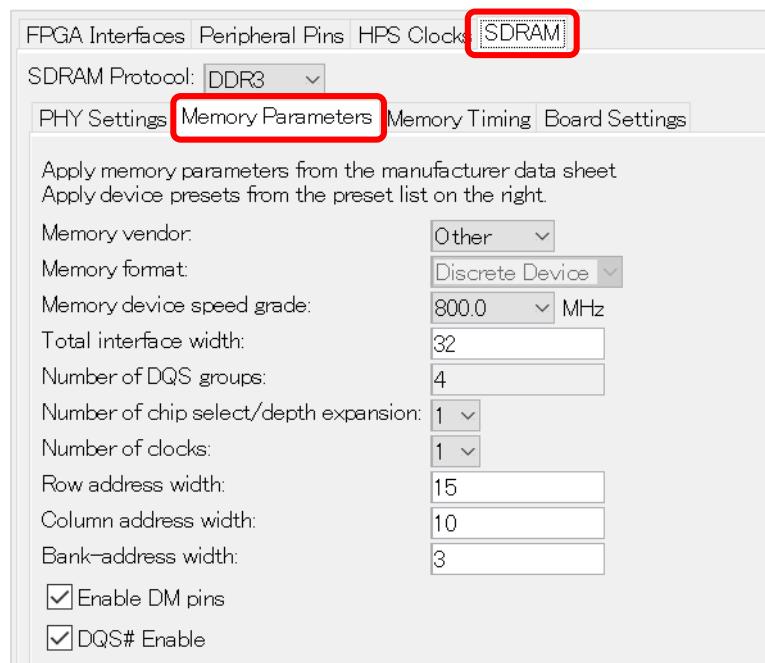

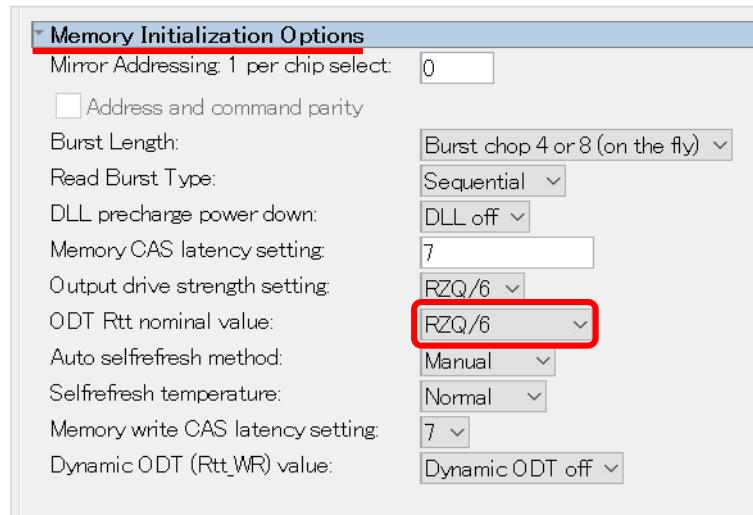

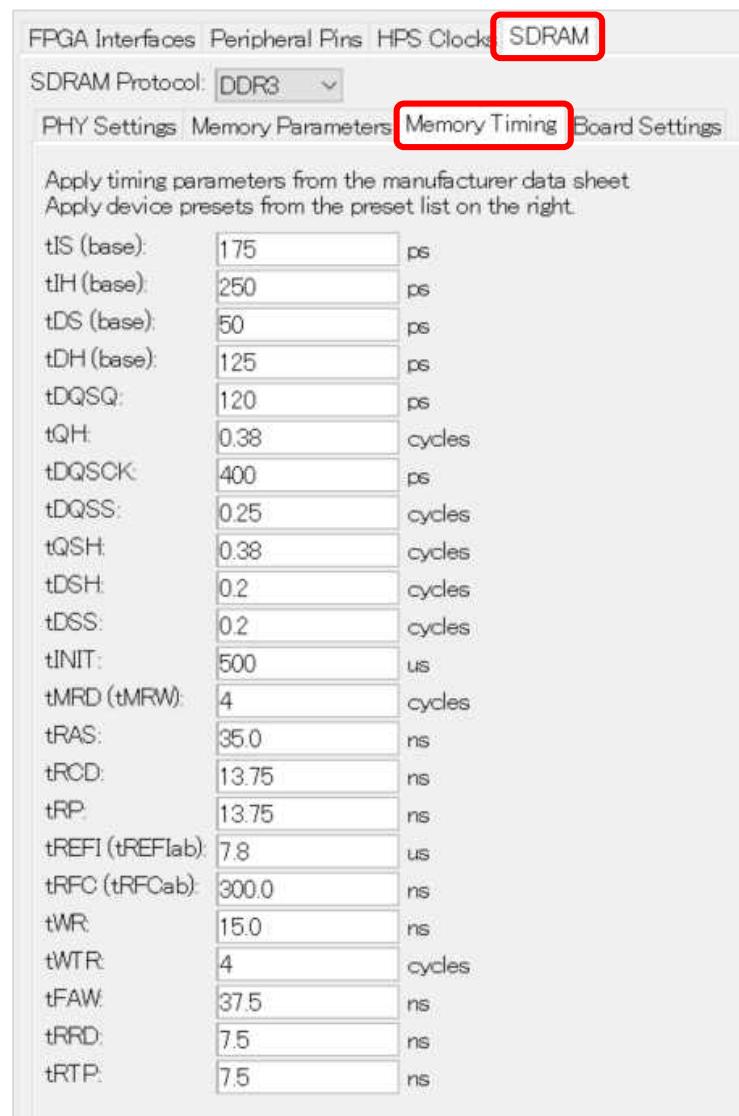

The **SDRAM** tab provides options for configuring parameters for the SDRAM controller on the HPS side and the connected DDR. Within the **SDRAM** tab, there are four additional tabs (**PHY Settings**, **Memory Parameters**, **Memory Timing**, **Board Settings**) for SDRAM configuration.

1. Click at the bottom of the **Arria V/Cyclone V Hard Processor System** window.

This action adds the HPS component to the Platform Designer system (required to display the Presets window in the next step).

Figure 3-27. Preparing to display the Parameters window

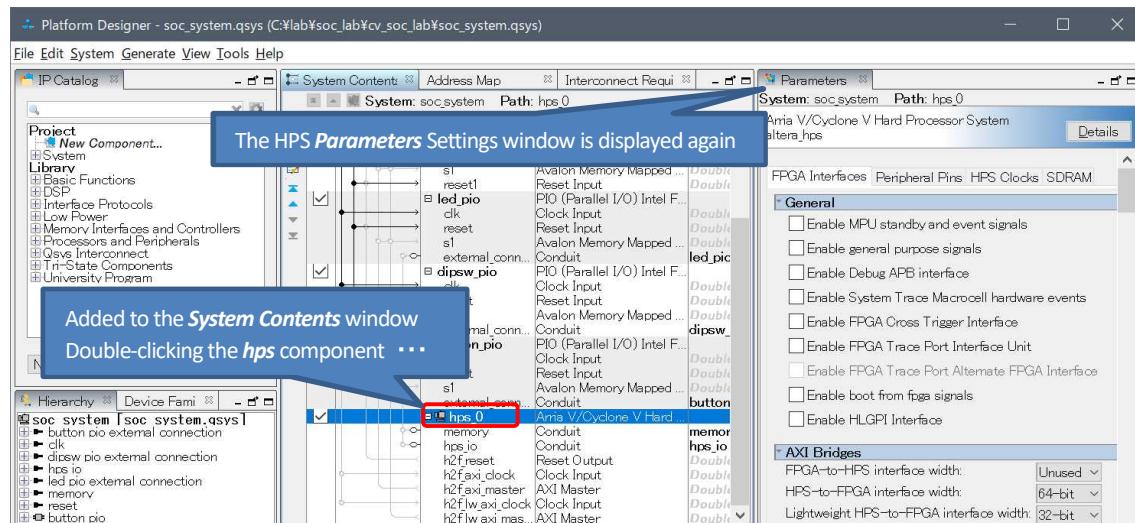

2. Double-click the HPS component in the **System Contents** window to display the HPS option settings in the **Parameters** window again.

This is necessary to display the **Preset** window in the next step.

Figure 3-28. Redisplay the HPS parameter setting window

3. Click the **SDRAM** tab in the **Parameters** window.

This time, we will use the preset SDRAM on the Atlas-SoC board.

Make sure that the **Presets** window is displayed.

**① Info:**

If the **Presets** window is not displayed, select Platform Designer **View** menu => **Presets** to display it.

If it is not displayed, select Platform Designer **View** menu => **Reset to System Layout** and select **Preset** again.

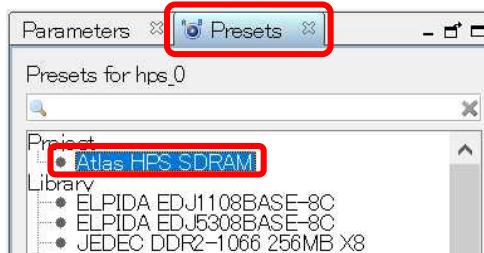

4. Select the **Atlas\_HPS\_SDRAM** preset in the **Presets** window.

Figure 3-29. Select Preset

5. When you click **Apply**, **Atlas\_HPS\_SDRAM** should be highlighted in bold. If it is, the settings are applied correctly.

6. If the **SDRAM** tab is not visible, click the **SDRAM** tab.

7. Click the **PHY Settings** tab and verify that the settings are as shown below.

Figure 3-30. Verify PHY Settings

8. Click the **Memory Parameters** tab and verify that the settings are as shown below.

Figure 3-31. Memory Parameters

9. Scroll down to the **Memory Initialization Options** section and verify that the **ODT Rtt nominal value** is set to **RZQ/6**.

Figure 3-32. Memory Initialization Options

10. Click on the **Memory Timing** tab and verify that the settings are as shown below.

Figure 3-33. Memory Timing

11. Click on the **Board Settings** tab and verify that **Use Altera's default settings** is selected in the **Setup and Hold Derating** and **Channel Signal Integrity** sections.

FPGA Interfaces Peripheral Pins HPS Clocks **SDRAM**

SDRAM Protocol: **DDR3**

PHY Settings Memory Parameters Memory Timing **Board Settings**

Use the Board Settings to model the board-level effects in the timing analysis.

The wizard supports single- and multi-rank configurations. Altera has determined the effects on the output signaling of these configurations and has stored the effects on the output slew rate and the channel uncertainty within the UniPHY MegaWizard.

*These values are representative of specific Altera boards. You must change the values to account for the board level effects for your board. You can use HyperLynx or similar simulators to obtain values that are representative of your board.*

**Setup and Hold Derating**

The slew rate of the output signals affects the setup and hold times of the memory device.

You can specify the slew rate of the output signals to refer to their effect on the setup and hold times of both the address and command signals and the DQ signals, or specify the setup and hold times directly.

Derating method:

Use Altera's default settings

Specify slew rates to calculate setup and hold times

Specify setup and hold times directly

|                                    |       |      |

|------------------------------------|-------|------|

| CK/CK# slew rate (Differential):   | 2.0   | V/ns |

| Address and command slew rate:     | 1.0   | V/ns |

| DQS/DQS# slew rate (Differential): | 2.0   | V/ns |

| DQ slew rate:                      | 1.0   | V/ns |

| tIS:                               | 0.325 | ns   |

| tIH:                               | 0.35  | ns   |

| tDS:                               | 0.2   | ns   |

| tDH:                               | 0.225 | ns   |

**Channel Signal Integrity**

Channel Signal Integrity is a measure of the distortion of the eye due to intersymbol interference or crosstalk or other effects. Typically when going from a single-rank configuration to a multi-rank configuration there is an increase in the channel loss as there are multiple stubs causing reflections. Please perform your channel signal integrity simulations and enter the extra channel uncertainty as compared to Altera's reference eye diagram.

Derating Method:

Use Altera's default settings

Specify channel uncertainty values

Address and command eye reduction (setup):  ns

Figure 3-34. Board Settings (1)

12. Scroll down to the **Board Skew** section and verify that the board skew is as shown below.

**Channel Signal Integrity**

Channel Signal Integrity is a measure of the distortion of the eye due to intersymbol interference or crosstalk or other effects. Typically when going from a single-rank configuration to a multi-rank configuration there is an increase in the channel loss as there are multiple stubs causing reflections. Please perform your channel signal integrity simulations and enter the extra channel uncertainty as compared to Altera's reference eye diagram.

Derating Method:

Use Altera's default settings

Specify channel uncertainty values

|                                            |     |    |

|--------------------------------------------|-----|----|

| Address and command eye reduction (setup): | 0.0 | ns |

| Address and command eye reduction (hold):  | 0.0 | ns |

| Write DQ eye reduction:                    | 0.0 | ns |

| Write Delta DQS arrival time:              | 0.0 | ns |

| Read DQ eye reduction:                     | 0.0 | ns |

| Read Delta DQS arrival time:               | 0.0 | ns |

**Board Skews**

PCB traces can have skews between them that can cause timing margins to be reduced. Furthermore skews between different ranks can further reduce the timing margin in multi-rank topologies.

|                                                              |       |    |

|--------------------------------------------------------------|-------|----|

| Maximum CK delay to DIMM/device:                             | 0.6   | ns |

| Maximum DQS delay to DIMM/device:                            | 0.6   | ns |

| Minimum delay difference between CK and DQS:                 | -0.01 | ns |

| Maximum delay difference between CK and DQS:                 | 0.01  | ns |

| Maximum skew within DQS group:                               | 0.02  | ns |

| Maximum skew between DQS groups:                             | 0.02  | ns |

| Average delay difference between DQ and DQS:                 | 0.0   | ns |

| Maximum skew within address and command bus:                 | 0.02  | ns |

| Average delay difference between address and command and CK: | 0.0   | ns |

Figure 3-35. Board Settings (2)

13. Select **File** menu => **Save** in Platform Designer to save the HPS parameter settings specified in the previous steps.

### 3-6. Step 6: Setting the HPS Clock and Export Signal

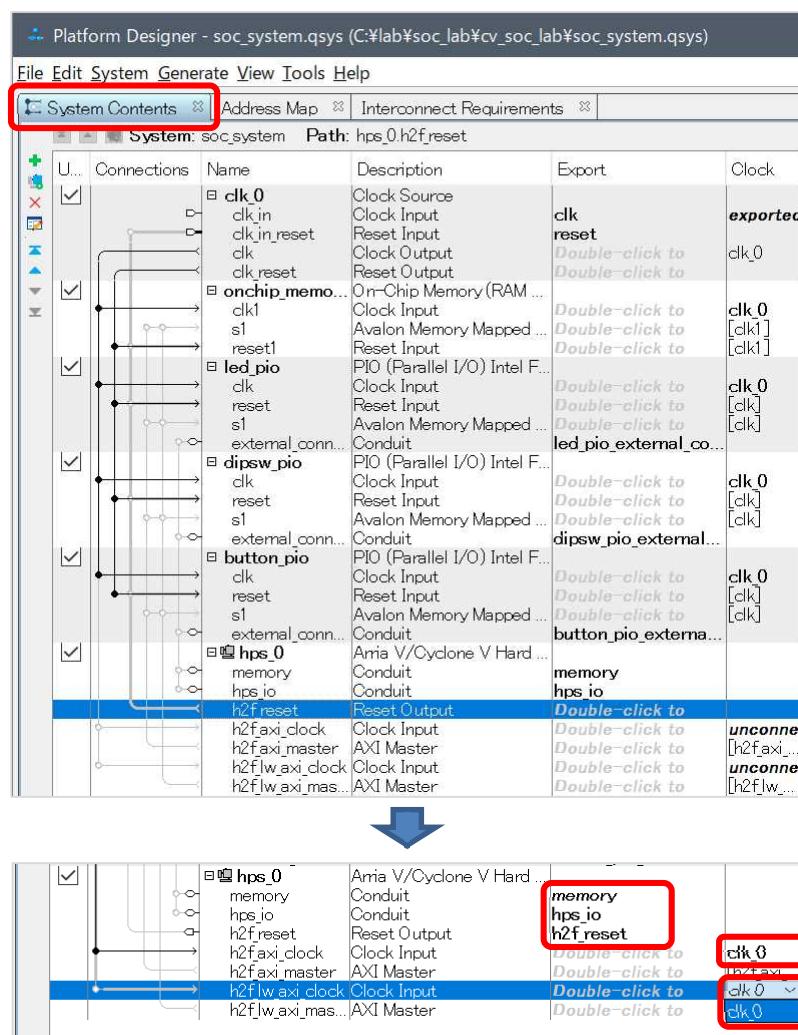

In this step, you will set the HPS H2F bridge clock and the LWH2F bridge clock.

The clocks set here are the clocks on the FPGA side of each bridge (h2f\_axi\_clk and h2f\_lw\_axi\_clk shown below). The clocks on the HPS side are l3\_main\_clk and l4\_mp\_clk, which are set in "[3-4. Step 4: Set the HPS Clock](#)" and are different from the clocks set here. The difference in clocks is absorbed within the bridge.

The HPS export signal is also set. This export signal is used for communication outside Platform Designer. For example, it is used to connect Platform Designer to other logic on the FPGA and to place it on pins.

Figure 3-36. Clock between HPS and FPGA

1. Go to the **System Contents** tab.

2. By specifying the signal name in the **Export** column, you can route the signal to the outside of the Platform Designer system. Make sure that the **hps\_io** port of the HPS component you just added is exported with the signal name **hps\_io**.

3. Similarly, make sure that the **memory** port of the HPS component is exported with the signal name **memory**. This is the IO of the SDRAM on the HPS side that you just configured.

4. Export the **h2f\_rest** of the HPS component. Double-click the **Export** column of **H2f\_reset**.

Rename it to "**h2f\_reset**" and press Enter to export.

5. Configure the Clock Input interface **h2f\_axi\_clock** on the HPS. Select **clk\_0** from the pull-down menu in the **Clock** column next to **H2f\_axi\_clock** and connect **clk\_0** to **h2f\_axi\_clock**.

6. Configure the Clock Input interface **h2f\_lw\_axi\_clock** on the HPS in the same way. Select **clk\_0** from the pull-down menu in the **Clock** column next to **H2f\_lw\_axi\_clock** and connect **clk\_0** to **h2f\_lw\_axi\_clock**.

Figure 3-37. Setting the clock and export signal

Now that **clk0** is connected, the two error messages in the **Message Window** in [Figure 3-23](#), should disappear.

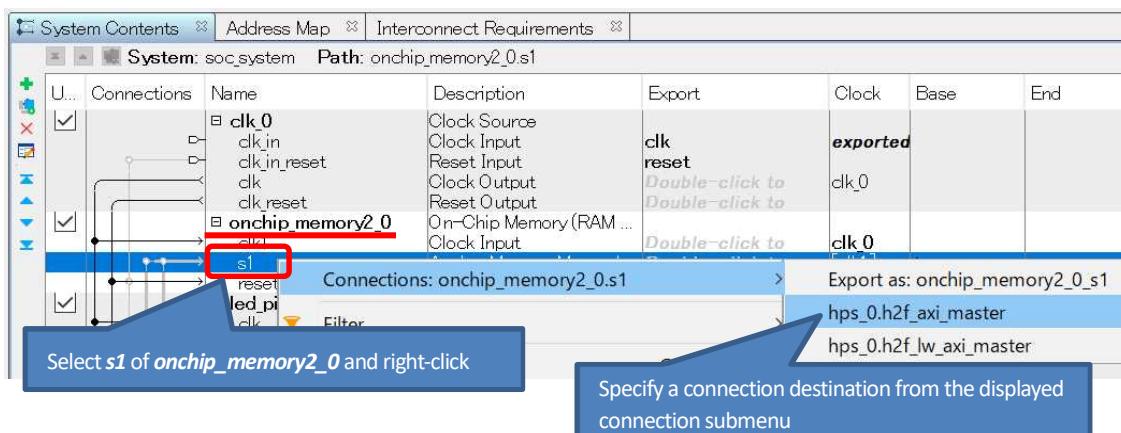

### 3-7. Step 7: Connecting HPS Components to Other Components

In this step, you will connect the HPS components added to the Platform Designer system and the components already implemented in the Platform Designer system. Since the FPGA will operate at `clk_0` (50 MHz), `clk_0` is already connected to each component.

1. Verify that the Clock Input interface of the `Onchip_memory2_0` component is connected to `clk_0`.

2. Verify that the Clock Input interface of the `Led_pio` component is connected to `clk_0`.

3. Verify that the Clock Input interface of the `Dipsw_pio` component is connected to `clk_0`.

4. Verify that the Clock Input interface of the `Button_pio` component is connected to `clk_0`.

5. Select `s1` of `onchip_memory2_0`, then right-click and select `hps_0.h2f_axi_master` from the connection submenu. This connects the `s1` interface of the `onchip_memory2_0` component to the **HPS h2f\_axi\_master**. This configuration allows the Arm® processor to access onchip\_memory on the FPGA side.

Figure 3-38. Connecting components

6. Similarly, right-click `s1` of `button_pio` and select `hps_0.h2f_lw_axi_master` from the connection submenu. This connects the `s1` interface of the `button_pio` component to the **HPS h2f\_lw\_axi\_master**.

Notice that the connection destination is **`h2f_lw_axi_master`**. The same applies to each subsequent PIO component.

7. Similarly, right-click `s1` of `dipsw_pio` and select `hps_0.h2f_lw_axi_master` from the Connect submenu. This connects the `s1` interface of the `dipsw_pio` component to the **HPS h2f\_lw\_axi\_master**.

8. Similarly, right-click `s1` of `led_pio` and select `hps_0.h2f_lw_axi_master` from the Connect submenu. This connects the `s1` interface of the `led_pio` component to the **HPS h2f\_lw\_axi\_master**.

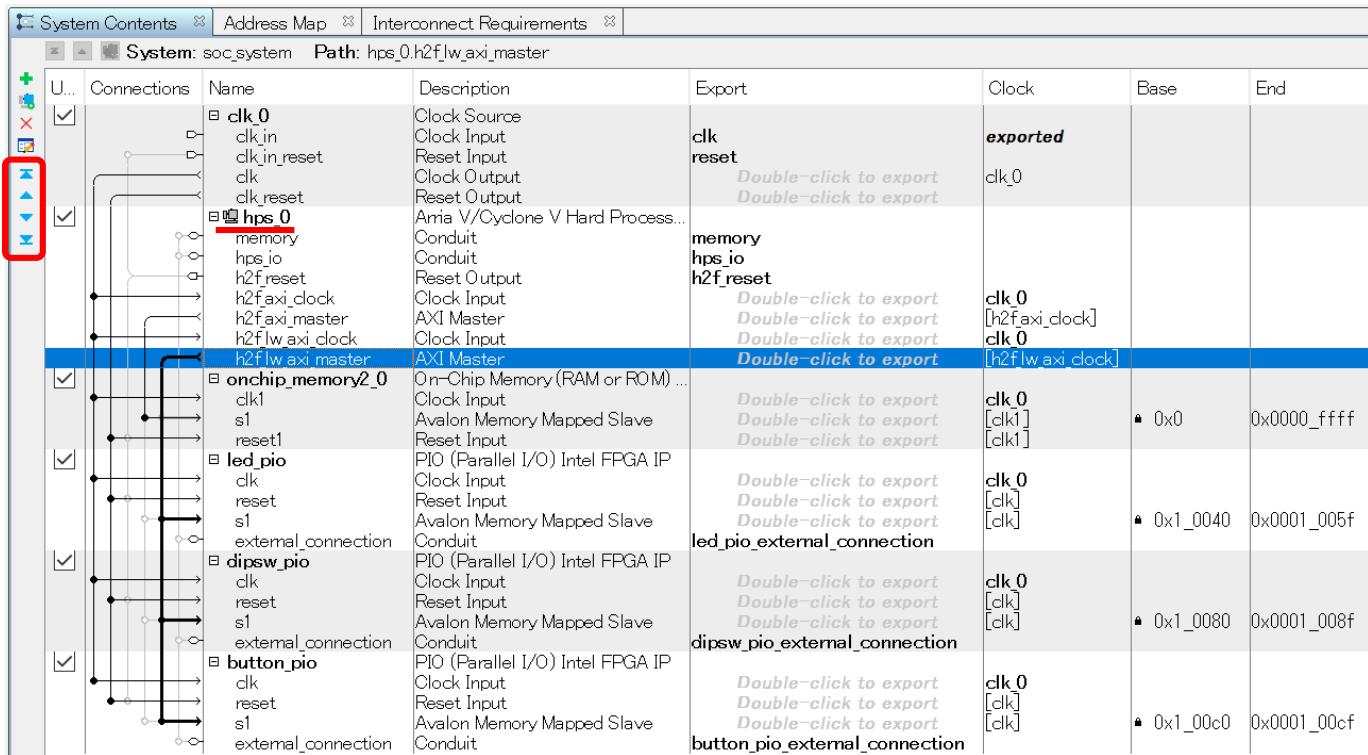

9. Select the HPS component and use the **up and down**  buttons in the Platform Designer toolbar on the left side of the **System Contents** window to move the HPS component below **clk\_0**. Use to move the HPS component below **clk\_0**.

The Platform Designer system after configuration is complete is shown below.

Figure 3-39. The Platform Designer system after configuration is complete

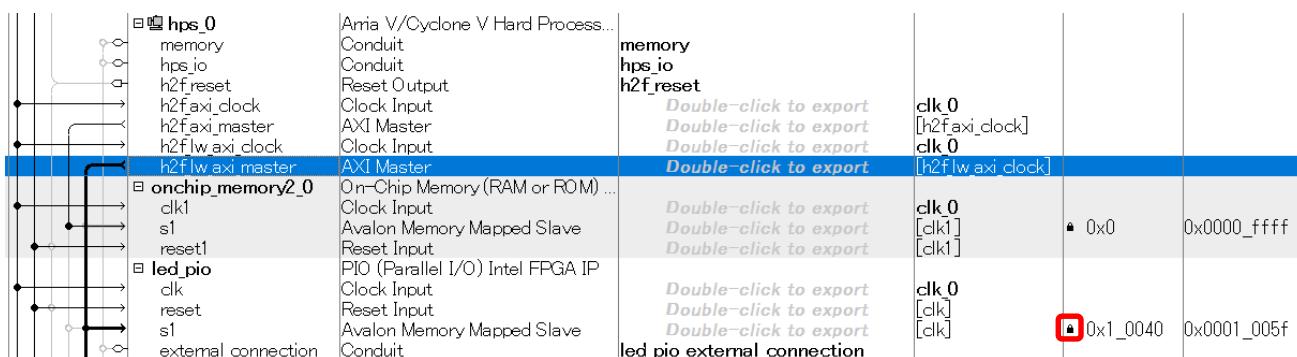

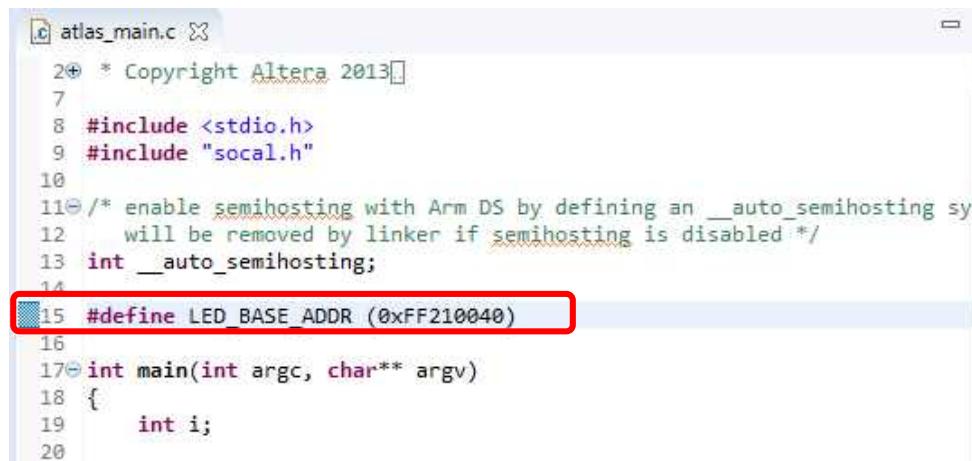

Consider accessing led\_pio.

If you look at the second **Base** column from the right of led\_pio, it is set to 0x0001\_0040. This is the offset address of led\_pio in Platform Designer. Earlier [8](#) The master to access led\_pio is **HPS h2f\_lw\_axis\_master**. Since the base address of the Lightweight HPS-to-FPGA bridge was 0xFF20\_0000, accessing this led\_pio would be:

Bridge base address (0xFF20\_0000) + Platform Designer offset address (0x0001\_0040) = **0xFF21\_0040**

Other components can be considered in the same way, and dipsw\_pio would be **0xFF21\_0080**.

Next, consider accessing onchip\_memory.

The base address of the **HPS h2f\_axi\_master** bridge, which is another path from the HPS to the FPGA, is 0xC000\_0000. In this case, the Platform Designer offset address of onchip\_memory connected to the **HPS h2f\_axi\_master** is 0x0, so in this case, the base address of the bridge (0xC000\_0000) is the base address to access onchip\_memory.

## 3-8. Step 8: Connect Resets and Assign Base Addresses

This step provides a bulk reset connection and automatic base address assignment.

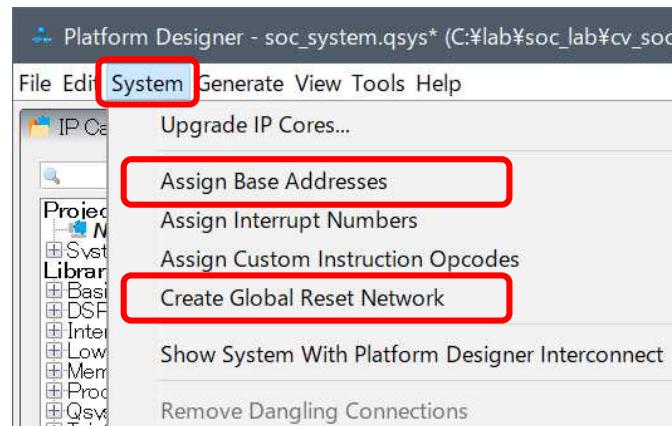

1. Select Platform Designer **System** menu => **Create Global Reset Network** to connect all reset interfaces in the design in bulk.

2. Automatically assign base addresses for all components so that there are no duplicate addresses. Select **System** menu => **Assign Base Addresses**.

Figure 3-40. Reset Bulk Connect and Assign Base Addresses Automatically

If you did **Assign Base Addresses**, nothing happened.

In this exercise, the base addresses for each peripheral were fixed beforehand, so they were not automatically assigned.

You can lock the address setting by using the lock symbol next to the base address, as shown in [Figure 3-41](#). Each click toggles whether the address is locked or not. If you want to lock the address, lock it with the lock symbol after setting the address. You can also lock it by selecting Platform Designer's **Edit** menu => **Lock Base Address**.

Figure 3-41. Fixing the Base Address

## 3-9. Step 9: Checking the Platform Designer System

1. Verify that the Platform Designer system you designed is as shown in "[Table 3-1. Connectivity of the Platform Designer system after design](#)" below. Also refer to "[Figure 3-39. The Platform Designer system after configuration is complete.](#)"

To be consistent with the Quartus® Prime project for the exercise, make sure that the export signals are properly exported and named correctly. You can use any signal name in the actual design. There is no regulation on the order of components.

Table 3-1. Connectivity of the Platform Designer system after design

| Component  | Port name           | Connection                                      |

|------------|---------------------|-------------------------------------------------|

| clk_0      | clk_in              | Export as <b>clk</b>                            |

|            | clk_in_reset        | Export as <b>reset</b>                          |

|            | clk                 | Connect to all components                       |

|            | clk_reset           | Connect to all components except hps_0          |

| led_pio    | external_connection | Export as <b>led_pio_external_connection</b>    |

| dipsw_pio  | external_connection | Export as <b>dipsw_pio_external_connection</b>  |

| button_pio | external_connection | Export as <b>button_pio_external_connection</b> |

| hps_0      | h2f_axi_master      | Connect to onchip_memory2_0.s1                  |

|            | h2f_lw_axi_master   | Connect to led_pio.s1                           |

|            |                     | Connect to dipsw_pio.s1                         |

|            |                     | Connect to button_pio.s1                        |

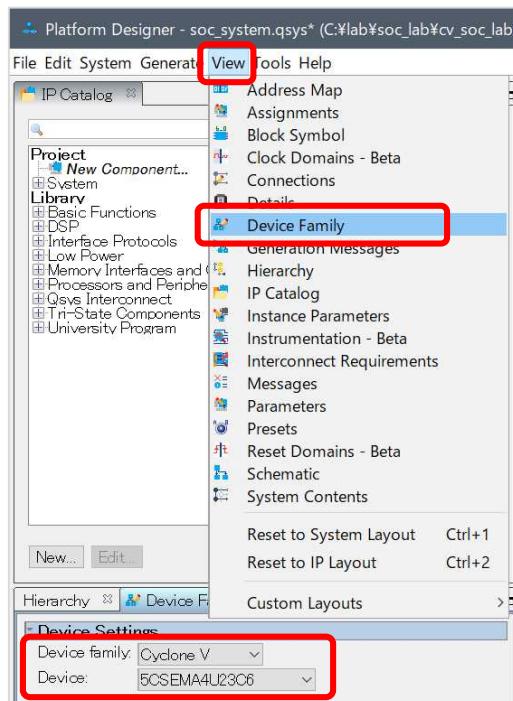

2. Select Platform Designer **View** menu => **Device Family** and confirm that the **Device Family** is **Cyclone V**.

The Device is 5CSEMA4U23C6 for the **Atlas-SoC** board and 5CSEBA6U23I7DK for the **DE10 Nano** board.

Figure 3-42. Device Family tab

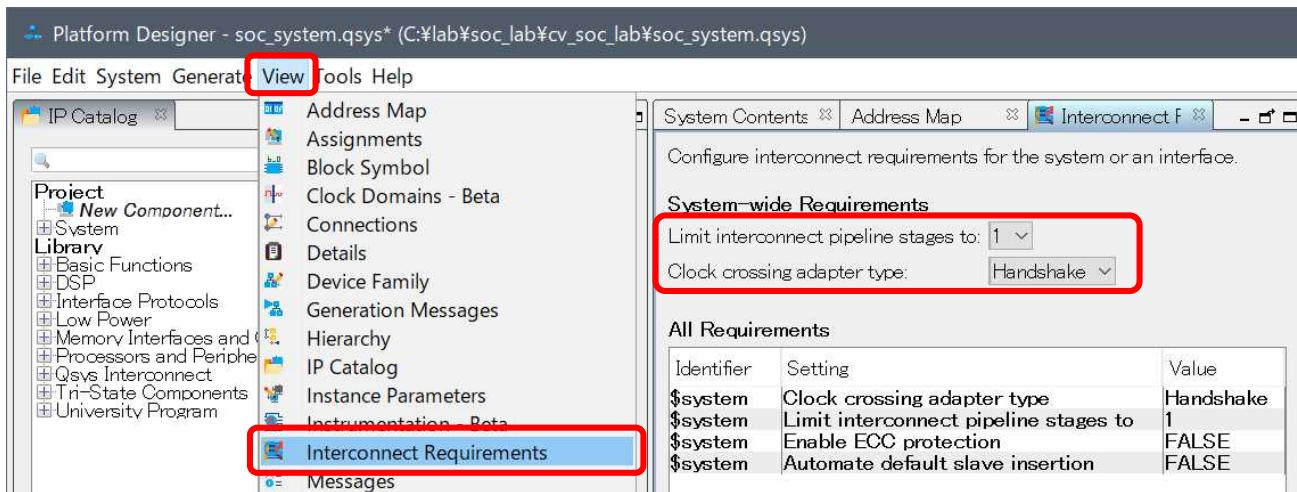

3. Select Platform Designer **View** menu Interconnect Requirements and set **Limit interconnect pipeline stages** to 1.

Increasing the number of stages allows more timing, but also increases the logic of the FPGA. Make sure the **Clock crossing adapter** type is set to **Handshake**. Increasing the number of stages allows more timing, but also increases the logic of the FPGA.

Make sure that the **Clock crossing adapter type** is set to **Handshake**.

Figure 3-43. Set project parameters

## 3-10. Step 10: Generate the Platform Designer system

Generate the completed Platform Designer system.

1. Check the **Message** box on the **System Contents** tab for any remaining errors. If there are any errors, you must fix them before continuing. Ignore the blue warning at this time.

| Type                  | Path | Message                                                                                                                       |

|-----------------------|------|-------------------------------------------------------------------------------------------------------------------------------|

| 2 Warnings            |      |                                                                                                                               |

| soc_system.hps_0      |      | "Configuration/HPS-to-FPGA user 0 clock frequency" (desired_cfg_clk_mhz) requested 100.0 MHz, but only achieved 97.368421 MHz |

| soc_system.hps_0      |      | 1 or more output clock frequencies cannot be achieved precisely, consider revising desired output clock frequencies.          |

| 5 Info Messages       |      |                                                                                                                               |

| soc_system.button_pio |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

| soc_system.dipsw_pio  |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

| soc_system.hps_0      |      | HPS Main PLL counter settings: n = 0 m = 73                                                                                   |

| soc_system.hps_0      |      | HPS peripheral PLL counter settings: n = 0 m = 39                                                                             |

| soc_system.led_pio    |      | PIO inputs are not hardwired in test bench. Undefined values will be read from PIO inputs during simulation.                  |

Figure 3-44. Message window display

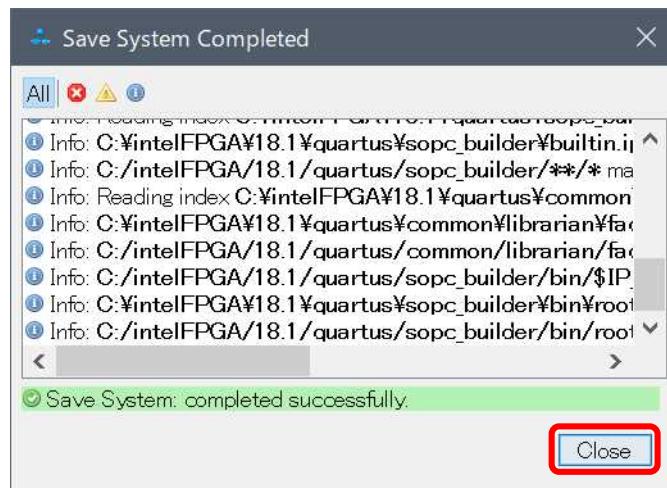

2. Select **File** menu => **Save** to save the Platform Designer system. **[Close]** when **Save System Completed** pops up.

Figure 3-45. Saving the Platform Designer system

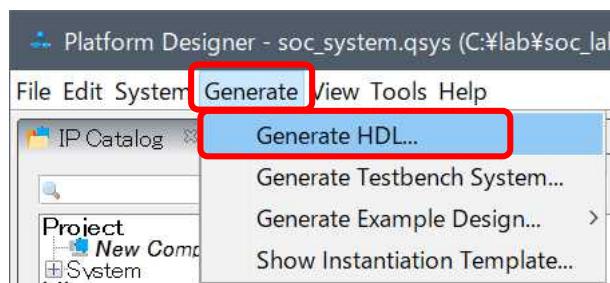

3. Select **Generate** menu => **Generate HDL**.

Figure 3-46. Generating the Platform Designer system

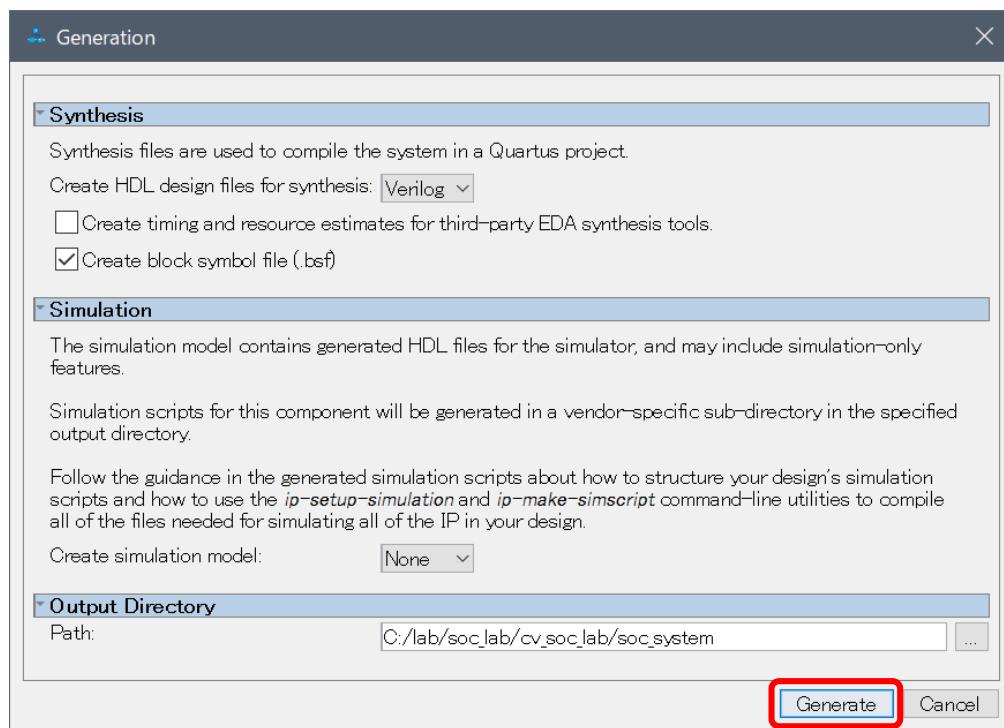

4. Check the settings in the **Generation** window and execute [Generate].

Figure 3-47. Platform Designer System Generate Execution Window

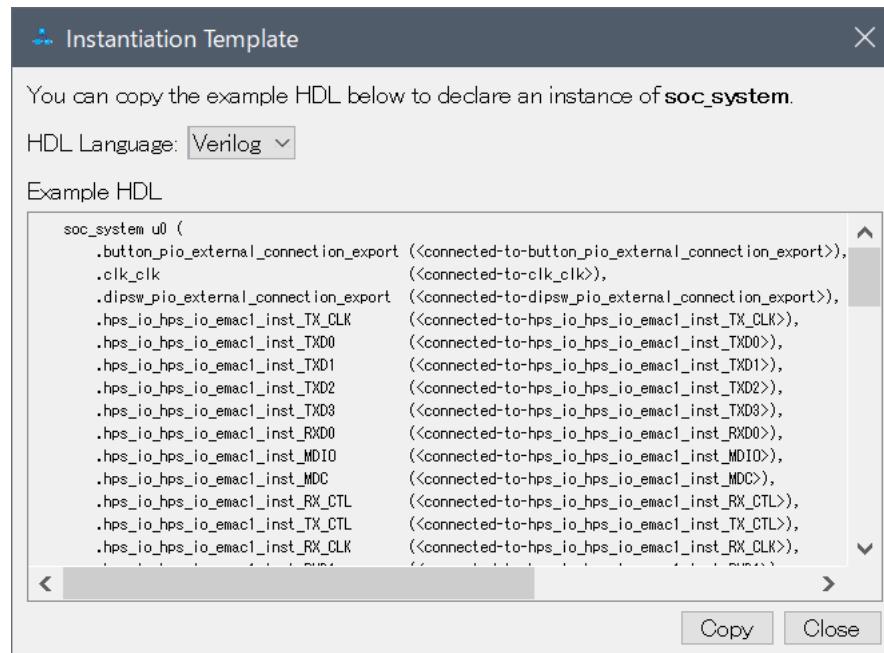

\_\_\_\_\_ 5. Platform Designer's **Generate** menu => **Show Instantiation Template** shows an example of an instance that can be used when instantiating a top design.

This time, it has already been instantiated, so there is no particular work to be done, but it is very useful when actually using it.

Figure 3-48. Platform Designer system instance example

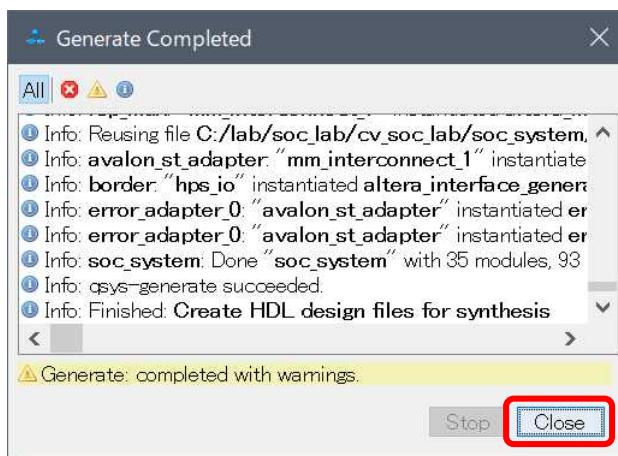

6. After Platform Designer generation is complete, click the **[Close]** button to close the Platform Designer system generation dialog box and return to Quartus® Prime.

Figure 3-49. Platform Designer system generation complete

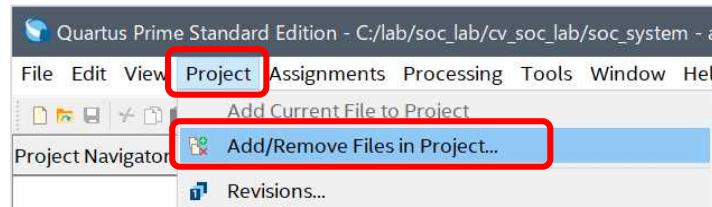

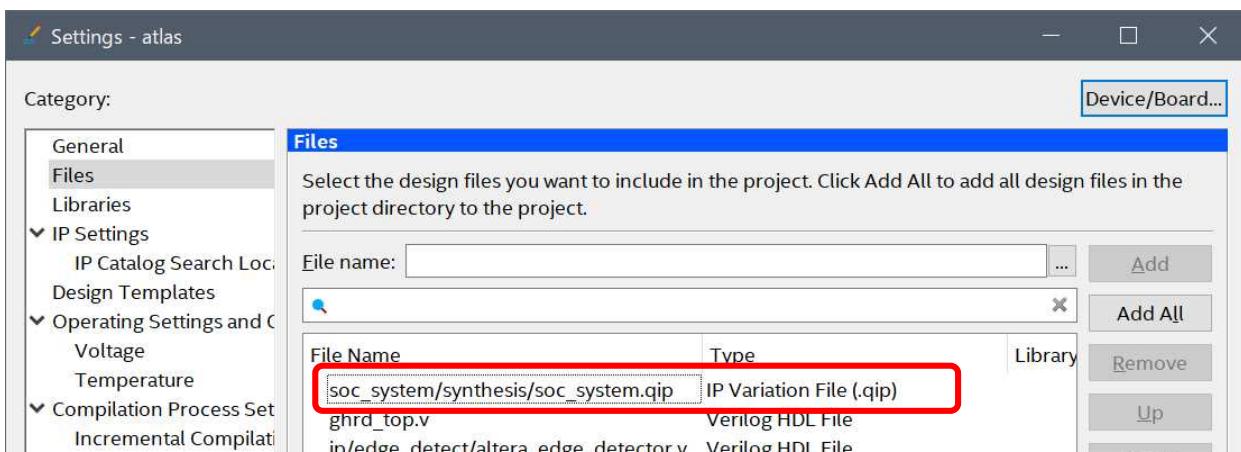

7. Select Quartus® Prime's **Project** menu => **Add/Remove Files in Project** (The Settings dialog box appears with the Files category selected).

Figure 3-50. Select Add/Remove Files in Project

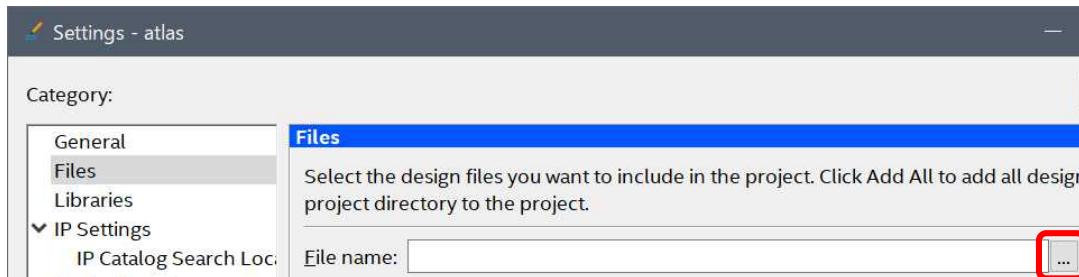

8. Press the **[...]** button next to the **File name** field in the Settings dialog box and browse to the **soc\_system/synthesis** folder from the **Select File** window.

Figure 3-51. Settings dialog box

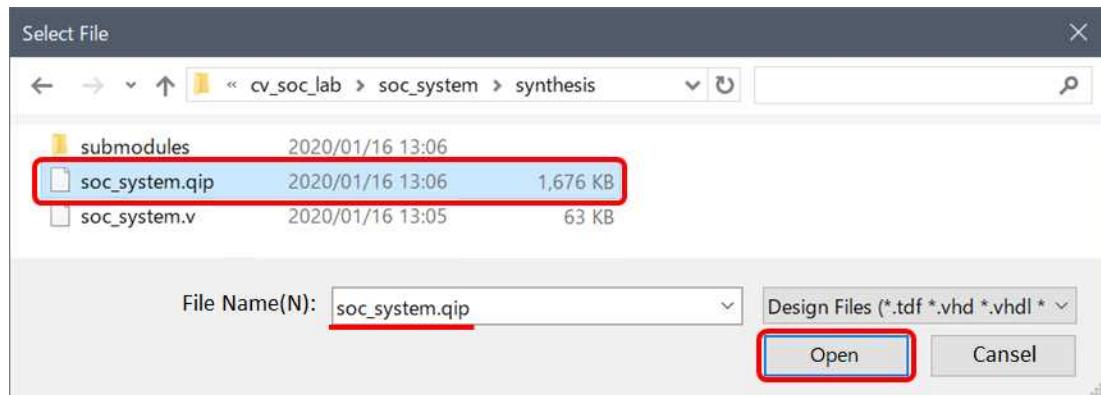

9. Select the file **Soc\_system.qip** and click **[Open]**. This qip file links the generated components in Platform Designer. Instead of registering each generated file individually, you can add a Platform Designer system to a project by registering this qip file.

Figure 3-52. Specifying the Qip File

10. Verify that the file has been added.

Figure 3-53. Register Qip file

11. Close the **Settings** dialog box with the **[OK]** button.

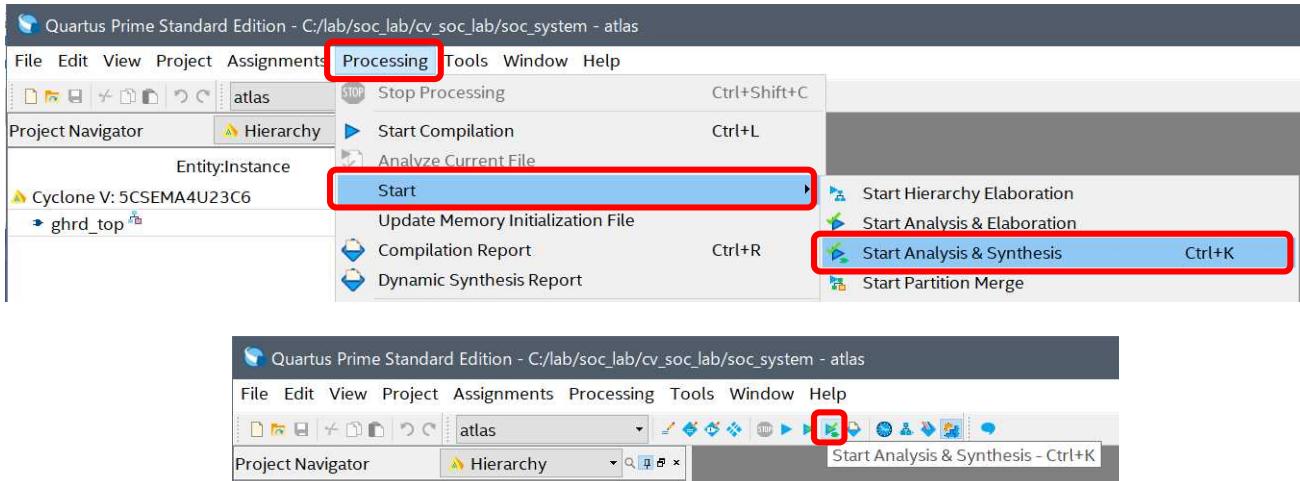

## 3-11. Step 11: Set pin assignments and compile Quartus® Prime project

For HPS-only IO, pin assignments are basically done automatically by the tool because pin placement is fixed. The exception is that SDRAM interfaces require a tool-generated script to be executed by the designer. To execute the script, first generate the netlist and then execute the script.

Therefore, first run Analysis & Synthesis to create the netlist, then execute the script and compile the FPGA again.

1. In Quartus® Prime, select **Processing** menu => **Start** => **Start Analysis & Synthesis**.

(Alternatively, click the Start Analysis & Synthesis button  on the GUI.)

Figure 3-54. Start Analysis & Synthesis

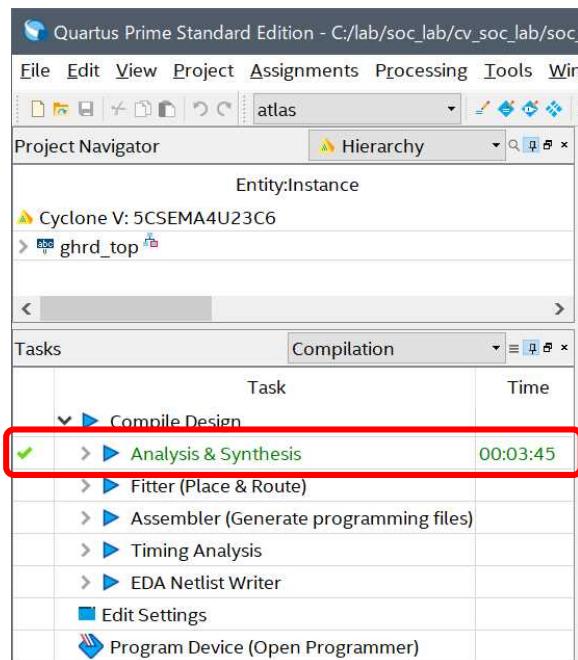

2. When finished, verify that there are no errors. , there are no errors. The netlist is now created.

Figure 3-55. Verify successful completion of Start Analysis & Synthesis

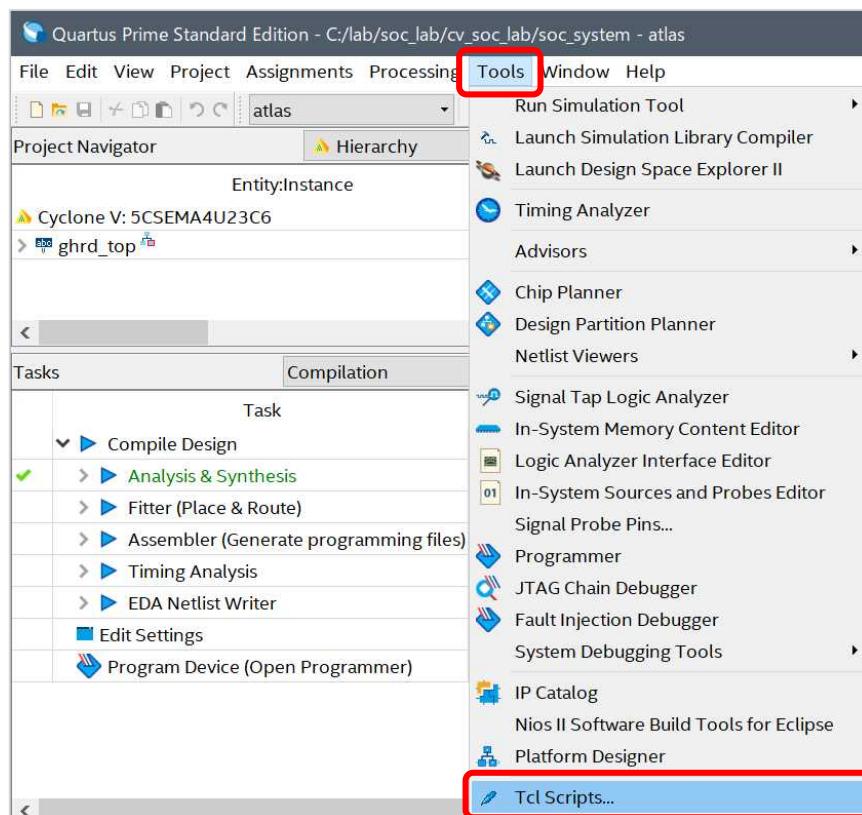

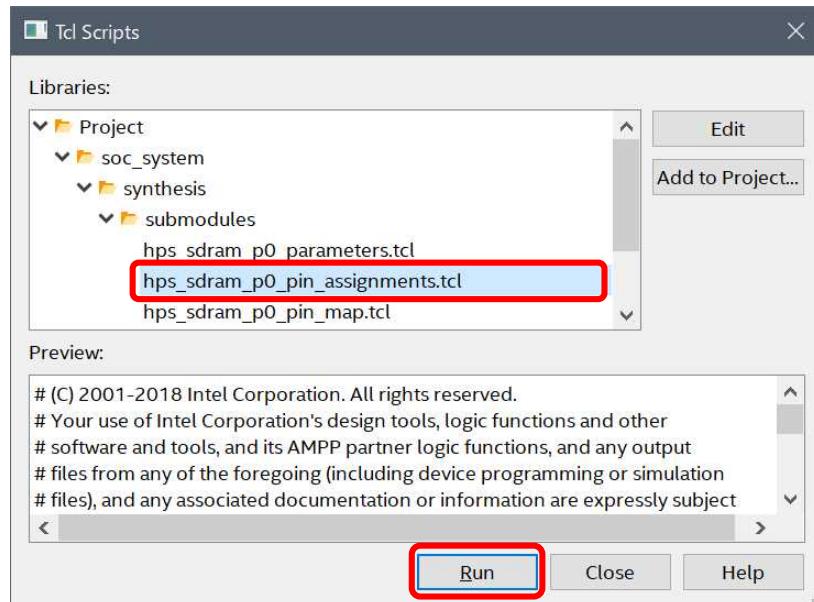

3. Select Quartus® Prime **Tools** menu => **TCL scripts**.

Figure 3-56. Starting the Tcl Scripts Window

4. Select **hps\_sdram\_p0\_pin\_assignments.tcl** in **soc\_system => synthesis => submodules**, and click the **[Run]** button (it takes a while for the application to take effect).

This operation will apply the settings made in the SDRAM Controller tab of HPS, such as SDRAM IO Standard and OCT settings.

Figure 3-57. Executing a Tcl Script

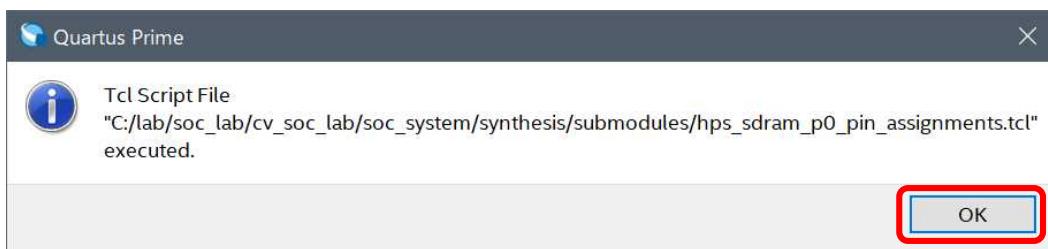

5. When you have finished, click the [OK] button.

Figure 3-58. Completing a Tcl Script

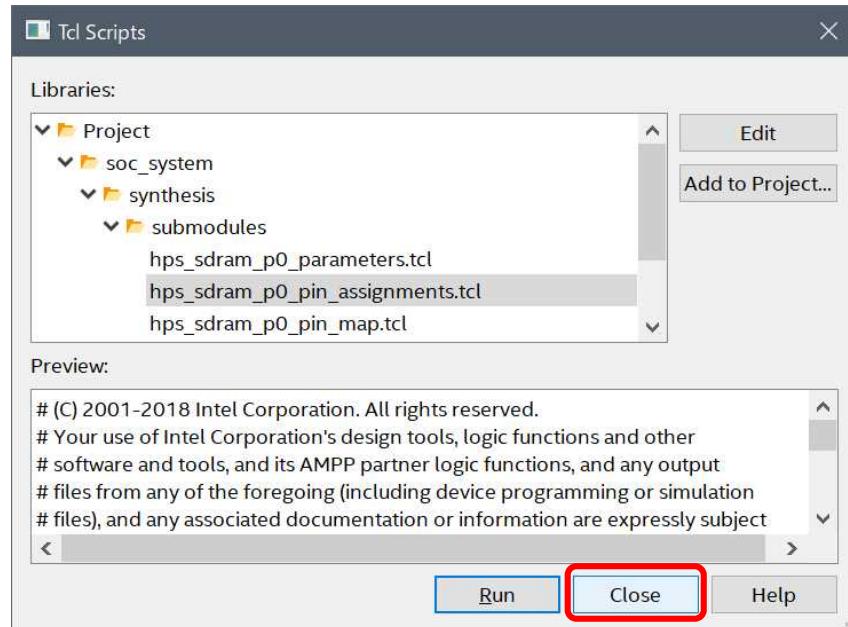

6. [Close] the Tcl Scripts window.

Figure 3-59. Close Tcl Scripts Window

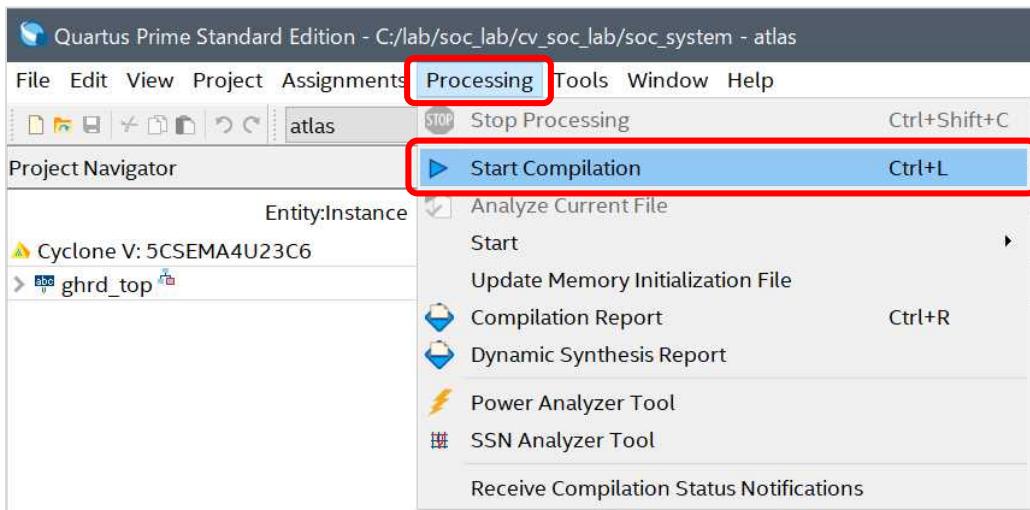

7. Select Quartus® Prime **Processing** menu => **Start Compilation** (Alternatively, click the Start Compilation button  on the GUI) to compile the FPGA. This compilation creates a .sof file that will be the working image of the HW and a handoff file that will be passed to the next software development.

Figure 3-60. Run Start Compilation

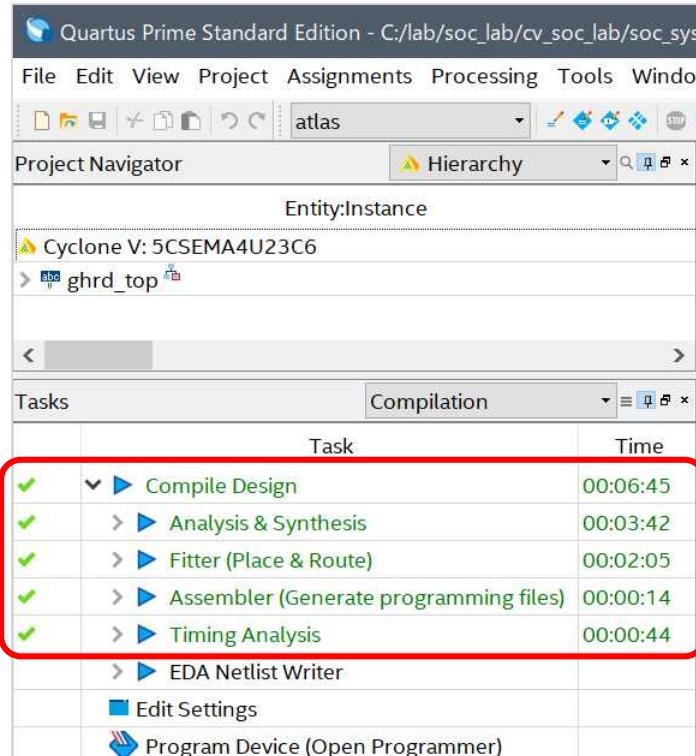

8. Verify that the compilation is complete.

Figure 3-61. Compilation complete

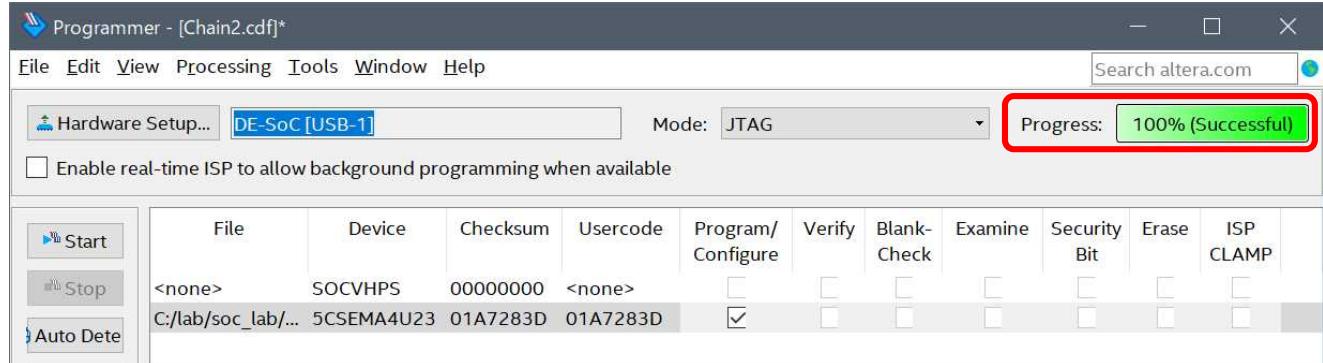

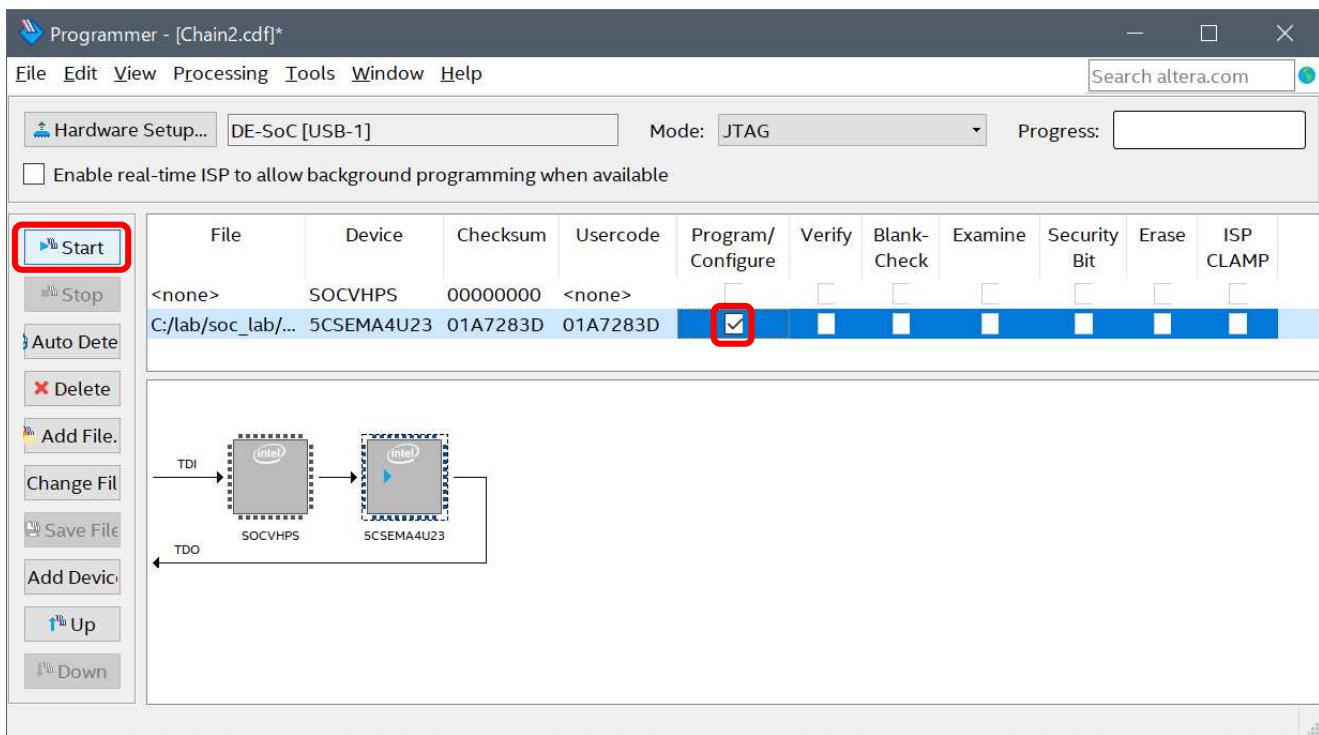

## 3-12. Step 12: Verify the output file

Verify the output file in Quartus® Prime and Platform Designer.

\_\_\_ 1. Using Windows® OS Explorer, navigate to the output file folder (below).

C:\\$lab\\$soc\_lab\\$cv\_soc\_lab\\$output\_files

\_\_\_ 2. Verify that there is a .sof file output in the above folder.

atlas.sof for Atlas-SoC board

DE10 Nano.sof for DE10 Nano board.

As mentioned earlier, this file is the operational image file of the FPGA.

This file will be written to the FPGA on the board using a tool called Programmer in a later exercise.

\_\_\_ 3. Using Windows® OS Explorer, navigate to the hardware/software handoff directory.

C:\\$lab\\$soc\_lab\\$cv\_soc\_lab\\$hps\_isw\_handoff\\$soc\_system\_hps\_0

Under the above folder are the hardware/software handoff files generated by the tool. These files contain various data set in the HPS component screen of Platform Designer, information about the SDRAM interface of HPS, and other files. These files are used to generate a file called Preloader, which is used to initialize the HPS side.

These files will be used to create Preloader in later exercises.

### Lab 1 Hardware Exercise Summary

In this section, you configured the hardware including the Arm® processor by performing the following tasks:

- Adding HPS components to the Platform Designer system

- Configuring HPS components

- Connecting HPS components to other components

- Generating the Platform Designer system

- Checking the files output by Quartus® Prime/Platform Designer

**Lab 1 is now complete.**

## 4. Lab 2 - Software Exercise (1) Generate Preloader

In this section, you will generate Preloader using the handoff file created in "[3. Lab 1: Hardware Exercise](#)"

**Point:**

In SoC EDS v20.1 (SoC EDS v19.1 and later), you need to build Preloader under the Linux OS environment. In this exercise, you will use the Windows Subsystem for Linux (WSL1) included with Windows® 10 to generate the boot loader.

Preloader is a boot loader based on the U-boot second program loader (Later, u-boot spl) and customized for Altera® SoC FPGAs. Preloader is responsible for:

- HPS pin multiplex configuration

- HPS IOCSR configuration

- HPS PLL and clock settings

- HPS peripheral reset unreset

- SDRAM initialization (calibration, etc.)

- Deployment of the next stage boot image to SDRAM

As mentioned above, Preloader provides the function of initializing the HPS block and loading the U-boot and OS into SDRAM. Preloader is automatically generated by using a handoff file that is automatically generated when Quartus® Prime/Platform Designer is designed. Therefore, the settings made in Quartus® Prime/Platform Designer can be applied to the HPS block without the user having to build initialization software. The sof file I just checked is the operating image of the FPGA side. On the other hand, the operating image of the HPS side is this file called Preloader. Note that the operating image is executed using different files for the FPGA side and the HPS side.

Now let's create the Preloader.

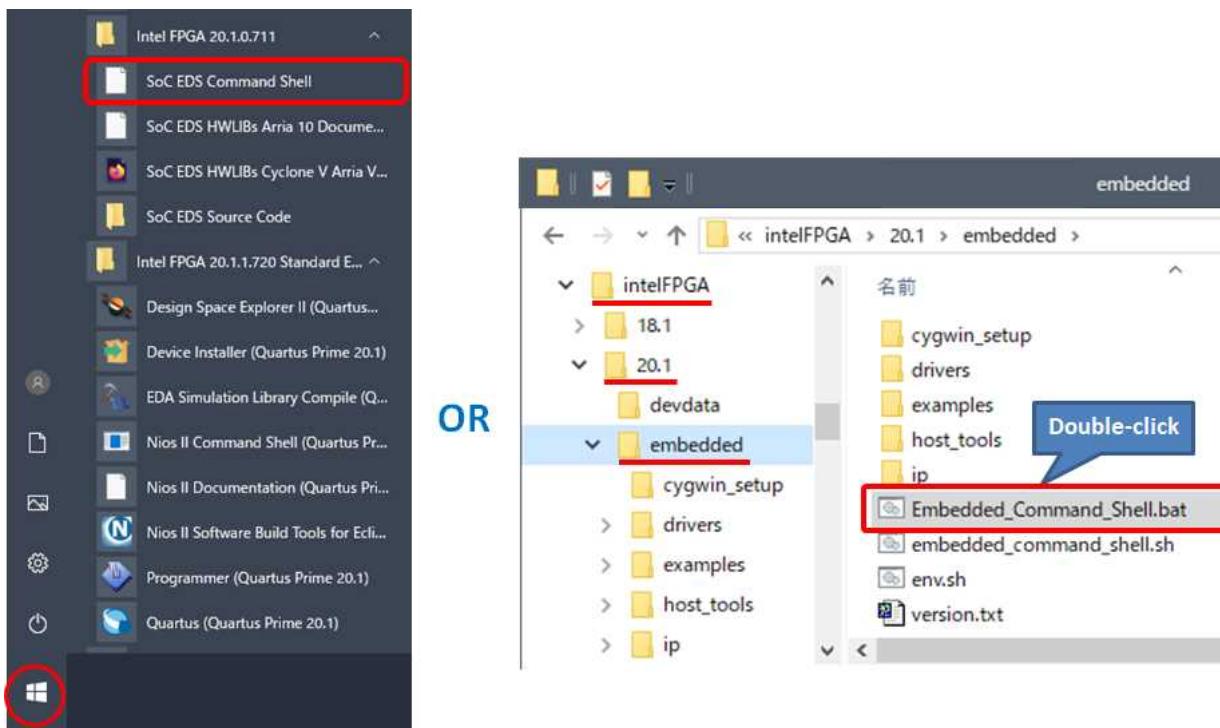

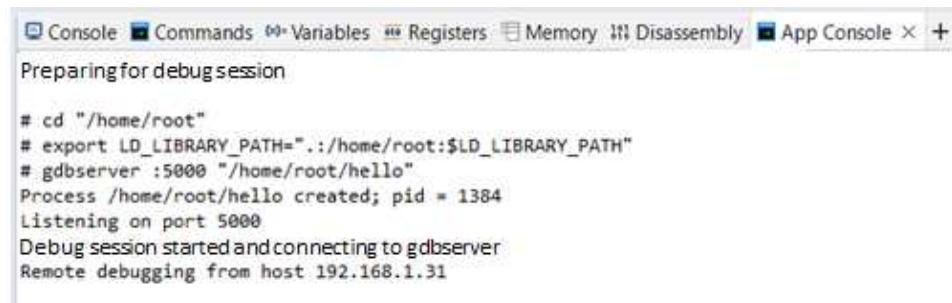

## 4-1. Step 1: Launch Embedded Command Shell

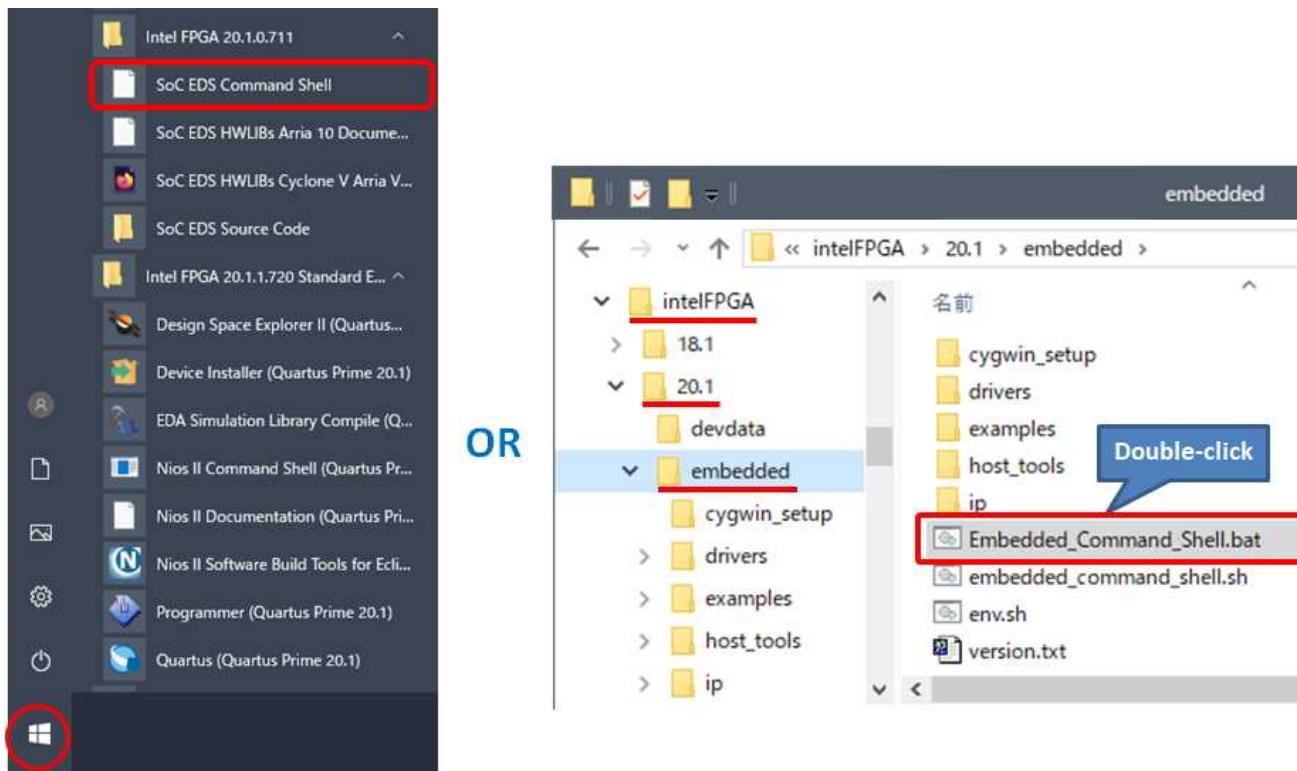

## 1. Launch the Embedded Command Shell included with the SoC EDS.

Launch the Embedded Command Shell by double-clicking the startup script `Embedded_Command_Shell.bat` located in the Windows® Start menu or in the SoC EDS installation folder.

Figure 4-1. Starting the Embedded Command Shell

## 4-2. Step 2: Generate the bsp project

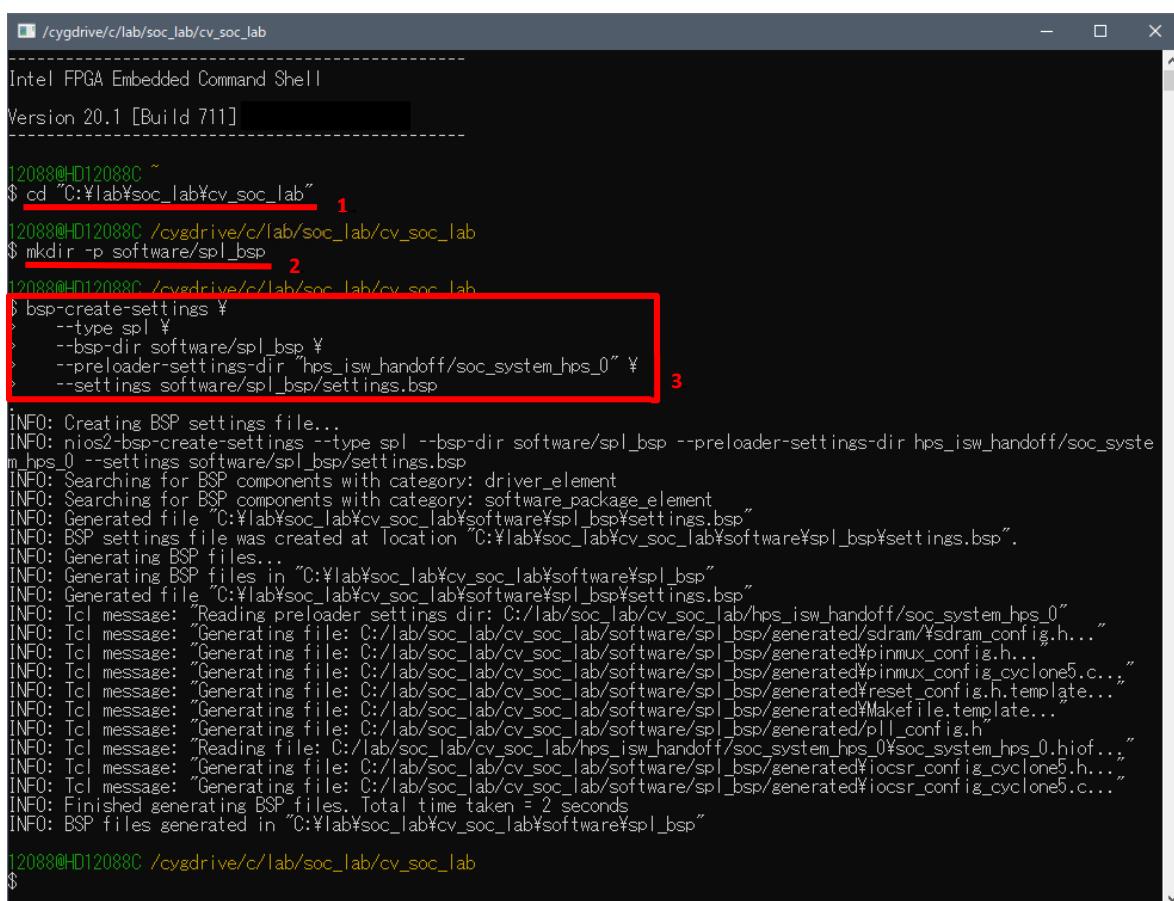

Generate the bsp project required for Preloader generation from the Quartus® Prime design handoff information (hps\_isw\_handoff/soc\_system\_hps\_0).

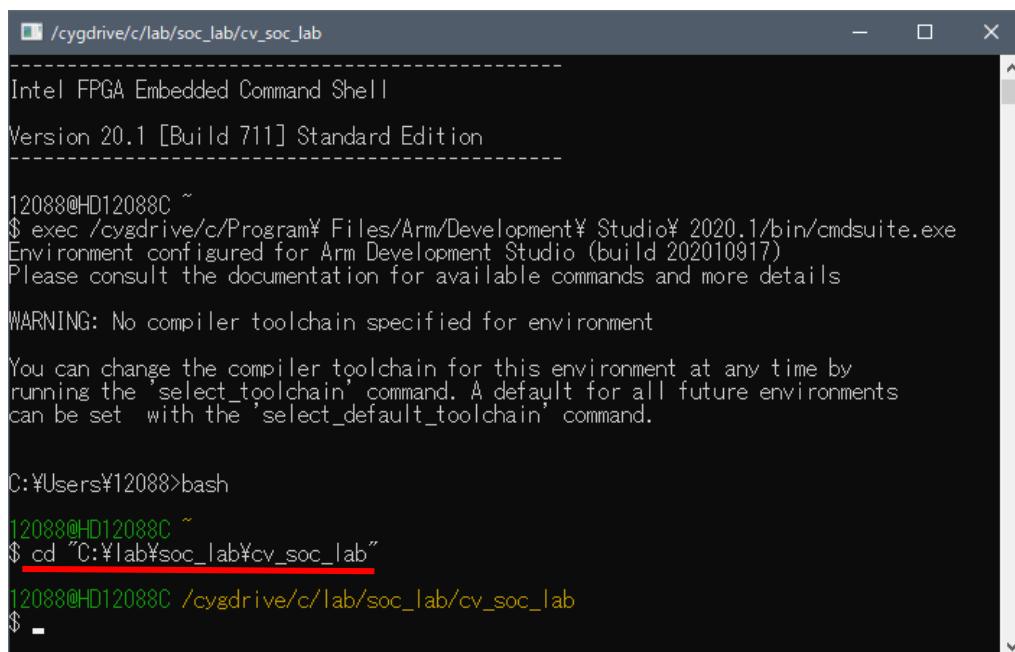

1. Change the current directory of the **Embedded Command Shell** to the Quartus® Prime project directory.

```

$ cd "C:\lab\soc_lab\cv_soc_lab"

```

2. Then run the following command to create the directory where the bsp project will be output:

```

$ mkdir -p software/spl_bsp

```

3. The following command generates the bsp project: The generated directory of the bsp project contains the source code that contains the definitions with the handoff information.

```

$ bsp-create-settings

--type spl

--bsp-dir software/spl_bsp

--preloader-settings-dir "hps_isw_handoff/soc_system_hps_0"

--settings software/spl_bsp/settings.bsp

```

```

12083@HD12088C ~

$ cd "C:\lab\soc_lab\cv_soc_lab" 1

12083@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab

$ mkdir -p software/spl_bsp 2

12083@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab

$ bsp-create-settings

--type spl

--bsp-dir software/spl_bsp

--preloader-settings-dir "hps_isw_handoff/soc_system_hps_0" 3

--settings software/spl_bsp/settings.bsp

:INFO: Creating BSP settings file...

:INFO: nios2-bsp-create-settings --type spl --bsp-dir software/spl_bsp --preloader-settings-dir hps_isw_handoff/soc_system_hps_0 --settings software/spl_bsp/settings.bsp

:INFO: Searching for BSP components with category: driver_element

:INFO: Searching for BSP components with category: software_package_element

:INFO: Generated file "C:\lab\soc_lab\cv_soc_lab\software\spl_bsp\settings.bsp"

:INFO: BSP settings file was created at location "C:\lab\soc_lab\cv_soc_lab\software\spl_bsp\settings.bsp".

:INFO: Generating BSP files...

:INFO: Generating BSP files in "C:\lab\soc_lab\cv_soc_lab\software\spl_bsp"

:INFO: Generated file "C:\lab\soc_lab\cv_soc_lab\software\spl_bsp\settings.bsp"

:INFO: Tcl message: "Reading preloader settings dir: C:/lab/soc_lab/cv_soc_lab/hps_isw_handoff/soc_system_hps_0"

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/sdram/sdram_config.h..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/pinmux_config.h..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/pinmux_config_cyclone5.c..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/reset_config.h.template..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/Makefile.template..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/pll_config.h"

:INFO: Tcl message: "Reading file: C:/lab/soc_lab/cv_soc_lab/hps_isw_handoff/soc_system_hps_0/soc_system_hps_0.hif...

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/locsr_config_cyclone5.h..."

:INFO: Tcl message: "Generating file: C:/lab/soc_lab/cv_soc_lab/software/spl_bsp/generated/locsr_config_cyclone5.c...

:INFO: Finished generating BSP files. Total time taken = 2 seconds

:INFO: BSP files generated in "C:\lab\soc_lab\cv_soc_lab\software\spl_bsp"

12083@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab

$

```

Figure 4-2. Generating a Bsp project

**⚠ Note:**

Error protection is required before using bsp-create-settings in SoC EDS v20.1std on Windows® 10. If an error occurs, take the corrective action described in the following reference sites and run bsp-create-settings again.

**📄 Reference:**

Macnica Altera FPGA Insights "[Workaround for bsp-create-settings execution error in SoC EDS environment](#)"

**ⓘ Info:**

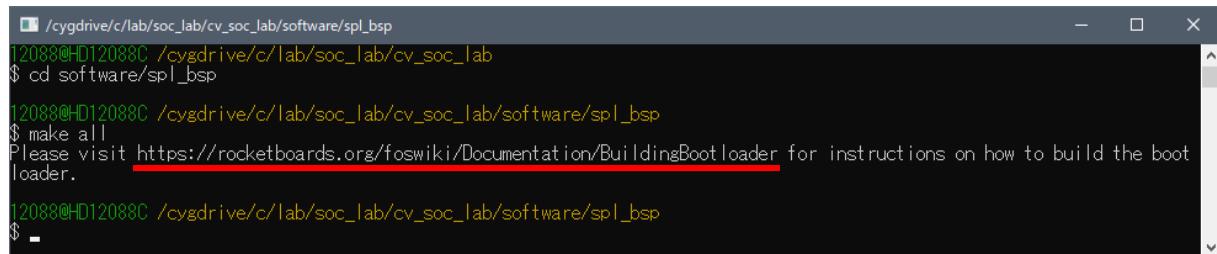

The bsp project contains a Makefile but is not used in the SoC EDS v20.1 (SoC EDS v19.1 or later) environment. Running make under the bsp project will take you to the documentation page (URL) on the Rocketboards.org site with instructions for building the bootloader.

```

12088@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

$ cd software/spl_bsp

12088@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

$ make all

Please visit https://rocketboards.org/foswiki/Documentation/BuildingBootloader for instructions on how to build the boot

loader.

12088@HD12088C /cygdrive/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

$ -

```

See: [Building Bootloader for Cyclone V and Arria 10](#)

bsp-create-settings created a bsp project under the software/spl\_bsp directory. The source files contained in the bsp project will then be used to build Preloader.

## 4-3. Step 3: Launch Preloader Build Environment

Generate the bsp project needed to generate Preloader from the Quartus® Prime design handoff information (hps\_isw\_handoff\$\soc\_system\_hps\_0).

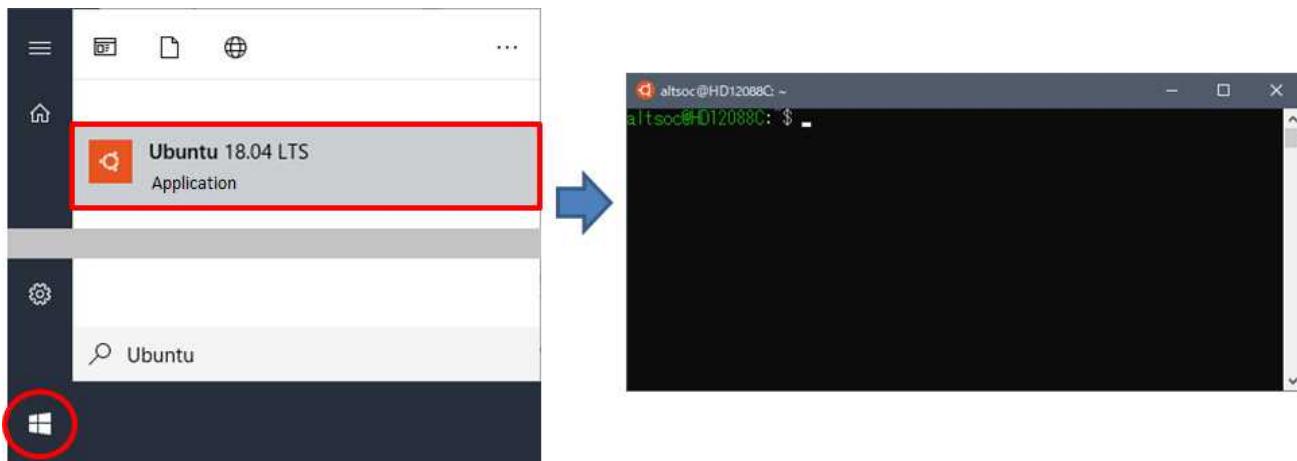

As noted at the beginning of Lab 2, building Preloader (boot loader) requires a Linux OS environment. This exercise uses Ubuntu 18.04 LTS running on WSL1. The following steps will be performed on the Ubuntu 18.04 LTS terminal of WSL, so please set up your WSL/Ubuntu 18.04 LTS environment beforehand.

**⚠ Note:**

- \* In addition to WSL 1, which was originally released, there are two different WSL environments: WSL 2 (Windows Subsystem for Linux 2), which is supported in Windows® 10 version 2004 and later. Please note that this exercise uses WSL 1.

- \* This document uses Ubuntu 18.04 LTS, but you should read the version of Ubuntu as appropriate for your environment.

**ⓘ Info:**

To set up the WSL 1 environment, refer to the following article.

**ⓘ Reference:**

Macnica Altera FPGA Insights "[Building Preloader/U-Boot with WSL \[Part 1\] Environment Setup](#)"

\* At the “SoC Startup Trial Seminar” held in our company, it will be set up beforehand.

1. Start Ubuntu 18.04 LTS running on WSL1.

Type Ubuntu in the Windows® Start menu and click on the suggested Ubuntu 18.04 LTS app.

Figure 4-3. Starting the Embedded Command Shell

**① Info:**

In your Linux OS environment, you need to install various packages necessary for building. In the case of Ubuntu 18.04 LTS, use the following command to add the necessary packages beforehand. "Do you want to continue? [Y/n]" appears, enter Y.

```

$ sudo apt update ↵

$ sudo apt upgrade ↵

$ sudo apt install build-essential bison flex ncurses-dev ↵

```

\* At the "SoC Startup Trial Seminar" held in our company, it will be set up beforehand.

---

**2. Install the bare metal GCC toolchain on Ubuntu 18.04 LTS on WSL1.**

Run the following command in **Ubuntu 18.04 LTS terminal** to download and extract the GCC toolchain. If already installed, proceed to the next step.

```

$ mkdir ~/toolchains ↵

$ cd ~/toolchains ↵

$ wget https://releases.linaro.org/components/toolchain/binaries/latest-7/arm-eabi/gcc-linaro-7.5.0-2019.12-x86_64_arm-eabi.tar.xz ↵

$ tar xf gcc-linaro-7.5.0-2019.12-x86_64_arm-eabi.tar.xz ↵

```

**① Info:**

Downloading the GCC toolchain takes time due to the large file size.

\* At the "SoC Startup Trial Seminar" held in our company, it will be set up beforehand.

---

**3. Set environment variables to use the bare metal GCC toolchain.**

Run the following command in the **Ubuntu 18.04 LTS terminal**:

```

$ export PATH=~/toolchains/gcc-linaro-7.5.0-2019.12-x86_64_arm-eabi/bin:$PATH ↵

$ export ARCH=arm ↵

$ export CROSS_COMPILE=arm-eabi- ↵

```

## 4-4. Step 4: Build Preloader

Generate the bsp project needed to generate Preloader from the Quartus® Prime design handoff information (hps\_isw\_handoff\$\soc\_system\_hps\_0).

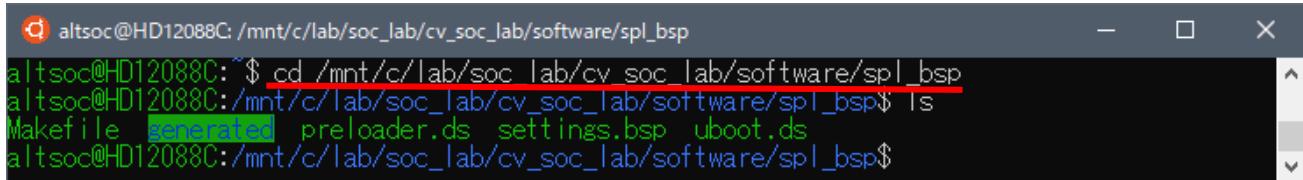

1. Change the current directory in the Ubuntu 18.04 LTS terminal to the bsp project directory.

```

$ cd /mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

```

```

altsoc@HD12088C: /mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

altsoc@HD12088C:~$ cd /mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp$ ls

Makefile generated preloader.ds settings.bsp uboot.ds

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp$

```

Figure 4-4. Navigate to the bsp project directory

2. Download and unpack the U-Boot/Preloader source tree under the bsp project directory. Run the following command in your Ubuntu 18.04 LTS terminal:

```

$ wget https://github.com/altera-opensource/u-boot-

socfpga/archive/ACDS20.1STD_REL_GSRD_PR.tar.gz

$ tar -xzvf ACDS20.1STD_REL_GSRD_PR.tar.gz

$ mv u-boot-socfpga-ACDS20.1STD_REL_GSRD_PR/ uboot-socfpga

```

① Info:

If wget is not available, such as when working offline, use the downloaded source tree. Instead, use the following command to copy and unpack the U-Boot/Preloader source tree:

```

$ tar -xzvf /mnt/c/lab/soc_lab/cv_soc_lab/solution/uboot-

socfpga/ACDS20.1STD_REL_GSRD_PR.tar.gz

$ mv u-boot-socfpga-ACDS20.1STD_REL_GSRD_PR/ uboot-socfpga

```

\*For the “SoC Startup Trial Seminar” in our company, follow these steps.

3. Navigate directly to the Uboot-socfpga source tree and run qts-filter.sh.

```

$ cd uboot-socfpga

$ ./arch/arm/mach-socfpga/qts-filter.sh

cyclone5 ../../../../ ./board/altera/cyclone5-socdk/qts/

```

This action populates the various header files generated by bsp-create-settings below the uboot-socfpga source tree.

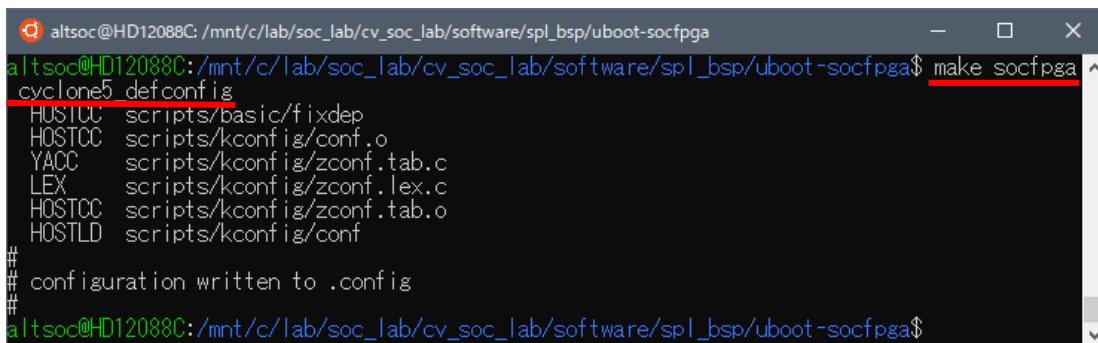

4. Configure the U-Boot/Preloader source tree for the Cyclone V SoC target.

```

$ make socfpga_cyclone5_defconfig

```

```

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp/uboot-socfpga

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp/uboot-socfpga$ make socfpga_cyclone5_defconfig

HOSTCC scripts/basic/fixdep

HOSTCC scripts/kconfig/conf.o

YACC scripts/kconfig/zconf.tab.c

LEX scripts/kconfig/zconf.lex.c

HOSTCC scripts/kconfig/zconf.tab.o

HOSTLD scripts/kconfig/conf

#

## configuration written to .config

#

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp/uboot-socfpga$

```

Figure 4-5. Configuring the U-Boot/Preloader Source Tree

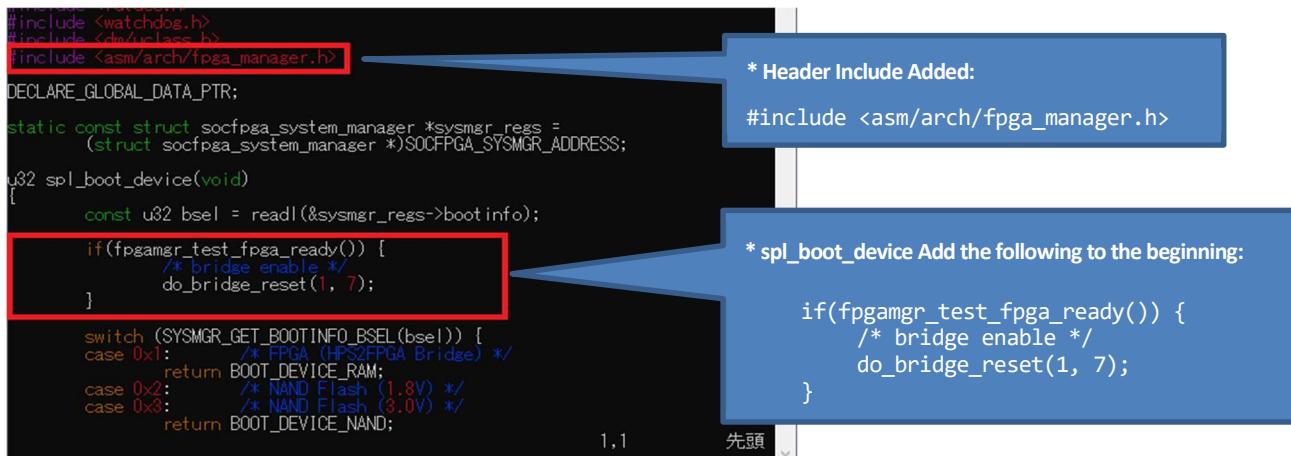

5. Rewrite part of the U-Boot/Preloader source tree for debugging.

Execute the following command in the **Ubuntu 18.04 LTS** terminal to edit in the **vi** editor.

After starting the editor, type the **i** key to enter the input mode. Rewrite the source according to the figure below.

After editing, press the **ESC** key once, then type **:wq** to save and exit.

① **Info:**

In the **vi** editor, you can search in the file by entering the / (slash) key followed by a search keyword while in normal mode. If you are in input mode (with – insert – or – INSERT – displayed at the bottom left of the window), press the **ESC** key once to enter normal mode.

If you cannot find the edit point in the source, use **/spl\_boot\_device** or **/socfpga\_sdram\_apply\_static\_cfg** to search in the file, referring to the information in the bubble below.

```

$ vi arch/arm/mach-socfpga/spl_gen5.c

```

```

#include <watchdog.h>

#include <dm/uclass.h>

#include <asm/arch/fpga_manager.h>

DECLARE_GLOBAL_DATA_PTR;

static const struct socfpga_system_manager *sysmgr_regs =

(struct socfpga_system_manager *)SOCFPGA_SYSMGR_ADDRESS;

u32 spl_boot_device(void)

{

const u32 bsel = readl(&sysmgr_regs->boot_info);

if(fpgamgr_test_fpga_ready()) {

/* bridge enable */

do_bridge_reset(1, 7);

}

switch (SYSMGR_GET_BOOTINFO_BSEL(bsel)) {

case 0x1: /* FPGA (HPS2FPGA Bridge) */

return BOOT_DEVICE_RAM;

case 0x2: /* NAND Flash (1.8V) */

case 0x3: /* NAND Flash (3.0V) */

return BOOT_DEVICE_NAND;

}

```

\* Header Include Added:

```

#include <asm/arch/fpga_manager.h>

```

\* **spl\_boot\_device** Add the following to the beginning:

```

if(fpgamgr_test_fpga_ready()) {

/* bridge enable */

do_bridge_reset(1, 7);

}

```

Figure 4-6. Edit Arch/arm/mach-socfpga/spl\_gen5.c

Figure 4-7. Edit Arch/arm/mach-socfpga/misc\_gen5.c

**Info:**

This source code edit adds processing to open the bridge interface between the HPS-FPGA during Preloader. It adds processing equivalent to what is normally done with the bridge enable command when running U-Boot.

## Reference:

Macnica Altera FPGA Insights "[U-Boot HPS-FPGA Bridge Open Command for SoC FPGAs](#)"

6. Build the source tree and generate the U-Boot and Preloader.

```

$ make -j 24

```

```

altsoc@HD12088C:/mnt/c/lab/soc_lab/cv_soc_lab/software/spl_bsp/uboot-socfpga$ make -j 24

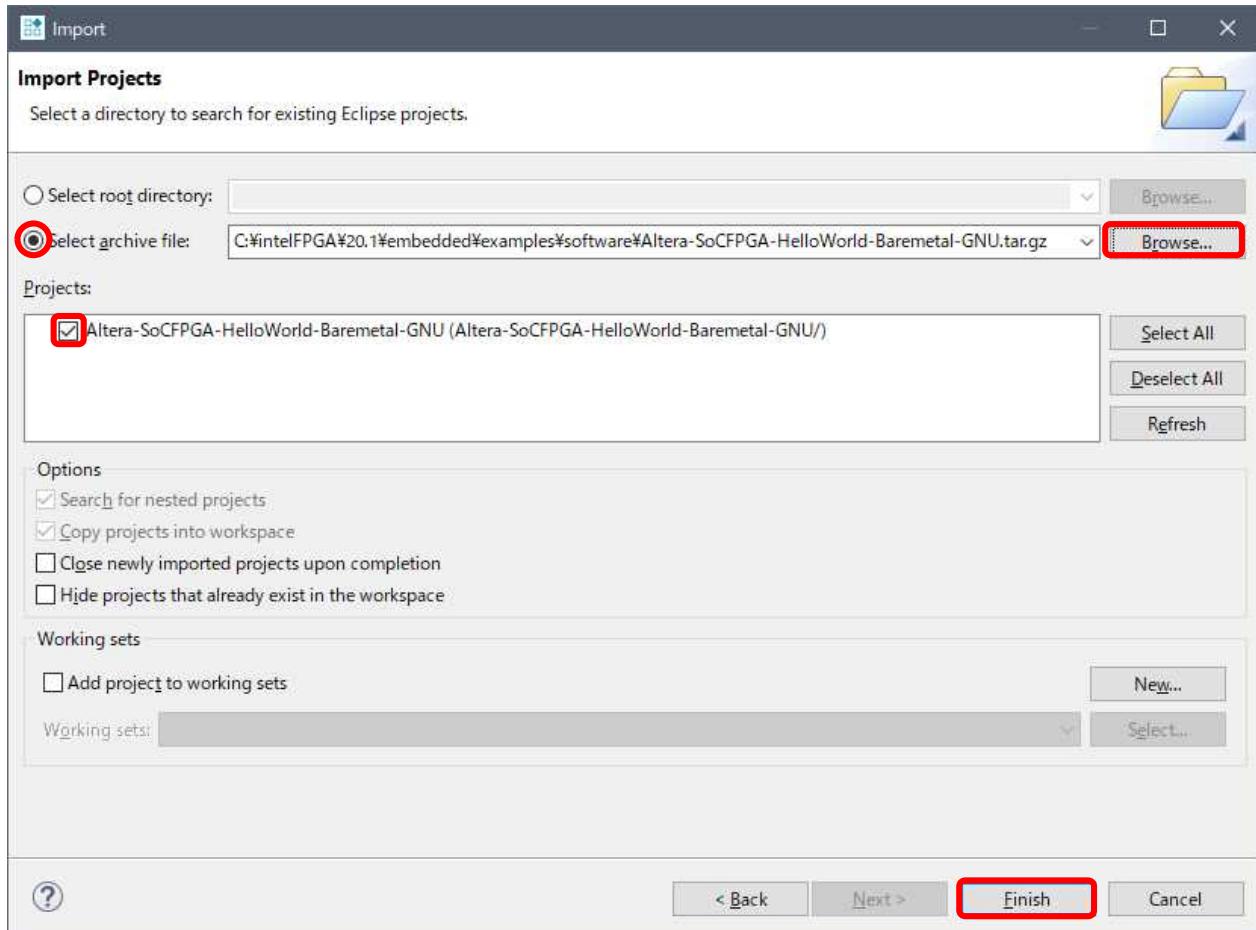

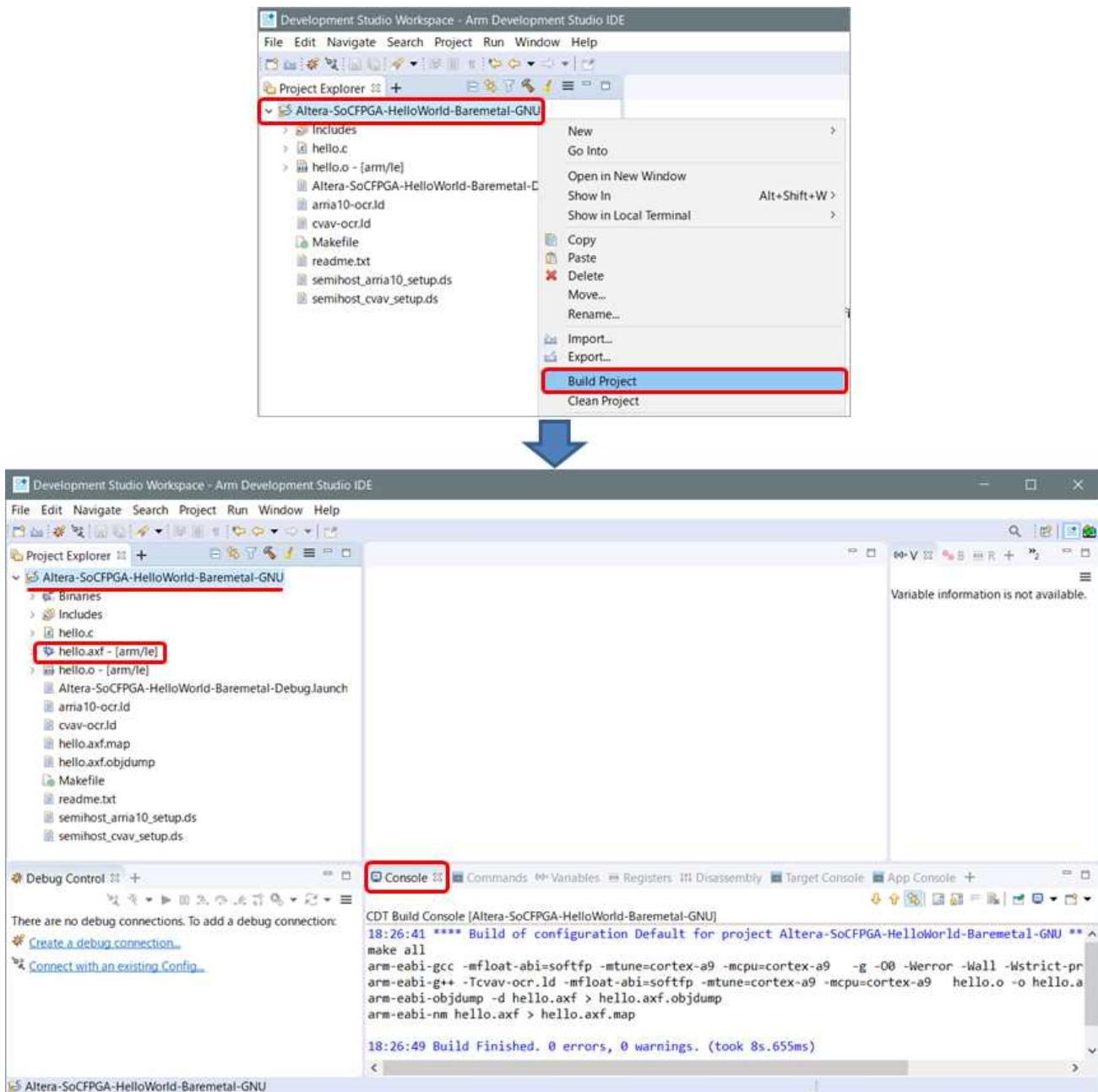

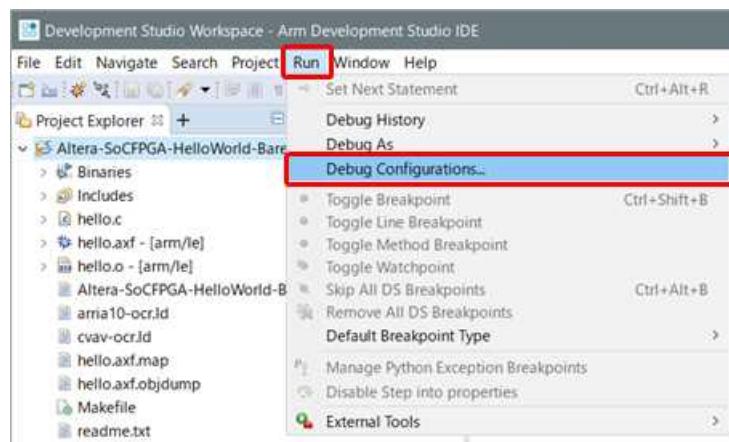

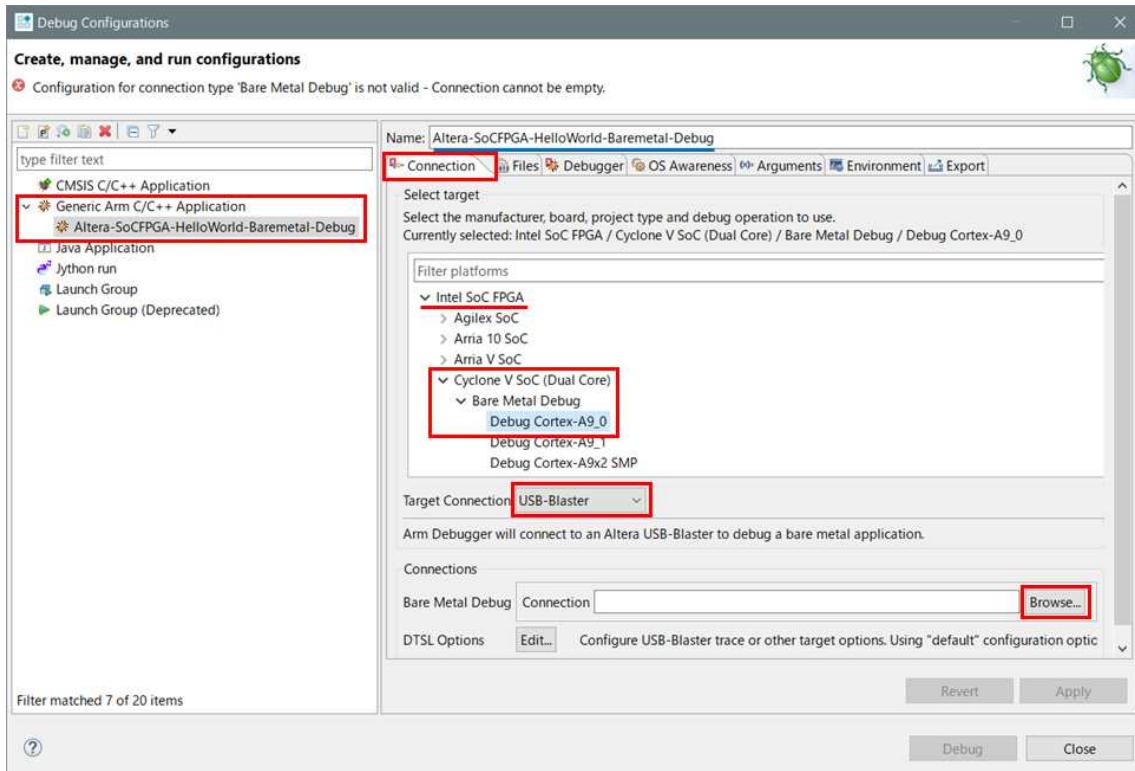

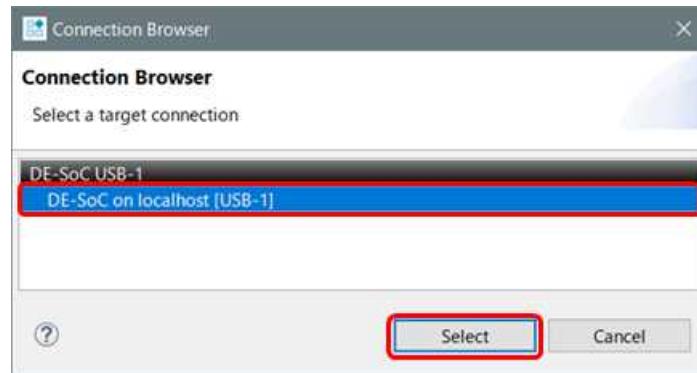

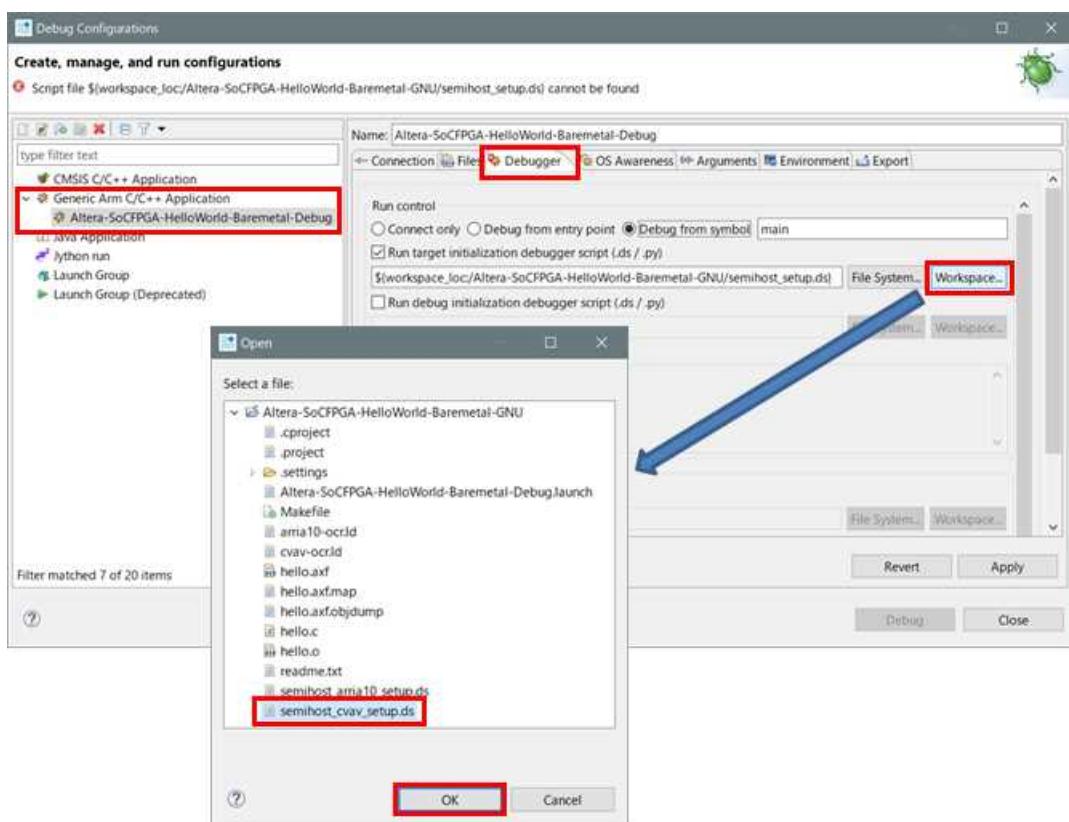

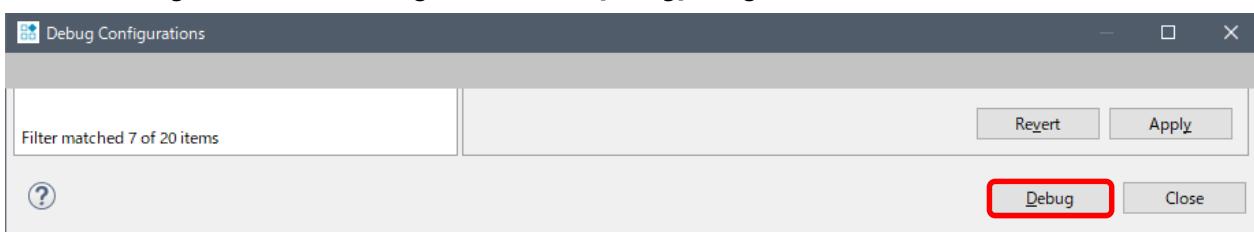

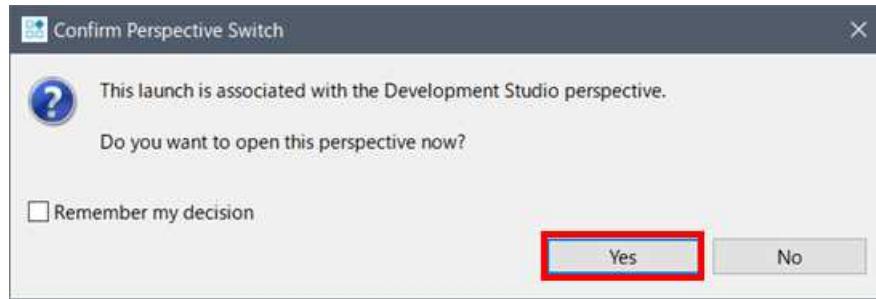

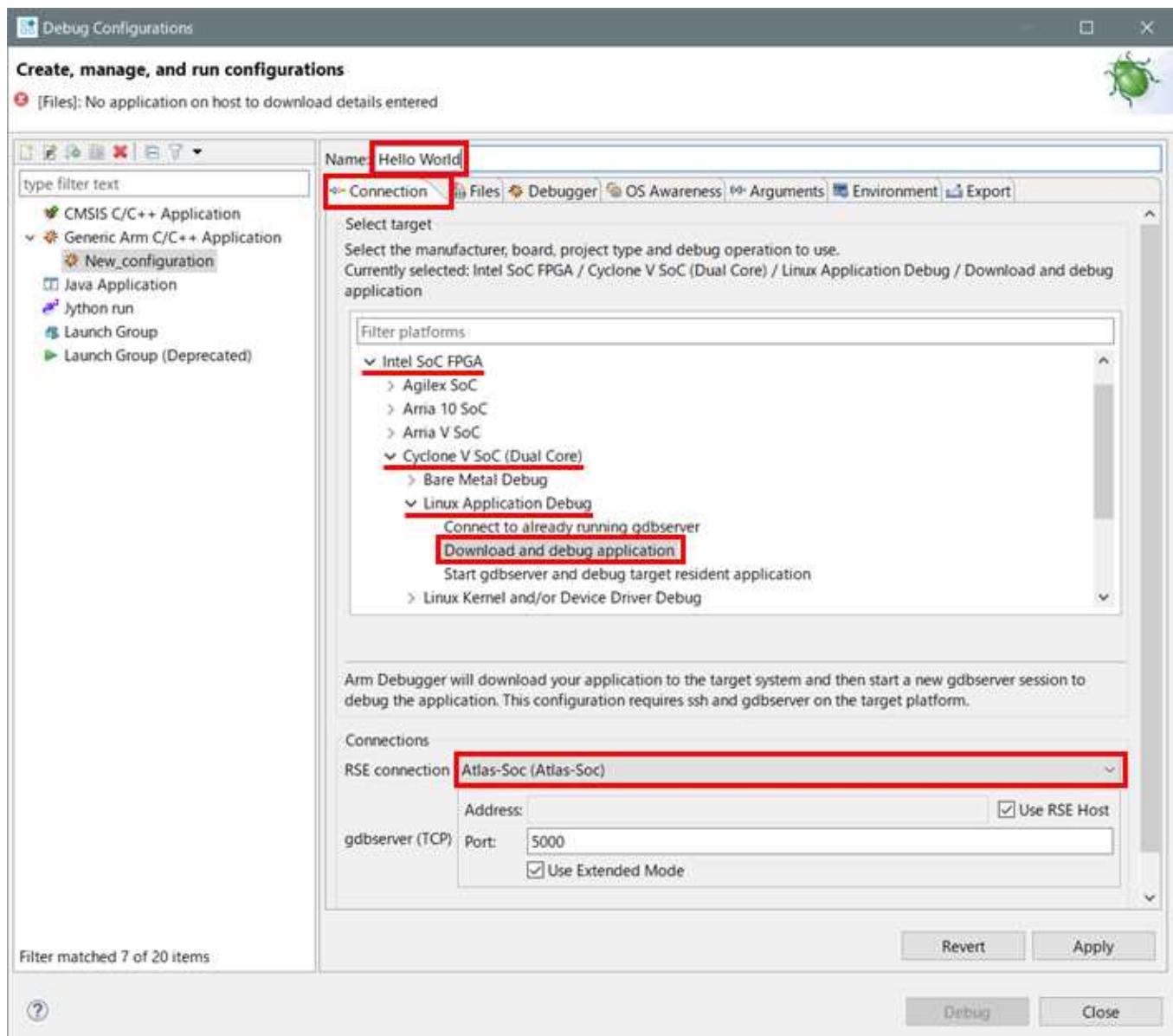

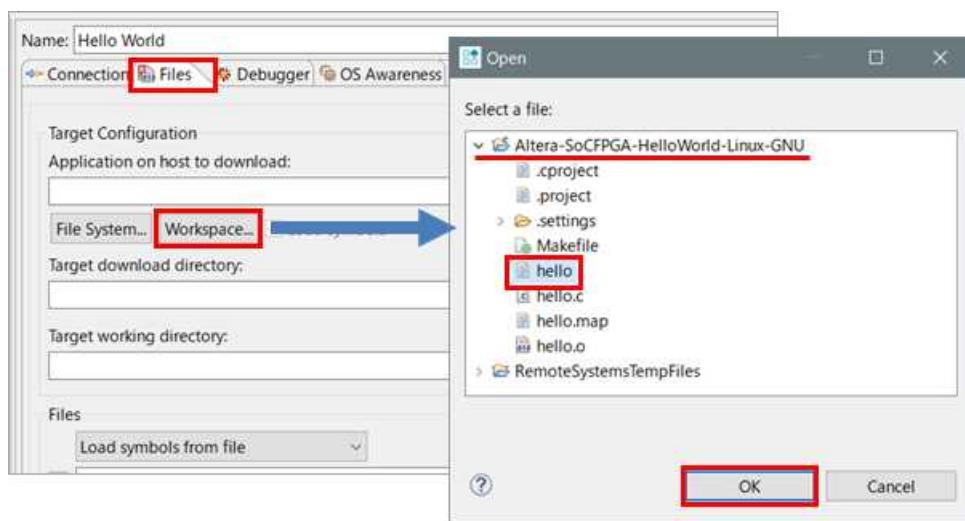

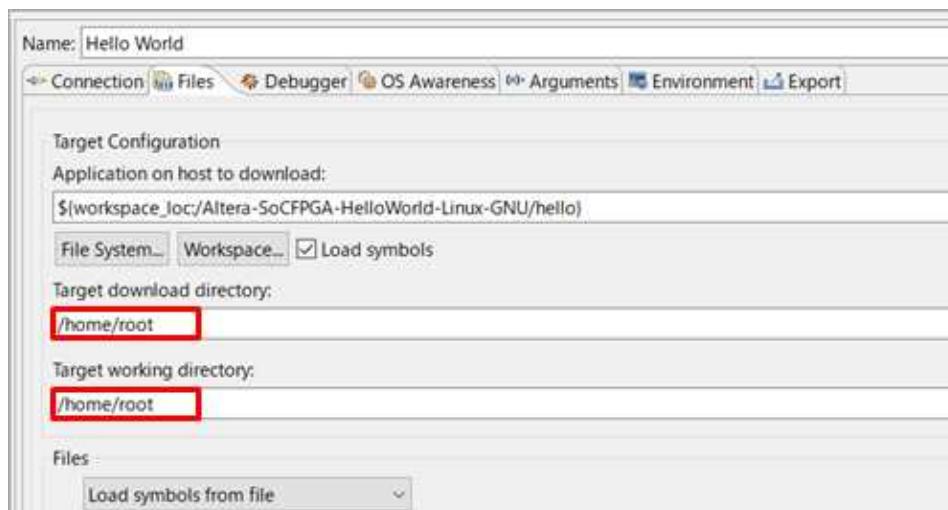

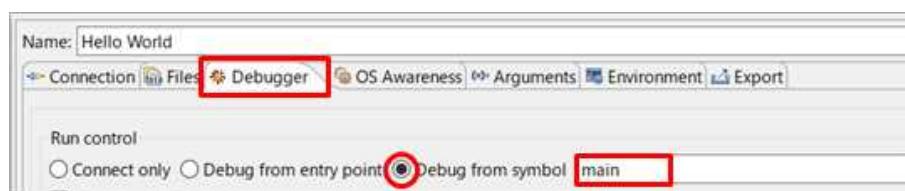

scripts/kconfig/conf --syncconfig Kconfig