# Quartus Prime はじめてガイド ピン・アサインの方法

ver.15.1

# Quartus Prime はじめてガイド ピン・アサインの方法

# <u>目次</u>

| 1. | はじめ                     | IZ                           |  |  |  |  |

|----|-------------------------|------------------------------|--|--|--|--|

| 2. | 事前作                     | 事前作業4                        |  |  |  |  |

|    | 2-1.                    | デバイスの選択4                     |  |  |  |  |

|    | 2-2.                    | データベースの構築4                   |  |  |  |  |

| 3. | ユーザ                     | ・I/O ピンのアサイン方法5              |  |  |  |  |

| 4. | 未使用ユーザ I/O ピンの属性設定方法10  |                              |  |  |  |  |

| 5. | コンパ                     | イル後の確認11                     |  |  |  |  |

| 6. | Live I/O Checking       |                              |  |  |  |  |

| 7. | I/O Assignment Analysis |                              |  |  |  |  |

| 8. | その他の機能15                |                              |  |  |  |  |

|    | 8-1.                    | Back-Annotate Assignments 15 |  |  |  |  |

|    | 8-2.                    | CSV ファイル                     |  |  |  |  |

|    | 8-2-1. CSV ファイルのエクスポート  |                              |  |  |  |  |

|    | 8-2-2. ピン制約情報の編集16      |                              |  |  |  |  |

|    | 8-2-3                   | 3. CSV ファイルのインポート17          |  |  |  |  |

|    | 8-3.                    | Show Fitter Placement        |  |  |  |  |

|    | 8-4.                    | Pad View ウィンドウ               |  |  |  |  |

| ᇔ  | 7 屠 麻                   | 20                           |  |  |  |  |

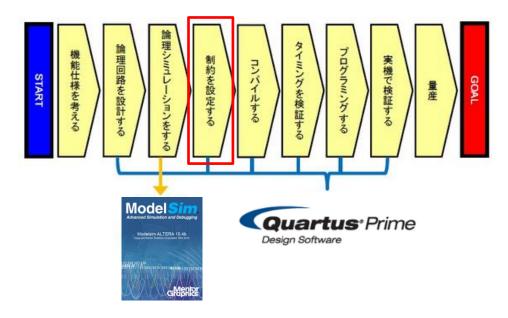

# 1. はじめに

この「Quartus Prime はじめてガイド」シリーズは、Quartus® Prime 開発ソフトウェアを初めてご利用になるユー ザ向けの資料です。

この資料は、Quartus Prime 開発ソフトウェアにおけるデバイスのピン・アサイン設定に関して説明しています。

主に、ユーザ回路のピンを Pin Planner を用いて、ターゲット・デバイスのピン番号に割り当てる(アサインする) 方法を紹介します。また、ピンの I/O 規格の設定方法や未使用ユーザ I/O ピンの属性を個々のピンに設定する 方法(個別設定)も案内しています。

その他、コンパイル・レポートの確認方法や便利な機能も紹介します。ピン・アサインを行う際にご覧ください。

# 2. 事前作業

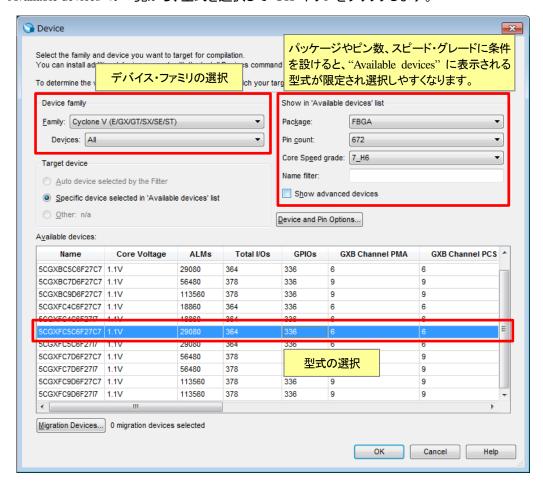

#### 2-1. デバイスの選択

ピンをアサインするためには、ターゲット・デバイスを決定する必要があります。デバイスの型式を設定していない場合は、以下の作業を行ってください。(既に型式を指定している場合は、この作業は不要です。)

- ① Assignments メニュー ⇒ Device を選択します。

- ② Family リストより、指定するデバイス・ファミリ名を選択します。

- ③ Target device 内において、"Specific device selected in 'Available devices' list" を選択します。

- ④ Available devices の一覧から、型式を選択して OK ボタンをクリックします。

#### 2-2. データベースの構築

ピンをアサインする前にデザイン情報を作成しておくと、Pin Planner の All Pins リスト上に自動的にピン名が表示されるので、とても便利です。以下の何れかの操作を実行してください。(実行時間が短いので、<u>推奨は Start Analysis & Elaboration です。</u>また、すでに実行済みの場合は、この作業は不要です。)

- Processing メニュー ⇒ Start ⇒ Start Analysis & Elaboration (お勧め度:高)

- Processing メニュー ⇒ Start ⇒ Start Analysis & Synthesis (お勧め度:中)

- Processing メニュー ⇒ Start Compilation (お勧め度:低)

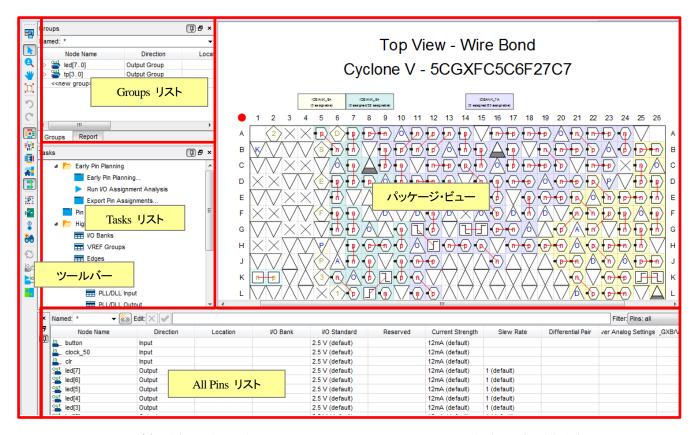

# 3. ユーザ I/O ピンのアサイン方法

Pin Planner を用いてデザイン内のピンを目的のピン番号へアサインする方法を紹介します。同時に、アサインし たピンの I/O Standard の設定方法も紹介します。なお、この操作は「第2章 事前作業」を実行していることを前提 にしています。

- ① Pin Planner を起動します。以下の何れかの方法で起動してください。

- Assignments メニュー ⇒ Pin Planner を選択

- ツールバーの 🍑 ボタンをクリック

※ Groups リストが表示されていない場合は、View メニュー ⇒ Groups List にチェックを入れると表示されます。

#### 【補足①: パッケージ・ビューの表示設定】

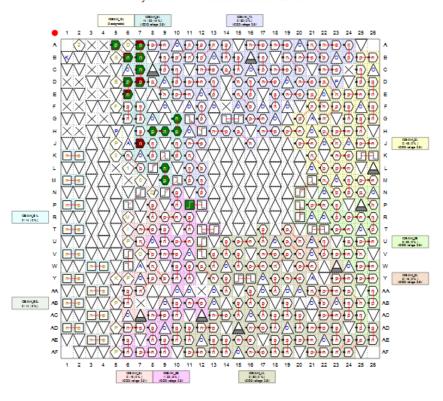

#### シンボルの説明

Pin Planner に表示されるシンボルは、Pin Legend Window の情報を 参照してください。

- View メニュー ⇒ Pin Legend Window

- ツールバーの 🧯 ボタンをクリック

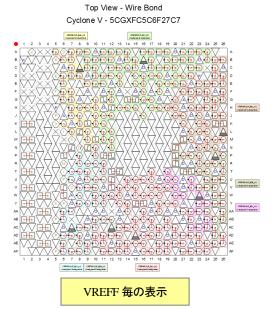

#### カラー表示

- I/O バンク毎に表示させる場合

- View  $\angle \neg \neg \Rightarrow Show \Rightarrow Show I/O Banks$

- ツールバーの 🏥 ボタンをクリック

- VREFF グループ毎に表示させる場合

- View メニュー ⇒ Show → Show VREFF Groups

- ツールバーの 👯 ボタンをクリック

<u>差動ピンのペア表示</u>

- *View*  $\nearrow = \neg \Rightarrow$  *Show*  $\Rightarrow$  *Show Differential Pin Pair Connections*

- ツールバーの 📮 ボタンをクリック

I/O バンク毎の表示

12mA (default)

12mA (default)

12mA (default)

led[3]

led[2]

out led[1]

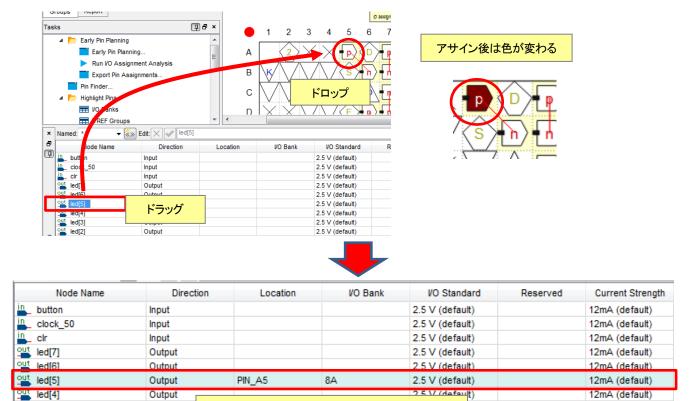

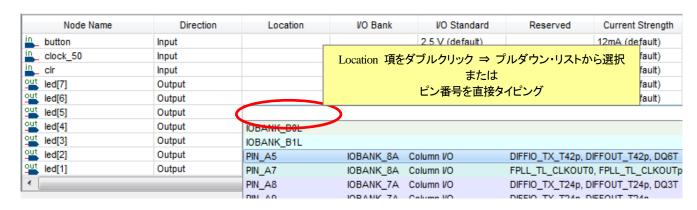

② ピンを目的の番号へアサインします。1 ピンずつ設定する方法とグループ単位で設定する方法があります。

#### ◆ 1 ピンずつ設定する方法

Output

Output

Output

All Pins リストからピン名を選択し、ドラッグ & ドロップでパッケージ・ビュー上の配置したいピンまで移動させます。

その他、All Pins リストのスプレッド・シートの Location 項をダブルクリックし、プルダウン・リストから選択する方法でも設定可能です。(番号を直接タイプすることでも設定可能です。)

z.o v ruerault)

2.5 V (default)

アサインされた情報が All Pins リストにも反映される

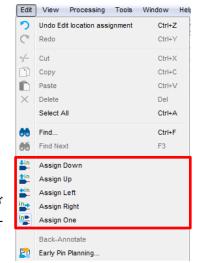

#### ◆ グループ単位で設定する方法

バス信号は自動でグループ化されます。Groups リストからアサインしたいピンを複数選択し、ドラッグ & ドロップでパッケージ・ビュー上の配置したいピン番号まで移動させます。

複数ピンに対してピン・アサインを一括で行う場合、Edit メニュー内で以下の設定を行うことにより配置方向を変えることができます。

Assign Down ・・・・・・ 指定したピンを上から順番に並べて配置

Assign Up ・・・・・・・ 指定したピンを下から順番に並べて配置

Assign Left ・・・・・・・ 指定したピンを左から順番に並べて配置

Assign Right ・・・・・・ 指定したピンを右から順番に並べて配置

Assign One\* ・・・・・・ 指定したピンを 1 つずつ配置

※ メンバーに登録された順番(上から)で、アサインされます。そのピンのアサインが 完了すると、次のメンバーのピン名がカーソルに表示されます。メンバーの一番下 のピン名のアサインが完了するまで、連続でアサインすることができます。

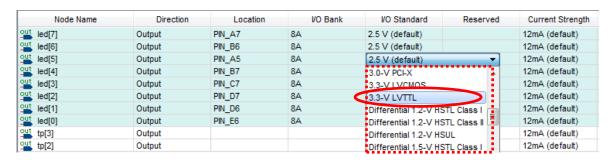

③ I/O Standard を設定します。デフォルトでデバイスのすべてのユーザ I/O に設定した I/O Standard (I/O Standard の全体設定)が表示されています。変更がある場合は、グループ・リスト、または All Pins リストの I/O Standard 欄をダブルクリックし、プルダウン・リストより選択します。

上記②~③の操作を繰り返して他のピンのアサインを行っていきます。

※ I/O Standard の全体設定は、Device & Pin Options ダイアログ・ボックス内 Voltage タブで行います。操作方法に関しては、 本資料を入手したサイト内から以下の資料をご覧ください。

『Quartus Prime はじめてガイド - デバイス・オプションの設定方法』

- ④ コンパイルを実行します。何れかの操作で実行してください。

- Processing メニュー ⇒ Start Compilation を選択

- ボタンをクリック

- ※ コンパイル実行することなくピンの適合性を確認する場合は、『第 6 章 Live I/O Checking』や『第 7 章 I/O Assignment Analysis』をご覧ください。

#### 【補足② : ピン・オプション】

デザイン内のピン・オプションを設定する場合は、Pin Planner の All Pins リスト上で設定することができます。Assignment Editor でも設定できますが、Pin Planner で設定することを推奨しています。

※ ピン・オプションの設定や Assignment Editor を使用した制約の方法に関しては、本資料を入手したサイト内から以下の資料をご覧ください。

『Quartus Prime - よく使用するピン・オプションの設定方法』

『Quartus Prime - 制約の方法(Assignment Editor)』

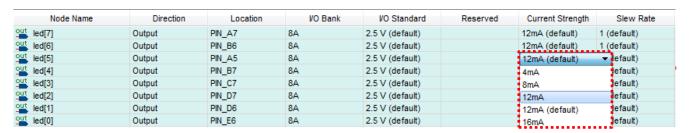

#### 例)Current Strength (出力電流値)を Pin Planner で設定する場合

All Pins リスト内において、オプションを設定するピンの Current Strength 項をダブルクリックします。以下のように、表示されたプルダウン・リストから出力電流値を選択します。(この設定は、Assignment Editor に反映されます。)

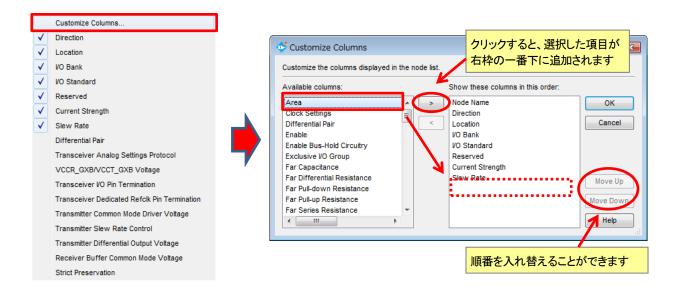

なお、カラムを追加したい場合は、All Pins リスト内において、マウスで右クリックして、表示させたいカラムにチェックを 入れます。

または、All Pins リスト内において、マウスで右クリック ⇒ Customize Columns を選択し、Customize Columns ダイアロ グ・ボックスの "Available columns" (左枠)から追加したいカラムを選択し、 ⇒ をクリックします。"Show these columns in this order" (右枠)に登録されたことを確認後、OK をクリックします。

### 4. 未使用ユーザ I/O ピンの属性設定方法

基板上で周辺のデバイスと FPGA や CPLD のピンを接続する場合、未使用のユーザ I/O ピンに対して基板の環境に応じた属性を設定(リザーブ・ピン設定)しなければなりません。そのような場合、デザイン上にリザーブ・ピンを作らずに、Quartus Prime 開発ソフトウェアのオプション設定だけで未使用 I/O ピンの属性を設定することが可能です。

操作は、デバイスの該当するピン全てに設定する"全体設定"と、特定のピンに対して個々に設定する"個別設定"があります。まず全体設定を行った後、それとは異なる属性を希望するいくつかのピンに対し個別設定で変更することをお勧めします。なお、全体設定と個別設定では、個別設定が優先されます。

※ リザーブ・ピン(未使用ユーザ I/O ピンの属性指定)の全体設定に関しては、本資料を入手したサイト内から以下の資料を ご覧ください。

『Quartus Prime はじめてガイド - デバイス・オプションの設定方法』

個別設定の方法は、以下のとおりです。

- ① Assignments メニュー ⇒ Pin Planner を選択します。

- ② All Pins リスト内の Node Name 欄の <<new node>> をダブルクリックし、リザーブ・ピン用に任意の名前を付けます。(デザイン上に存在しない名前にしてください。)

- ③ ドラッグ & ドロップでパッケージ・ビュー上の目的のピン番号まで移動、または Location 欄のプルダウン・リストにてピン番号を選択します。

- ④ I/O 規格に変更がある場合は、I/O Standard 欄をダブルクリックし、プルダウン・リストより選択します。(アサインするバンクの VCCIO により、変更が必要な場合があります。)

- ⑤ Reserved 欄をダブルクリックし、プルダウン・リストより、属性を選択します。(デバイスにより設定項目が変わります。)

• As SignalProbe output : SignalProbe 用の出力ピンとして予約されます。

• As bidirectional : ピンは双方向ピンとして予約されます。

As input tri-statedピンは入力ピンとして予約され、トライ・ステート処理されます。

• As output driving ground : ピンは出力ピンとして予約され、GND(Low)を出力します。

As output driving an unspecified signal : ピンは出カピンとして予約され、未定義の値を出力します。

As output driving VCCピンは出力ピンとして予約され、VCC(High)を出力します。

個別設定を行うリザーブ・ピンが複数ある場合には、上記の操作を繰り返してリザーブ・ピンの個別設定を 行います。

⑥ 設定終了後、コンパイルを実行します。

# 5. コンパイル後の確認

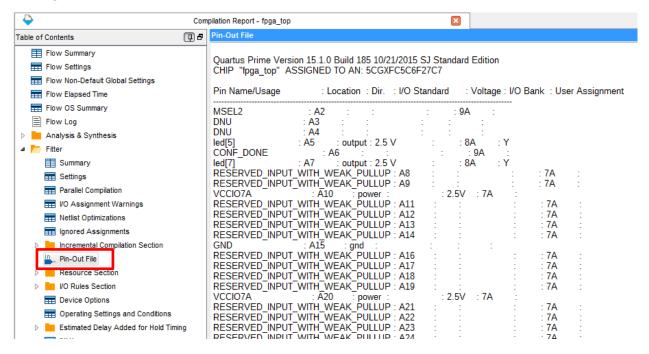

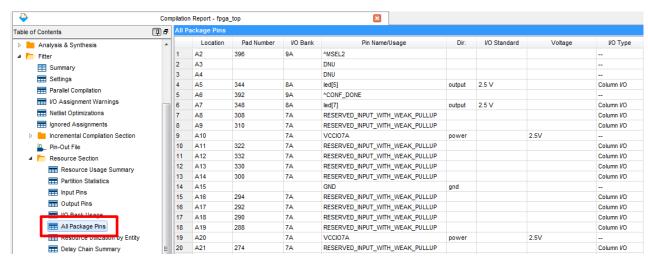

コンパイル(配置配線)後のピン・アサインの確認は、コンパイル・レポートで確認できます。確認方法は、<u>すべて</u>のピン情報を確認する方法とデザイン上に存在するピンだけを確認する方法の 2 通りがあります。

#### ◆ すべてのピン情報を確認する方法

- コンパイルを完了させます。

- ② Processing メニュー ⇒ Compilation Report を選択します。(コンパイル終了後に、自動で起動します。)

- ③ Fitter レポート・ディレクトリ ⇒ Pin-Out Fie より確認します。(テキスト・ベースで表示)

または、Fitter レポート・ディレクトリ ⇒ Resource Section ⇒ All Package Pins より確認します。(スプレッド・シートで表示)

ver. 15.1 2016 年 2 月 11/20 ALTIMA Corp. / ELSENA,Inc.

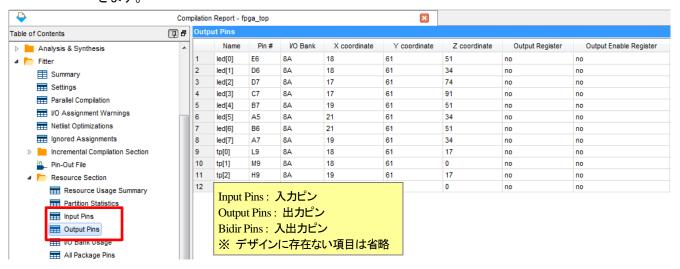

#### デザイン上に存在するピンだけを確認する方法

- コンパイルを完了させます。

- ② Processing メニュー ⇒ Compilation Report を選択します。(コンパイル終了後に、自動で起動しま

- ③ Fitter レポート・ディレクトリ ⇒ Resource Section ⇒ Input Pins / Output Pins / Bidir Pins から確認で

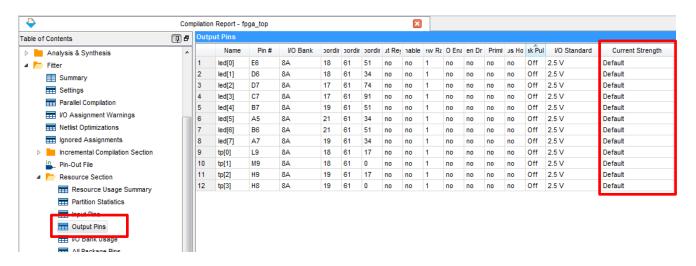

#### 【補足③: ピン・オプションの確認方法】

ピン・オプション(補足②参照)の適用結果は、コンパイル・レポートより確認することができます。 Compilation Report ⇒ Fitter ⇒ Resource Section ⇒ Input Pins / Output Pins / Bidir Pins のレポート内の各 項をご覧ください。

例)Current Strength (出力電流値)の適用性を確認する

Compilation Report ⇒ Fitter ⇒ Resource Section ⇒ Output Pins または Bidir Pins を選択し、レポート内の各ピンに対 する Current Strength 項より確認できます。

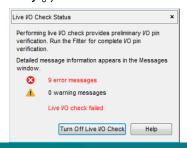

### 6. Live I/O Checking

※ Live I/O Checking 機能は、Stratix® IV と Arria® II、Cyclone® IV、MAX® 10、MAX V、MAX II デバイスで サポートしています。

この機能は、ユーザがアサインした I/O ピンの配置がアルテラ FPGA や CPLD のピン・ガイドライン・ルール に適合しているかどうかを、ピン制約を設定したと同時に Pin Planner 上で簡易チェックします。例えば電圧の異なるピンが同一バンクに混在していた場合や、差動信号とシングル信号の位置関係(パッドの間隔)など、I/O ルールに則ってアサインされているかをフル・コンパイルすることなく(但し、事前に Analysis & Synthesis の実行は必須)確認できるため、I/O 規格を多く使用するユーザには有効的な機能です。もし、適さないアサインがあった場合には、リアル・タイムにエラー・メッセージやワーニング・メッセージを表示します。メッセージは Pin Planner の Message ウィンドウ、Quartus Prime 開発ソフトウェアの Message ウィンドウにそれぞれ表示されます。

なお、Live I/O Checking 実行後は、最終的な I/O 適合検証機能である I/O Assignment Analysis を実行する必要があります。操作は『第 7 章 I/O Assignment Analysis』をご参照ください。

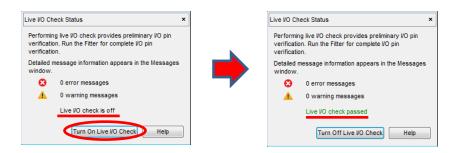

Live I/O Checking の操作は以下のとおりです。

- ① Processing メニュー ⇒ Start → Start Analysis & Synthesis を実行します。

- ※ すでに実行している場合には、この操作は不要です。

- ② Assignments メニュー ⇒ Pin Planner を選択します。

- ③ View メニュー ⇒ Live I/O Check Status Window を表示させます。

- ④ ウィンドウ内の Turn On Live I/O Check ボタン、または Pin Planner 内ツールバーの Enable Live I/O Check ボタン 峰 をクリックし、ピン・アサインのチェックを実行します。

- ⑤ ユーザ I/O ピンのアサイン(番号の割り当て、I/O 規格の設定)や未使用ユーザ I/O ピンの属性などの設定を行います。I/O ルールに違反していなければ、上右図のように "Live I/O check passed" と表示されます。

- ⑥ I/O ルールに違反していた場合には、Live I/O Check Status ウィンドウにエラーまたはワーニング・メッセージ 数が表示され、Pin Planner(または Quartus Prime 開発ソフトウェア)の Message ウィンドウに内容が表示され ます。(問題を回避するためにメッセージを確認し、ピンのレイアウトや I/O 規格などを変更する必要があります。)

```

Type ID Message

169026 Pin led[0] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[1] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[2] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[3] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[4] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[5] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[6] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

169026 Pin led[7] with I/o standard assignment 2.5 V is incompatible with I/o bank 8. I/

168002 Live I/o check failed

```

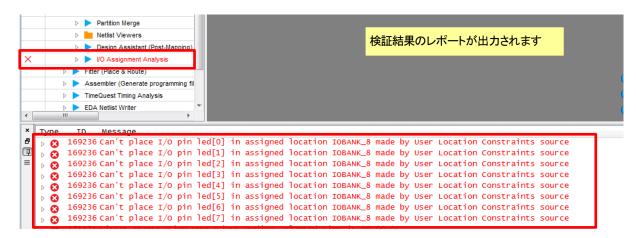

# 7. I/O Assignment Analysis

Live I/O Checking でエラーがなくなったら、最終的な I/O の検証を行います。この機能は、フル・コンパイルを実行することなく、全ユーザ I/O ピンの制約に対する適合性をチェックします。I/O Assignment Analysis は Live I/O Checking よりも多くの内容をチェックするため、Live I/O Checking の検証後に実行することを推奨します。また、最終的にはコンパイルを実行してください。

基本使用フローは以下のとおりです。

- ① 事前に Live I/O Checking において、ピン・アサインの適合性を確認しておきます。

- ② Processing メニュー ⇒ Start ⇒ Start I/O Assignment Analysis を実行します。

エラーやクリティカル・ワーニングがなければ、ピン制約は適合しています。もしエラーが発生した場合は、メッセージを確認し、ピンのレイアウトや I/O 規格などを変更する必要があります。メッセージは Pin Planner(または Quartus Prime 開発ソフトウェア)のメッセージ・ウィンドウに表示されます。

# 8. その他の機能

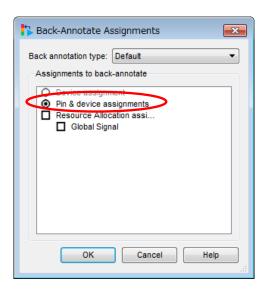

#### 8-1. Back-Annotate Assignments

ユーザが最初からピン・アサインせずコンパイルを実行した場合、Quartus Prime 開発ソフトウェアのコンパイラは自動的にピンの配置を決定します。そのピン配置結果をユーザのピン制約に反映させることが可能です。その場合は Back-Annotate Assignments 機能を活用します。これは、コンパイル後のセルやピンの配置結果をQuartus Prime 開発ソフトウェアの設定ファイル(.qsf ファイル)へ反映させる機能です。

操作方法は以下のとおりです。

- ① コンパイルを実行し、ピンを自動で配置させます。

- ② コンパイル後のピン配置情報を Quartus Prime 開発ソフトウェアの設定ファイル(.qsf ファイル)へ反映させます。

- Assignments メニュー ⇒ Back-Annotate Assignments

- ③ Pin & device assignments にラジオ・ボタンを設定し、OK ボタンをクリックします。

- ④ Assignments メニュー ⇒ Pin Planner を選択します。デザイン内のピンが Quartus Prime 開発ソフトウェアのコンパイラにより自動的に配置されていることが確認できます。

- ⑤ ピン番号または I/O 規格において、変更したい内容の修正を行います。

- ⑥ 修正した内容を適応させるため、Live I/O Checking と I/O Assignment Analysis、コンパイルを実行します。

#### 8-2. CSV ファイル

Quartus Prime 開発ソフトウェアのピン制約は、CSV(カンマ区切り)ファイルに対応しています。Pin Planner の情報をエクスポートしたり、あらかじめ作成しておいた CSV ファイルをインポートしたりすることができます。CSV ファイルをインポートする場合は、カラム見出しのロウは決められた表記でなければならないため、Pin Planner 上から一度 CSV ファイルをエクスポートして雛形を作成し、それにアサイン情報を入力(編集)した後に、再びインポートすることを推奨しています。(表記ルールに反すると、Quartus Prime 開発ソフトウェアが内容を認識しません。)

ここでは、ピン・アサインにおいて CSV ファイルを活用するときの推奨の手順を紹介します。

※ この操作でピンをアサインする場合には、「第2章事前作業」を行う必要があります。

#### 8-2-1. CSV ファイルのエクスポート

Pin Planner から CSV ファイルを出力します。

- ① Assignments メニュー ⇒ Pin Planner を選択します。

- ② File メニュー ⇒ Export より、出力するディレクトリ先と保存するファイル名を指定し、Export ボタンをクリックします。この時、拡張子が .csv であることを確認します。

#### 8-2-2. ピン制約情報の編集

Pin Planner から CSV ファイルを出力します。

① Microsoft® 社の Excel などを活用し、保存した CSV ファイルを開きます。

| То                  | Direction | Location | I/O Book   | I/O Standard   | Reserved | Current Streng |

|---------------------|-----------|----------|------------|----------------|----------|----------------|

|                     | _         | LUCATION | 17 O Dalik | 17 O Stariuaru | Reserveu | Ourient Stieng |

| altera_reserved_tck | Input     |          |            |                |          | .= / В Ш і     |

| altera_reserved_tdi | Input     |          |            |                | 7.       | ラム見出し          |

| altera_reserved_tdo | Output    |          |            |                |          |                |

| altera_reserved_tms | Input     |          |            |                |          |                |

| clk_in_one          | Input     | PIN_R20  | 5B         | 1.2-V HSUL     |          |                |

| leds[7]             | Output    | PIN_H9   | 8A         | 2.5 V          |          |                |

| leds[6]             | Output    | PIN_H8   | 8A         |                |          |                |

| leds[5]             | Output    | PIN_B6   | 8A         |                |          |                |

| leds[4]             | Output    | PIN_A5   | 8A         |                |          |                |

| leds[3]             | Output    | PIN_E9   | 8A         |                |          |                |

| leds[2]             | Output    | PIN_D8   | 8A         |                |          |                |

| leds[1]             | Output    | PIN_K6   | 8A         |                |          |                |

| <u></u>             | Output    | PIN_L7   | 8A         |                |          |                |

| イン上のピン              | Input     | PIN_AB24 | 5A         |                |          |                |

| SPAM AI17J          | Output    | PIN M24  | 6A         |                |          |                |

Ⅲ €

ブラウズ・ボタン

Categories..

Cancel Help

X

- ② CSV ファイルにおいて、必要な箇所にのみ情報を編集します。それ以外は空欄にします

- ◆ ピン番号を変更する場合は、Location 欄のピン番号を編集します。記述は以下のとおりです。

記述 : PIN\_番号 記述例: PIN\_E2

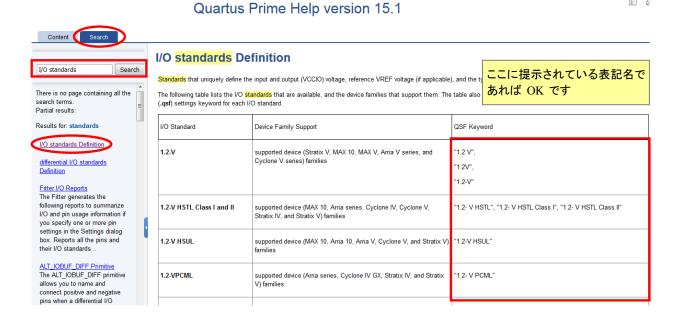

◆ I/O Standard を変更する場合は、I/O Standard 欄の規格名を編集します。記述は以下の通りです

記述例: SSTL-2 Class II

※ 各規格の記述名は、Assignment Editor または Pin Planner の I/O Standard に表示される表記を参考にしてくださいするか、 Help メニュー ⇒ Help Topics を選択すると Web ブラウザが起動するので、Search タブ内にキーワード "I/O standards" を 入力して検索してください。

③ アサイン情報を入力し終えたら、CSV ファイルを保存します。(ファイル・メニュー ⇒ 上書き保存)

#### 8-2-3. CSV ファイルのインポート

Quartus Prime 開発ソフトウェアにて、編集した CSV ファイルをインポートします。

- ① Assignments  $\mathcal{A} = \mathcal{A} \longrightarrow \text{Import Assignment}$ を選択します。

- ② Select File よりピン・アサイン情報を反映した い CSV ファイルを選択します。

- ③ OK ボタンをクリックします。

- ④ Pin Planner または Assignment Editor において設定が反映されていることを確認してください。

- Assignments メニュー ⇒ Pin Planner、または Assignments メニュー ⇒ Assignment Editor

🕥 Import Assignments

Specify the source and categories of assignments to import

Copy existing assignments into fpga\_top.qsf.bak before importing

- ⑤ 設定内容を適応させるため、コンパイルを実行します。

- Processing メニュー ⇒ Start Compilation

2016年2月 ver. 15.1 17/20 ALTIMA Corp. / ELSENA,Inc.

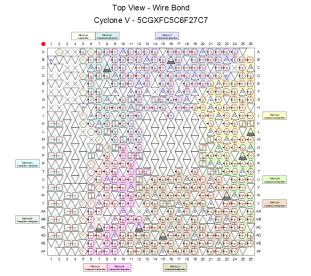

#### 8-3. Show Fitter Placement

Show Fitter Placements では、Quartus Prime 開発ソフトウェアの Fitter が決めたピン配置を Pin Planner 上で確認することができます。

- ① Show Fitter Placements を起動します。Pin Planner 上の View メニュー ⇒ Show ⇒ Show Fitter Placements、または、ツールバーにある をクリックします。Show Fitter Placements を起動するためには、Live I/O Checking を解除しなければなりません。

- ※ Live I/O Checking の詳細は、『第6章 Live I/O Checking』をご参照ください。

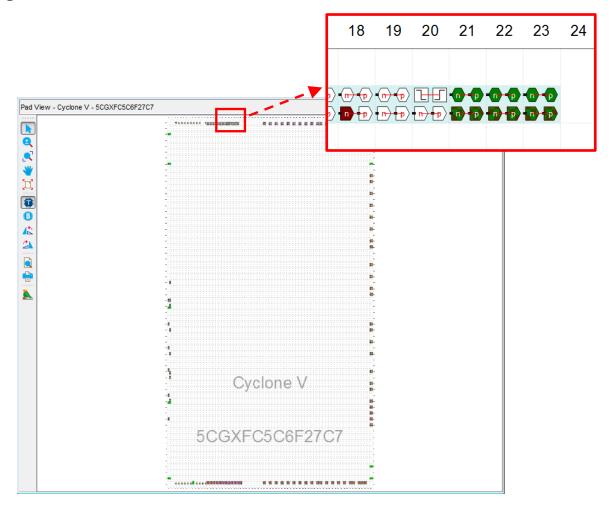

- ② パッケージ・ビューのピン表示が下記のように変化します。また左下に が表示され、Fitter が配置したピンが緑色で表示されます。

- \_ 0

- ・・・・・ ユーザが配置したピン(茶)

- Q ..... Fitter & ユーザが配置したピン(緑と赤の網目)

- **Q** ····· Fitter が配置したピン(緑)

Top View - Wire Bond Cyclone V - 5CGXFC5C6F27C7

#### 8-4. Pad View ウィンドウ

Quartus Prime 開発ソフトウェアでは、デバイスの信号品質(シグナル・インテグリティ)の問題をあらかじめ防止するために、ピン配置ルールにもとづき、ピン・アサインの妥当性を検証しています。(第 6 章 Live I/O Checking、第 7 章 I/O Assignment Analysis。) 例えば、シングル・エンド信号(入力 / 出力)ピンと差動信号ピンのパッド・ロケーション(間隔)には、"何パッド間隔を空けてアサインしなくてはならない" など制約があります。(パッドとは、デバイスのパッケージ・ピンが接続されているシリコン・ダイの接続部分のことです。)ユーザはピン番号を決める際、どのピン番号がどのパッド・ロケーションに割り当てられているのか把握することが重要です。

Pin Planner には、パッド・ロケーション用のビューワがあります。ピン配置ルールに沿ってピン番号を決める時や I/O Assignment Analysis 機能などにより、レイアウトのエラーが発生したときなどにご利用ください。

※ ピン配置ルールについては、各デバイスや Quartus Prime 開発ソフトウェアのハンドブックをご参照ください。

操作方法は、以下のとおりです。

- ① Pin Planner を起動

- ② Pin Planner 上の View メニュー ⇒ Pad View

# 改版履歴

| Revision | 年月      | 概要 |

|----------|---------|----|

| 1        | 2016年2月 | 初版 |

#### 免責およびご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、本資料を入手されました下記代理店までご一報いただければ幸いです。

株式会社アルティマ ホームページ: http://www.altima.co.jp 技術情報サイト EDISON:  $\underline{https://www.altima.jp/members/index.cfm}$ 株式会社エルセナ ホームページ: <a href="http://www.elsena.co.jp">http://www.elsena.co.jp</a> 技術情報サイト ETS :  $\underline{https://www.elsena.co.jp/elspear/members/index.cfm}$

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

- 5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる際は、各メーカ発行の英語版の資料もあわせてご利用ください。