# Quartus® Prime はじめてガイド TimeQuest によるタイミング解析の方法

Ver.17

## Quartus Prime はじめてガイド TimeQuest によるタイミング解析の方法

## <u>目次</u>

| 1.  | はじめに                               | 3   |

|-----|------------------------------------|-----|

| 2.  | コンパイル・レポートの確認                      | 4   |

|     | 2-1. 各フォルダの概要                      | 5   |

|     | 2-2. サマリ・レポートの概要                   | 6   |

|     | 2-3. 詳細レポート(パス・スラック・レポート)の生成       | 7   |

| 3.  | 詳細レポート                             | 9   |

|     | 3-1. 詳細レポートの概要                     | 10  |

|     | 3-2. パス・サマリ                        | 10  |

|     | 3-3. パス・スラック・レポート                  | 12  |

|     | 3-3-1. Path Summary                | 12  |

|     | 3-3-2. Statistics                  | 13  |

|     | 3-3-3. Data Path                   | 14  |

|     | 3-3-4. Waveform タブ                 | 15  |

|     | 3-3-5. Extra Fitter Information タブ | 16  |

| 4.  | テクニカル・ビューワの活用                      | 18  |

|     | 4-1. Chip Planner                  | 18  |

|     | 4-2. Technology Map Viewer         | 18  |

|     | 4-3. Resource Property Editor      | 19  |

| 5.  | タイミング・エラー改善のための手法                  | 20  |

| ⊐H- | 临尾麻                                | 2.2 |

#### 1. はじめに

この「Quartus® Prime はじめてガイド」シリーズは、インテル® Quartus® Prime 開発ソフトウェアを初めてご利用になるユーザ向けの資料です。

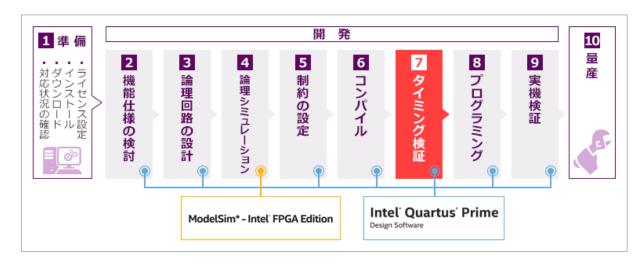

この資料は、FPGA / CPLD 開発の『7. タイミング検証』フェーズで参考になります。

この資料は、FPGA/CPLD のデザイン(回路)に対して与えたタイミング制約用ファイル(SDC ファイル)をQuartus® Prime に登録してコンパイルした時に、配置配線結果がタイミング制約(要求)を満たしているのか、それとも満たすことができなかったのかを確認する方法について説明しています。

元々は ASIC 業界の標準フォーマットになっている Synopsys Design Constraints (SDC) ファイルを FPGA/CPLD のタイミング制約に使用することで、Quartus® Prime の Fitter(配置配線)で目標(ガイド)として参照するだけでなく、TimeQuest Timing Analyzer による高性能なタイミング解析にも使用されます。

大まかな解析ステップを示すと、以下の通りとなります。

- 1. Quartus® Prime のコンパイル・レポートを確認(タイミング・エラーの有無を確認)

- 2. TimeQuest で詳細レポートを生成

- 3. TimeQuest で詳細レポートの解析(タイミング・エラーとなっているパスの遅延の詳細を確認)

この資料では、TimeQuest を使用した詳細パスのタイミング解析結果の確認方法まで説明しています。しかし、タイミング満たせていないパスをどのように改善するかはケースによって異なるので、回避方法の詳細については説明していません。

本資料で使用しているツールおよびツール・バージョンは、以下の通りです。

■ インテル® Quartus® Prime 開発ソフトウェア Standard Edition 17.1

## 2. コンパイル・レポートの確認

タイミング制約用の SDC ファイルが完成したら、Quartus® Prime で SDC ファイルの登録とコンパイルを実行します。SDC ファイルの作成方法や登録については、下記資料をご覧ください。

『Quartus® Prime はじめてガイド - TimeQuest によるタイミング解析の方法』

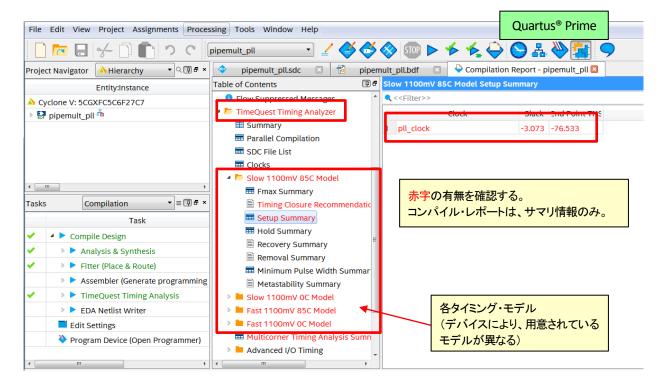

コンパイルが終わったら、コンパイル・レポートを確認してください。コンパイル・レポートではフェーズ毎に詳細なコンパイル結果を確認することができますが、タイミング解析についてはサマリ情報のみ確認できます。配置配線した結果がタイミング制約を満たせないなどのタイミング違反があった場合は、赤字で表示されます。コンパイル後には、まず赤字の有無を確認してください。

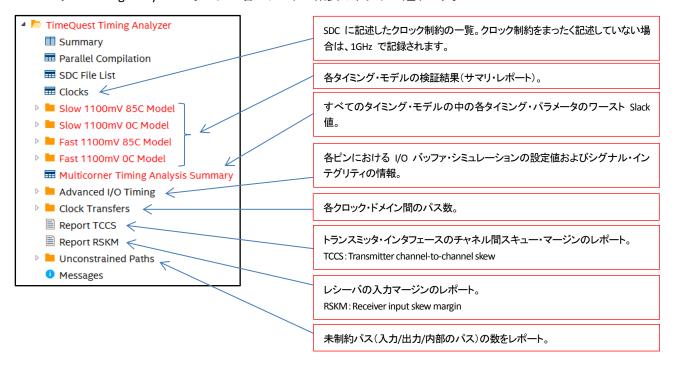

#### 2-1. 各フォルダの概要

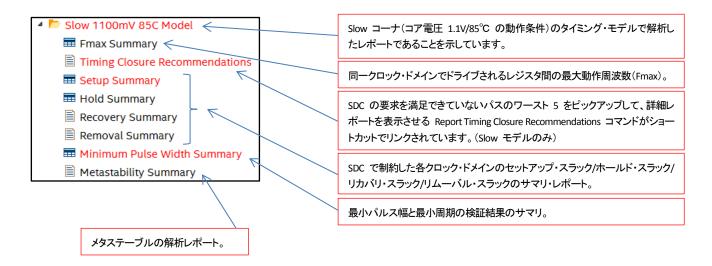

コンパイル・レポートの TimeQuest Timing Analyzer フォルダには、カテゴリごとにレポートが格納されています。 赤字で表示されている項目は、タイミング制約に対して満足していないパス、つまりタイミング・エラーのパスが含まれていることを示しています。

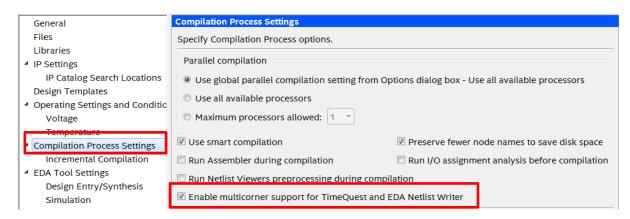

また、複数あるタイミング・モデルごとに詳細なレポートを生成させることもできます。タイミング・モデルの数は、デバイスやプロセスによって異なります。Assignment メニュー  $\Rightarrow$  Settings  $\Rightarrow$  Compilation Process Settings カテゴリの Enable multicorner support for TimeQuest and EDA Netlist writer にチェックを入れてコンパイルすると、各タイミング・モデルにおけるサマリ・レポートが生成されます。

もしコンパイル後にこのオプションを適用させてレポート生成させたい場合は、オプション設定後に TimeQuest Timing Analyzer プロセスを単独で実行してください(Processing メニュー ⇒ Start ⇒ Start TimeQuest Timing Analyzer)。フル・コンパイルすることなく、最終の配置配線結果からタイミング解析してレポートを生成してくれます。

TimeQuest Timing Analyzer フォルダの各カテゴリの概要は、以下の通りです。

#### 2-2. サマリ・レポートの概要

SDC ファイルにタイミング制約漏れがなく、かつ適切な制約ができていることを前提とした時に、主にユーザはコンパイル・レポートの TimeQuest Timing Analyzer フォルダに生成された各タイミング・モデルのタイミング解析結果 (サマリ・レポート)において、タイミング・エラーがないかを確認します。

タイミング・モデルは複数存在するため、サマリ・レポートも複数フォルダに生成されます。それは、半導体デバイスがプロセス<Process>(製造のばらつき)や電圧<Voltage>、温度<Temperature>によって、回路の遅延が変動するためです。この 3 つの組み合わせを PVT 条件やデバイスの動作条件と呼んだりします。一般的に、電圧が高くて温度が低いほど遅延は小さくなり、高速で動作します。最も速い動作条件を「Fast コーナ」、最も遅い動作条件を「Slow コーナ」と呼びます。タイミングの解析は、少なくてもこの 2 つの動作条件で行います。

"少なくても 2 つの動作条件"と書いたのは、デバイスのベンダによって考え方に違いがあるからです。例えば、インテル® FPGA の場合、90-nm プロセスまでの FPGA は 2 つの動作条件で解析しますが、40/60/65-nm プロセスの FPGA では 3 つ、14/20/28-nm プロセスの FPGA では 4 つの動作条件で解析します。一般的には、Fast/Slow コーナの 2 つですべての条件をカバーできるように、タイミング・モデルに余裕を持たせます。動作条件を追加すれば、更に正確な解析ができるため、2 つ以上の動作条件を使う場合があります。つまり、ユーザはすべてのタイミングを満足したかどうかを確認する必要があります。

ここから、Slow コーナのサマリ・レポートを例に、各フォルダを説明します。

ここで、タイミング・エラーになっている項目に着目します。Setup Summary をクリックすると、Slow コーナにおける各クロック・ドメインのセットアップ解析のサマリ・レポートが表示されます。それぞれの列のラベルは、「Clock」と「Slack」、「End Point TNS」です。

「Clock」列には、クロック・ドメインの名前が表示されます。複数のクロック・ドメインがあるデザインでは、すべてのクロック・ドメインが表示されます。

「Slack」列には、クロック・ドメインの最小スラックが表示されます。この値がマイナスの時は赤字で表示され、タイミングを満たしていないパスがあることを示します。

「End Point TNS」の TNS は Total Negative Slack の略で、クロック・ドメイン内のマイナスのスラック値を合計した値です。この値が大きいほど、そのクロック・ドメインにはタイミングを満たさないパスが数多く残っていて、タイミング収束が難しいと考えられます。

更に詳しい解析をするには、タイミングを満たさなかったパスがどのように構成されているのかを確認するため、 詳細レポート(パス・スラック・レポート)を生成します。

#### 2-3. 詳細レポート(パス・スラック・レポート)の生成

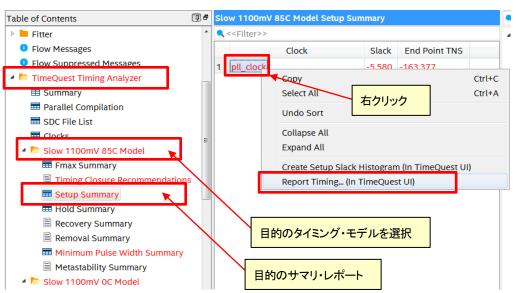

サマリ・レポートからさらに詳しい解析をするために、詳細レポート(パス・スラック・レポート)を生成します。なお、詳細レポートを生成する方法は幾つかあります。例えば、Quartus® Prime から別途 TimeQuest Timing Analyzer を起動して目的のタイミング・モデルを選択し、再度サマリ・レポートを生成してから詳細レポートを生成させるフローがインテルのドキュメントなどでも紹介されていますが、本資料では手軽に詳細レポートを生成させる方法で説明します。

コンパイル・レポート内の TimeQuest Timing Analyzer フォルダから詳細の解析をしたいタイミング・モデルのフォルダを展開して、目的のパラメータのサマリ・レポートを選択します。その後、詳細に確認したいクロック・ドメインを選択して、右クリックします。表示されたプルダウン・メニューから Report Timing... (In TimeQuest UI) を選択します。

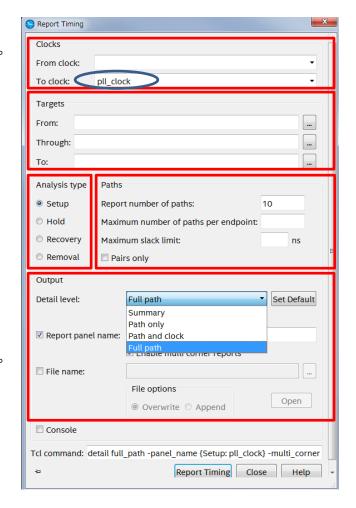

自動的に TimeQuest が起動してバックグラウンドで指定したタイミング・モデルのタイミング用ネットリスト (Post-fit)が生成され、登録した SDC ファイルを読み込み、指定した内容が入力された状態で Report Timing ダイアログ・ボックスが表示されます。このまま Report Timing をクリックしても詳細なレポートが生成されますが、必要な項目を追加することで表示するパスを絞り込むことができます。

#### Clocks

必要に応じて、解析したいパスの送信クロック (From Clock)と受信クロック(To Clock)を指定します。 サマリ・レポートからのリンクで開いた場合は、受信クロック(To Clock)が入力された状態になっています。

#### Targets

必要に応じて、解析したいパスの始点(From)と通 過点(Through)、終点(To)を指定します。

#### Analysis type

セットアップ/ホールド/リカバリー/リムーバルのいずれかを選択します。サマリ・レポートからのリンクで開いた場合は、セットアップが選択された状態になっています。

#### Paths

レポートに表示するパスの数や条件を指定します。 デフォルトは 10 パスです。スラックがある値より小 さいパスを表示するといった指定もできます。

#### Output

表示するレポートの詳細レベルを指定します。また、レポート表示のパネル名の指定やレポートの内容をテキストのファイルへ出力させることもできます。

表示するレポートの条件などを入力した状態で Report Timing をクリックすると、条件に合致した詳細レポート (パス・スラック・レポート)が表示されます。

## 3. 詳細レポート

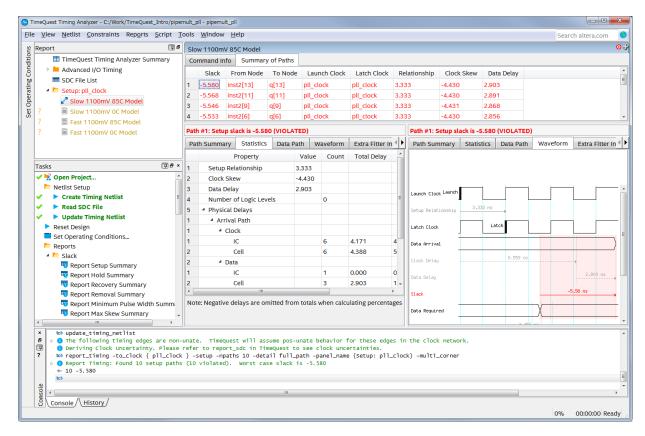

TimeQuest Timing Analyzer レポートの各タイミング・モデルのサマリから、Report Timing をクリックして詳細レポートを生成したら、パス・スラック・レポートを解析します。この詳細レポートで、タイミング要求を満たせなかったパスがどのように構成されているのかを確認して、その要因を明確にします。

#### 3-1. 詳細レポートの概要

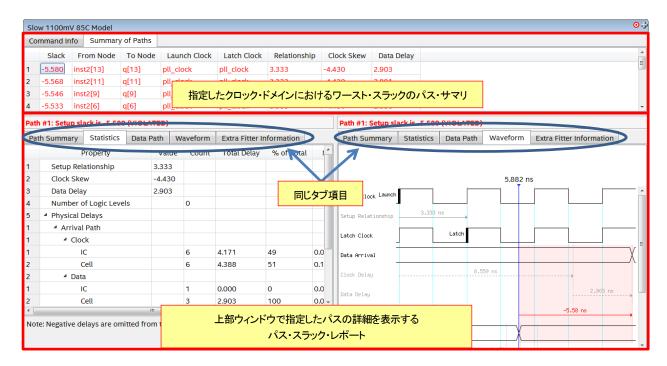

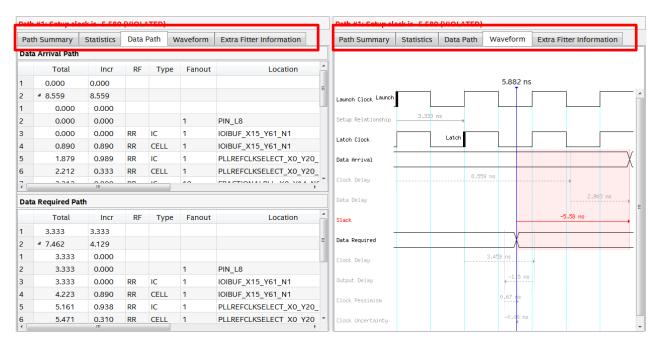

Report Timing により生成したレポートは、大きく2画面で構成されています。

上部ウィンドウでパスをクリック(指定)すると、下部ウィンドウが連動して指定パスの詳細を表示する仕組みになっています。下部ウィンドウは左右に分割されているので、好みに応じて同時に別タブの情報を見ることができます。

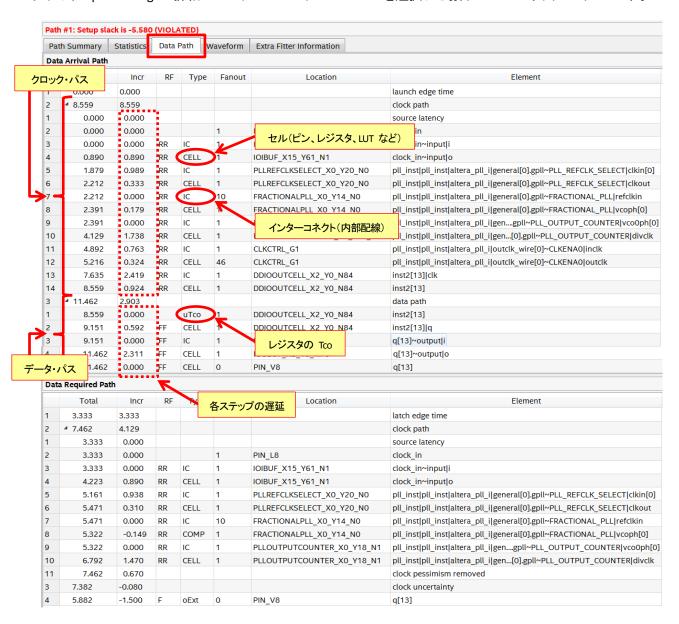

#### 3-2. パス・サマリ

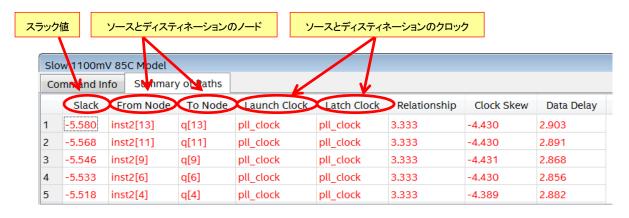

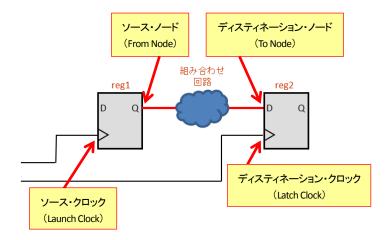

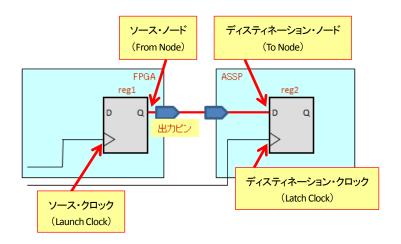

クロック・ドメインにおけるワースト・スラックのパス・サマリのウィンドウ(詳細レポートの上部)では、以下の情報が確認できます。この例は、To Node が出力ポートなので、以下の例2 が該当します。

#### ■ 例1:内部レジスタ間のパス

#### ■ 例2:デバイスを跨ぐレジスタ間のパス

スラック値(単位:ns)は、SDC 制約に対してのマージンです。マイナス値の場合は、期待値(制約値)に対してどのくらい不足しているかを示します。

例えば 1 行目は、以下のように読み取ります。

<u>ソース・ノード(送信ノード)の"inst2[13](レジスタ)"</u>から<u>ディスティネーション・ノード(受信ノード)"q[13](出力ポート)に接続している対向デバイス(後段のデバイス)の入力レジスタ"</u>までは、それぞれ SDC で定義したクロック "pll\_clock" (PLL 出力クロック)と"pll\_clock" (PLL 出力クロック)の同一クロックでドライブされており、そのノード間の遅延は、SDC で制約した制約値に対して 5.580ns 不足している。

では、このノード間はどのような経路により制約値を満足できないのかを確認するため、パス・スラック・レポート を解析します。

#### 3-3. パス・スラック・レポート

詳細レポートの下部ウィンドウにあるパス・スラック・レポートは、左右に分割され、同じタブが用意されています。 同時に別タブの情報を見ることができます。

タイミング・エラーを起こしているパスを改善するため、ユーザはこれらの情報から現状(要因)を把握する必要があります。各タブの概要を紹介します。

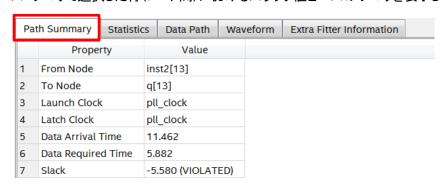

#### 3-3-1. Path Summary

パス・サマリで選択した行(ノード間)におけるスラック値とパスのサマリを表示しています。

Data Arrival Time(データ到達時間)とは、クロック・ソースの送信エッジから送信レジスタを通って受信レジスタに データが到達するまでの時間のことです。これは、送信レジスタまでのクロック遅延と送信レジスタの遅延、受信レジスタまでのデータ遅延の合計です。

Data Required Time(データ要求時間)とは、受信レジスタが正しくデータを受け取るために、受信レジスタにデータが到達しておくべき時間のことです。

Slack は SDC 制約に対して、実際の回路が持つタイミングのマージンのことです。以下の式により算出され、回路内のすべてのパスに対してスラックがプラス値になれば、その回路はタイミング要求を満たして正しく動作することを示します。

Setup Slack = Data Required Time (Setup) — Data Arrival Time

Hold Slack = Data Arrival Time - Data Required Time (Hold)

タイミング解析をするには、まず用語と考え方を理解する必要があります。本資料では、用語と考え方の説明を 省略しています。詳細は、下記資料をご覧ください。

『TimeQuest ~タイミング解析の用語と考え方~』

#### 3-3-2. Statistics

パス・サマリで選択した行(ノード間)におけるパス遅延の統計を表示しています。

| Path S | Summary                | Statistics | Data I | Path   | Waveform | Extra Fitter I | nformation |        |        |

|--------|------------------------|------------|--------|--------|----------|----------------|------------|--------|--------|

|        | F                      | roperty    |        | Valu   | e Count  | Total Delay    | % of Total | Min    | Max    |

| 1      | Setup Relationship     |            |        | 3.333  |          |                |            |        |        |

| 2      | Clock Ske              | w          |        | -4.430 | )        |                |            |        |        |

| 3      | Data Delay             |            |        | 2.903  |          |                |            |        |        |

| 4      | Number of Logic Levels |            |        |        | 0        |                |            |        |        |

| 5 4    | ■ Physical Delays      |            |        |        |          |                |            |        |        |

| 1      | ▲ Arrival Path         |            |        |        |          |                |            |        |        |

| 1      |                        |            |        |        |          |                |            |        |        |

| 1      | IC                     |            |        | 6      | 4.171    | 49             | 0.000      | 2.419  |        |

| 2      | Cell                   |            |        | 6      | 4.388    | 51             | 0.179      | 1.738  |        |

| 2      | ■ Data                 |            |        |        |          |                |            |        |        |

| 1      | IC                     |            |        |        | 1        | 0.000          | 0          | 0.000  | 0.000  |

| 2      | Cell                   |            |        |        | 3        | 2.903          | 100        | 0.000  | 2.311  |

| 3      | uTco                   |            |        |        | 1        | 0.000          | 0          | 0.000  | 0.000  |

| 2      | Required Path          |            |        |        |          |                |            |        |        |

| 1      |                        |            |        |        |          |                |            |        |        |

| 1      | IC                     |            |        | 4      | 0.938    | 26             | 0.000      | 0.938  |        |

| 2      | Cell                   |            |        | 3      | 2.670    | 74             | 0.310      | 1.470  |        |

| 3      | Р                      | LL Compens | ation  |        | 1        | -0.149         | 0          | -0.149 | -0.149 |

Arrival Path および Required Path は、Data Arrival Path と Data Required Path のクロックとデータの内訳を表しています。

また、IC (Inter Connect) は、内部配線の遅延の合計を表しています。Cell は、内部セル(ピンやロジック・エレメントなど配線以外の部分)の遅延の合計を表しています。uTco は、内部レジスタの出力遅延(Clock-to-Output Time / Tco)です。

#### 3-3-3. Data Path

パス・サマリで選択した行(ノード)におけるパス遅延の詳細(経路)を表示いています。ユーザはこの Data Path タブをメインに検証します。画面は Data Arrival Path と Data Required Path に分かれていて、"データ到達時間"と"データ要求時間"のパスを表示しています。

以下は、Report Timing の詳細レベル(Detail Level)に Full Path を選択した場合のパス・スラック・レポートです。

その他、各列では以下のような内容が確認できます。

| Total    | ノードまでの遅延時間の合計                               |                           |  |  |  |  |

|----------|---------------------------------------------|---------------------------|--|--|--|--|

| Incr     | ノードまでの遅延時間                                  |                           |  |  |  |  |

| RF       | 信号の立ち上がり(Rise)、立ち下がり(Fall)のどちらを解析したパスかを示します |                           |  |  |  |  |

| Туре     | ノードのタイプを示します                                |                           |  |  |  |  |

|          | CELL                                        | 論理セル                      |  |  |  |  |

|          | IC                                          | 配線(Inter Connect)         |  |  |  |  |

|          | СОМР                                        | PLL の位相補正値                |  |  |  |  |

|          | uTco/uTsu/uTh                               | レジスタの出力遅延/セットアップ時間/ホールド時間 |  |  |  |  |

|          | iExt/oExt                                   | 入力/出力の制約設定値               |  |  |  |  |

| Fanout   | ノードのファンアウト数                                 |                           |  |  |  |  |

| Location | ノードの配置された位置                                 |                           |  |  |  |  |

| Element  | ノードの名前                                      |                           |  |  |  |  |

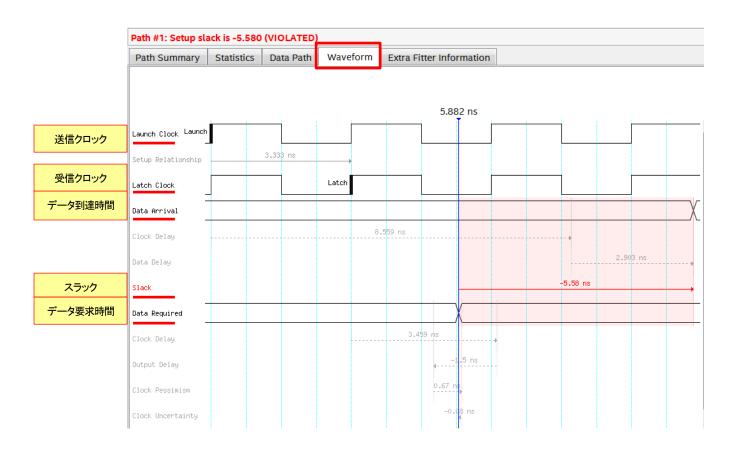

#### 3-3-4. Waveform タブ

パス・サマリで選択した行(ノード)における Data Path タブの情報をグラフィカルに波形表示しています。ここにはデータ到達時間やデータ要求時間、スラックの関係が波形で表示されるので、直感的かつ視覚的にもわかりやすく検証ができます。

特に入出力タイミングの解析では、ユーザが与えたタイミング制約とタイミング解析した結果から得られるスラックなどの関係が、Data Path タブなどの数値のみではわかりにくいことがあるので、Data Path タブと同時に Waveform タブを見ることで確認しやすくなります。

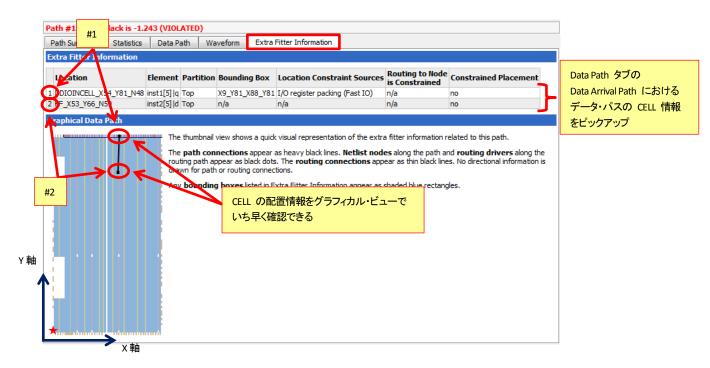

#### 3-3-5. Extra Fitter Information タブ

パス・サマリで選択した行(ノード)におけるフィッタ情報(配置配線情報)を視覚的に表示しています。このタブは、60/65-nm 以降のプロセスのデバイスで表示されます。

例えば、上部に示された表の 1 がデータ・パスの始点、最末尾がデータ・パスの終点で、共に黒ドットで表示されます。その間のルーティングは黒線で表示されます。ただし、このルーティング表示は、実際の配線経路を表示している訳ではありません。CELL の位置を直線的に結んだものです。なお、Location 項は座標(X, Y)で示され、デバイスの左下(★マーク)が原点(X1, Y1)です。

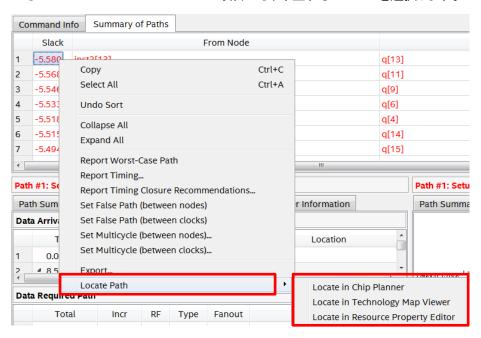

## 4. <u>テクニカル・ビューワの活</u>用

TimeQuest のパス・スラック・レポートの情報を、Quartus II のグラフィカル・ビューワ・ツールと関連付けて閲覧することができます。数値のみのタイミング解析情報に加えて、視覚的な情報がプラスされることで、ユーザはより現状を把握することができます。

詳細レポートのパス・サマリの中で確認したいパスの Slack 付近を指定して、右クリックで現れるプルダウン・メニューから Location Path ⇒ Locate in \*\*\* 項目から、希望するビューワを選択します。

#### 4-1. Chip Planner

タイミングを満たさない原因は様々ですが、その 1 つに"配置の問題"があります。それを検証するのに便利なツールが Chip Planner です。

Chip Planner は、デバイスのリソース(ロジック・エレメントやメモリ・ブロック、DSP ブロック、I/O ピンなど)の使用状況やデバイス内部のどこに配置しているかをグラフィカルに確認できるビューワです。その機能を活用して、TimeQuest により得られたタイミングの詳細レポートで指定したデータ・パス間のセル配置関係を確認します。

※ 本資料では、Chip Planner の詳細については割愛します。

#### 4-2. Technology Map Viewer

タイミングを満たさない原因は様々ですが、その 1 つに"回路の実現方法の問題"があります。それを検証するのに便利なツールが Technology Map Viewer です。

Technology Map Viewer は、作成した論理回路がどのような論理ブロックで構成され、接続されているのかをグラフィカルに確認できるビューワです。その機能を活用して、TimeQuest により得られたタイミングの詳細レポートで指定したデータ・パス間のセル構成を確認します。

※ 本資料では、Technology Map Viewer の詳細については割愛します。

#### 4-3. Resource Property Editor

Chip Planner や Technology Map Viewer と共に、必要に応じて使用すると便利なツールが Resource Property Editor です。

Resource Property Editor は、ロジックの実装と接続の詳細をデバイスの構造(デバイス・アーキテクチャ)レベルで確認できるグラフィカル・ビューワです。Chip Planner や Technology Map Viewer から、さらにデバイス構造レベルの配置情報を得たいときに、各ビューワから Resource Property Editor にクロス・プローブするといった使い方が主です。

※ 本資料では、Resource Property Editor の詳細については割愛します。

## 5. タイミング・エラー改善のための手法

タイミング解析した結果、タイミング違反のパスがある場合は、タイミング違反に至っている原因を探ります。タイミング・エラーは、主に以下の原因が考えられます。(もちろん、これら以外の要因もあり得ます。)

- データ・パス間の多段ロジック

- 送信側の高ファンアウト信号

- 物理的制約の衝突(配置や配線)

- 厳しいタイミング制約

タイミングの詳細レポートやテクニカル・ビューワなどから、タイミング・エラーの原因を調査して、改善させる必要があります。

● Timing Optimization Advisor の活用(Tools メニュー ⇒ Advisors ⇒ Timing Optimization Advisor)

Advisor は、デザインを最適化するための推奨設定を提案してくれる機能です。提案された設定を試すことで、状況が改善する可能性があります。 マークは、適用されていない設定であることを表しています。ユーザは内容を確認して、試してみる価値があるかどうかを判断します。設定によっては、Settings 画面を開かなくても、Correct the Settings をクリックするだけで簡単に設定を反映させることができます。 マークは、既に適用済みの設定を表しています。Undo をクリックすると、未設定の状態に戻すことができます。

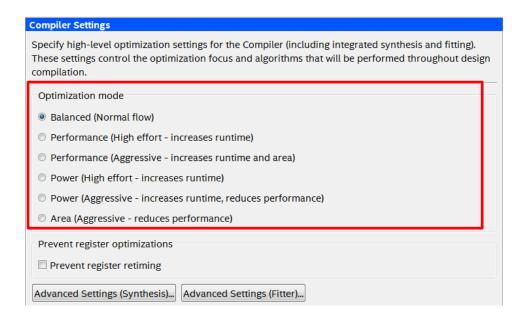

● 配置配線オプションの変更(Assignments メニュー ⇒ Settings ⇒ Compiler Settings)

高パフォーマンスになるような配置配線設定や消費電力低減になるような配置配線設定、リソースをなるべく消費しないエリア重視の配置配線設定があります。デフォルトはパフォーマンスとパワー、エリアのバランスの取れた設定である Balanced になっています。

#### ● デザインの見直し

場合によっては、デザインの見直しで改善するかも知れません。タイミング違反の要因によっては、検討する必要があるかも知れません。

- タイミング制約の見直し(本当に正しい制約をしているか?必要以上に厳しい制約になっていないか?) タイミング制約をもう一度見直して、制約値が厳しすぎることなく最適かどうかを確認してみてください。基本的には、タイミング制約にマージンを持たせる必要はありません。(100MHz で動作するクロックに対して、110MHz のクロックであるといった過剰なタイミング制約与えるなど)

- デバイスのスピード・グレードを高速デバイスへ変更 デバイスのスピード・グレードの変更が許容できる場合は、試してみると良いかも知れません。

## 改版履歴

| Revision | 年月      | 概要 |

|----------|---------|----|

| 1        | 2018年3月 | 初版 |

#### 免責およびご利用上の注意

弊社より資料を入手されましたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可無く転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、本資料を入手されました下記代理店までご一報いただければ幸いです。 株式会社マクニカ アルティマ カンパニー <a href="https://www.alt.macnica.co.jp/">https://www.alt.macnica.co.jp/</a> 技術情報サイト アルティマ技術データベース <a href="https://www.altima.jp/members/">https://www.alt.macnica.co.jp/</a> 技術情報サイト アルティマ技術データベース <a href="https://www.altima.jp/members/">https://www.altima.jp/members/</a>

株式会社エルセナ http://www.elsena.co.jp 技術情報サイト ETS https://www.elsena.co.jp/elspear/members/index.cfm

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

- 5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる際は、各メーカ発行の英語版の資料もあわせてご利用ください。