インテル® Agilex™ FPGA & SoC / インテル® Stratix® 10 FPGA 外部メモリー・インターフェース Example Design Traffic Generator 2.0

# MACNICA

株式会社マクニカ アルティマカンパニー

Rev.1.0 2021/10

# 概要

- ◆ 本資料は、外部メモリー・インターフェースの Example Design に実装される Traffic Generator 2.0 の設定および動作についてまとめています

- 実機確認手順については、下記をご参照ください

- <u>インテル® Agilex™ FPGA & SoC 外部メモリー・インターフェース Traffic Generator 2.0</u>

- 本資料の画像は、下記ツールを使用しています

- 。 インテル® Quartus® Prime 開発ソフトウェア プロ・エディション 21.1

# Agenda

- 1. Traffic Generator

- 2. 起動画面

- 3. Instruction Pattern

- 4. Address Pattern

- 5. Data Pattern

- 6. Traffic Preset Mode

- 7. まとめ

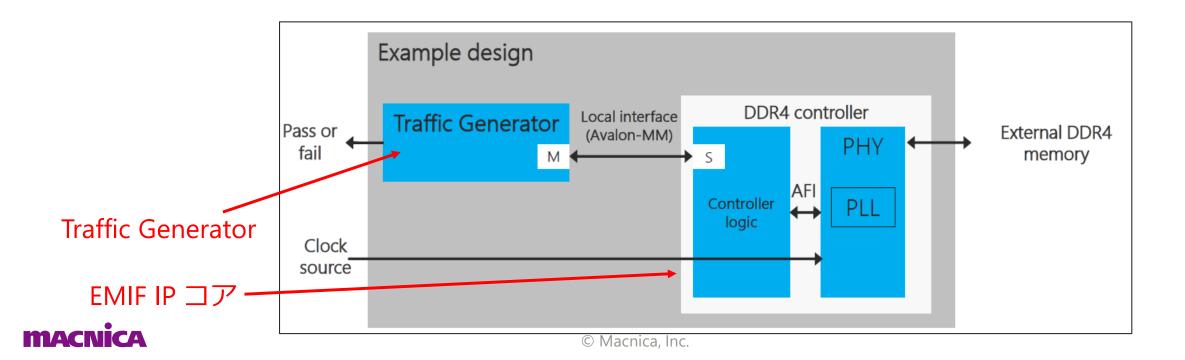

#### Traffic Generator について

- Traffic Generator とは、EMIF IP コアの生成する Example Design 内に実装される、テスト用の回路です

- 。 テスト・パターン生成、および リード・データ の チェックをおこないます

- Traffic Generator 2.0 を使用することで、ユーザー側からテスト・パターンを設定することができます

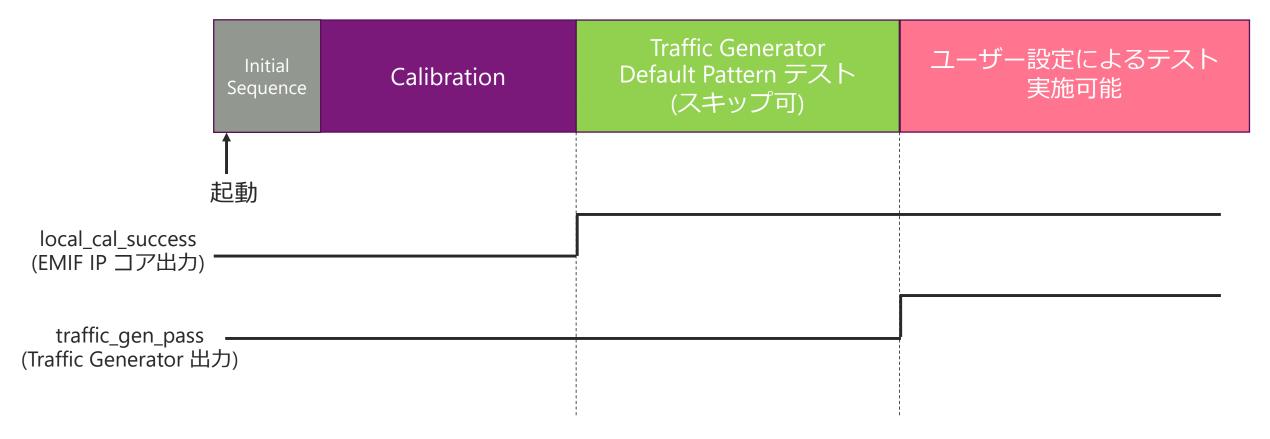

# Example Design の起動時の動作

- Example Design の起動時の動作は、下記のとおりです

- Traffic Generator のテストが完了後、ユーザー設定によるテストを実施 可能です

#### Traffic Generator の設定について

● IP コア生成時に、Example Design に実装する Traffic Generator を設定します

\* Traffic Generator (Settings only applicable for example design)

| <ul> <li>Traffic Generator (settings only applicable for example design)</li> </ul> |       |   |

|-------------------------------------------------------------------------------------|-------|---|

| ✓ Use configurable Avalon traffic generator 2.0                                     |       |   |

| ✓ Enable default traffic pattern (pattern configured during compile-time)           |       |   |

| ✓ Enable user-configured traffic pattern (pattern configured during run-time)       |       |   |

| TG2 default traffic duration:                                                       | Short | - |

| TG2 Configuration Interface Mode:                                                   | JTAG  | - |

|                                                                                     |       |   |

| 項目                                                                          | 設定  | 説明                                                                      |

|-----------------------------------------------------------------------------|-----|-------------------------------------------------------------------------|

| Use configurable Avalon traffic generator 2.0                               | ON  | Traffic Generator 2.0 が実装されます。                                          |

|                                                                             | OFF | Legacy の Traffic Generator が実装されます。                                     |

| Enable default traffic pattern (pattern configured during compiletime)      | ON  | Calibration 後に Traffic Generator のデフォルト設定でのテストが実行されます。                  |

|                                                                             | OFF | テストは実行されず Calibration 完了で停止します。                                         |

| Enable user-configured traffic pattern (pattern configured during run-time) | ON  | Traffic Generator に対してユーザー側からパターン設定等のアクセスが可能になります。                      |

|                                                                             | OFF | OFF にした場合、ユーザー側からのアクセスは無視されます。<br>(以降で紹介するユーザー側からの設定をおこなうには、ON にしてください) |

#

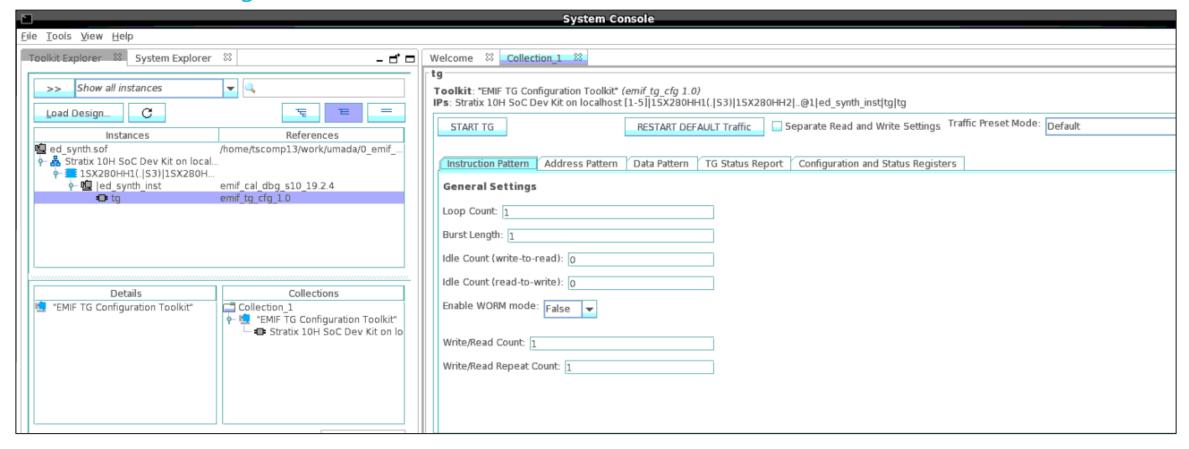

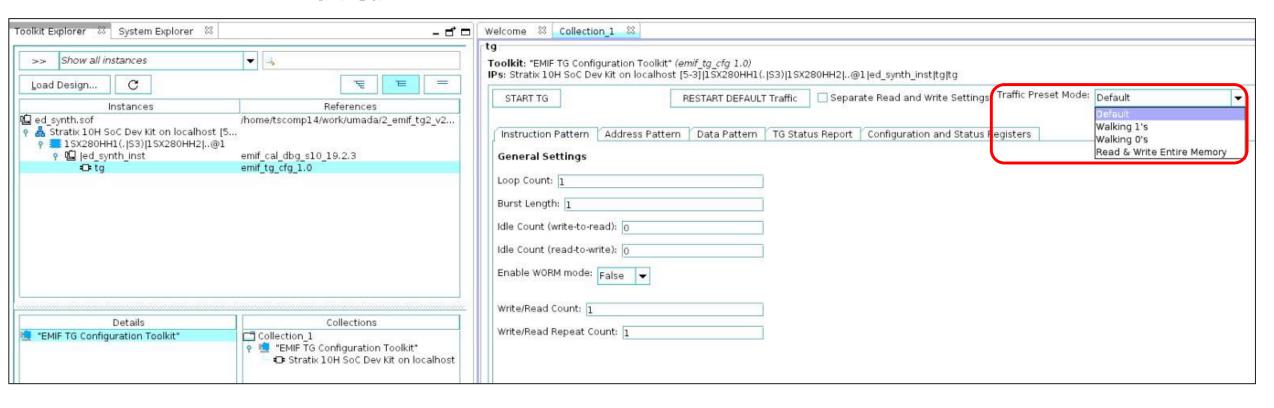

#### Traffic Generator 2.0 の起動画面

#### ● 起動時の表示画面

- 起動手順は下記リンクをご参照ください

- 。 <u>インテル<sup>®</sup> Agilex<sup>™</sup> FPGA & SoC 外部メモリー・インターフェース Traffic Generator 2.0</u>

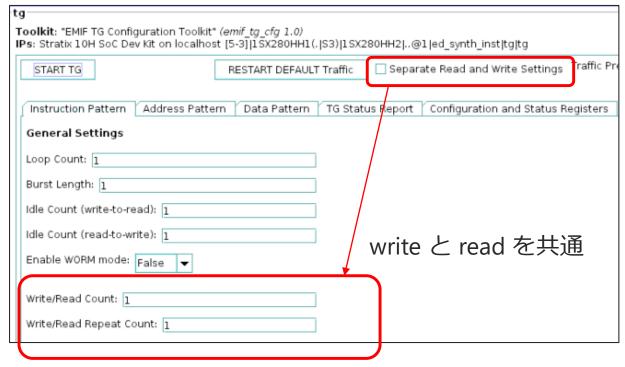

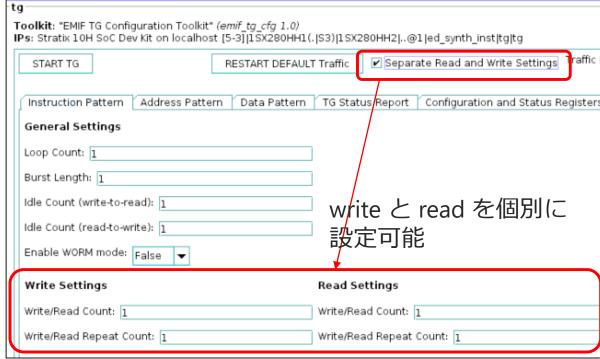

# Separate Read and Write settings

- Separate Read and Write settings

- 。 ライト時と リード時と個別に設定する機能です

- 今回は OFF 設定として、ライトとリードは同じ設定としています

#### 今回はこの設定で動作確認を実施

(参考: ON に設定時の画面)

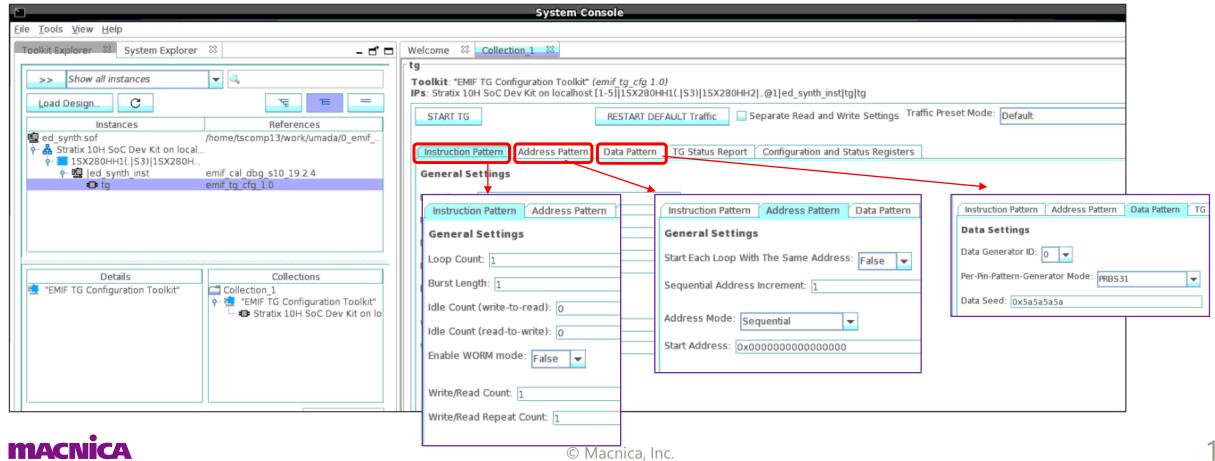

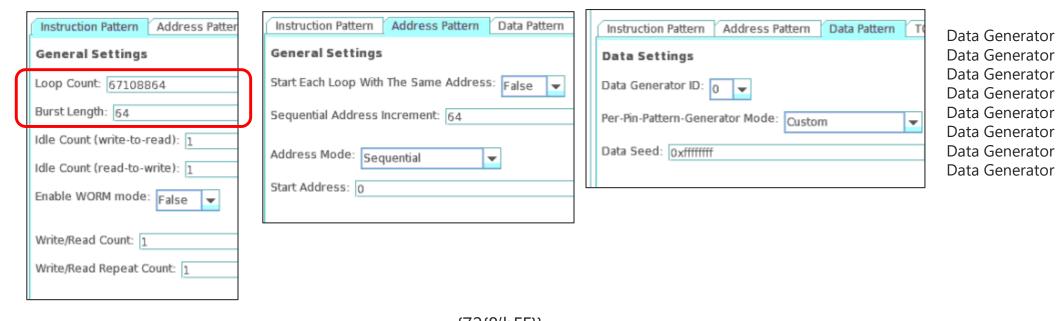

#### 設定タブ

#### ● 動作設定をおこなうのは下記タブです

- 。 Instruction Pattern タブ

- Address Pattern タブ

- 。 Data Pattern タブ

10

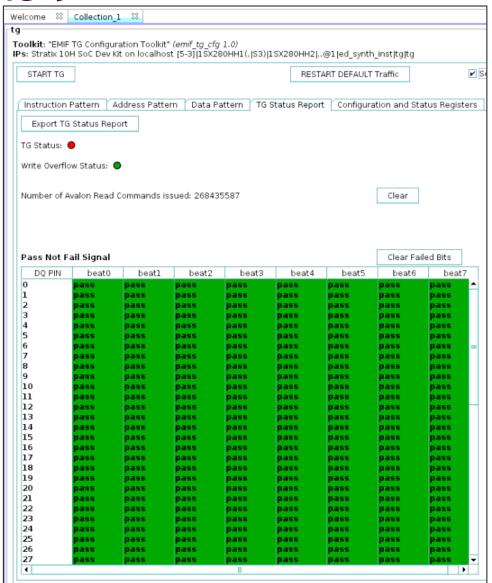

#### Pass / Fail 判定について

● Pass / Fail は TG Status Report に表示されます

・ ビット毎に表示されます (今回の評価では全て Pass となるため、省略)

© Macnica, Inc.

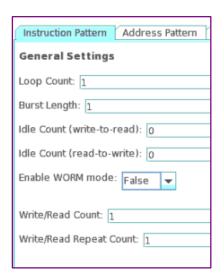

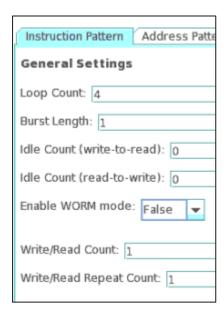

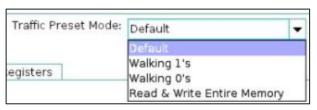

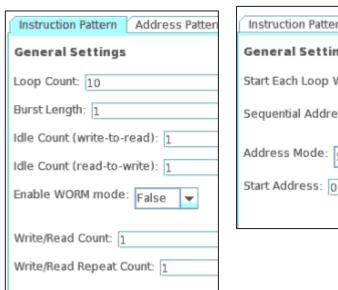

# Instruction タブの設定項目について

| 項目                            | 説明                                                                        |

|-------------------------------|---------------------------------------------------------------------------|

| Loop Count                    | 設定した一連の動作をループする回数を設定します。<br>"0" を設定した場合、無限ループとなります。                       |

| Burst Length                  | 各アクセスのバースト長を設定します。                                                        |

| Idle Count<br>(write-to-read) | ライト動作からリード動作に切り替える際に挿入する アイドル時間(クロック数)を設定します。<br>なお本資料では動作波形による説明はございません。 |

| Idle Count<br>(read-to-write) | リード動作からライト動作に切り替える際に挿入するアイドル時間(クロック数)を設定します。<br>なお本資料では動作波形による説明はございません。  |

| Enable WORM mode              | WORM モードの Enable/Disable を設定します。                                          |

| Write/Read Count              | 各ライト/リード動作の回数を設定します。<br>アドレスを変更しておこなう回数となります。                             |

| Write/Read Repeat Count       | 各ライト/リード動作について、同一アドレスに繰り返しアクセスする回数を設定します。                                 |

13

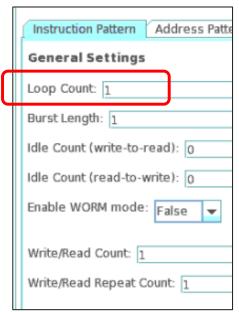

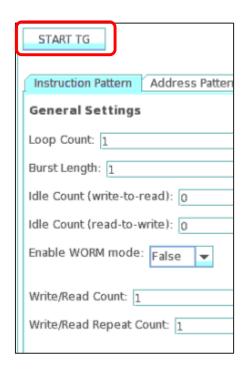

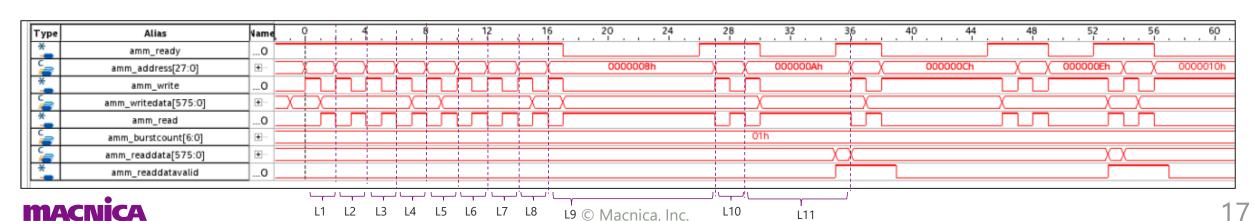

# Loop Count (1)

#### ● 繰り返し回数を設定します

。 Loop Count = 1 の動作波形

#### 【動作】

- ① addr 0 (⊂ single write (1 burst)

- 2 addr 0 ( $\subset$  single read (1 burst)

- ①② を Loop Count 数 (=1) 実行して停止

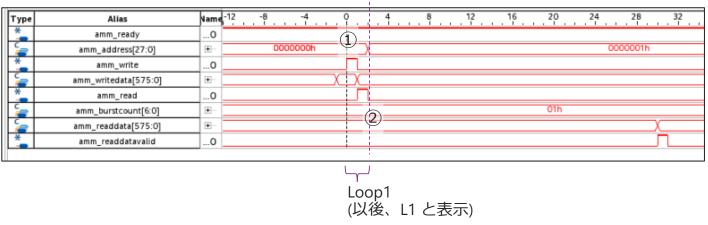

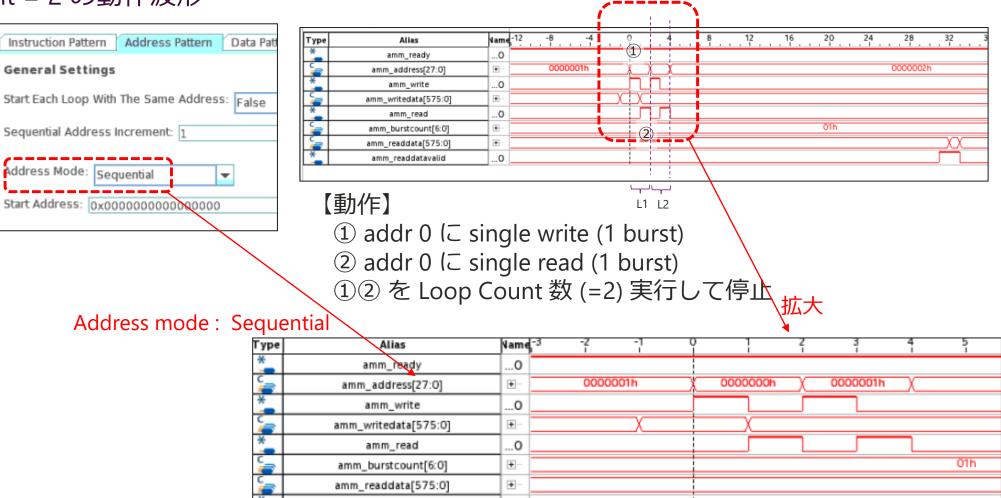

# Loop Count (2)

#### ● 繰り返し回数を設定します

。 Loop Count = 2 の動作波形

0.

amm readdatavalid

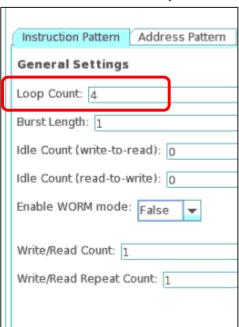

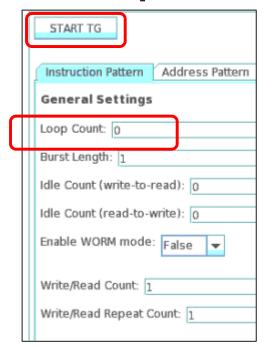

# **Loop Count (3)**

#### ● 繰り返し回数を設定します

Loop Count = 4 の動作波形

Instruction Pattern

**General Settings**

Sequential Address Increment: 1

Start Address: 0x0000000000000000

Type

Address Mode: Sequential

Address Pattern Data Patt

Alias

amm\_ready

amm\_write

amm\_read

Start Each Loop With The Same Address: False

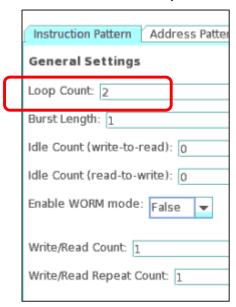

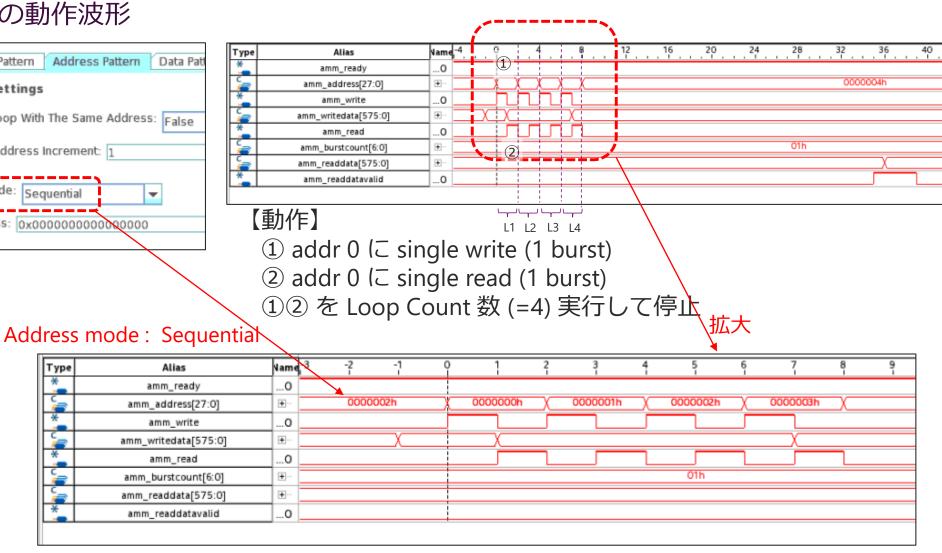

# Loop Count (4): Loop Count = 0 の設定

Loop Count = 0 の場合、連続動作となります

START TG の表示が STOP TG ... に 切り替わります

Instruction Pattern Address Pattern

General Settings

Loop Count:

Burst Length:

Idle Count (write-to-read):

Idle Count (read-to-write):

Enable WORM mode:

False

Write/Read Count:

Write/Read Repeat Count:

1

停止する場合、ク リックします。 START TG の表示に 切り替わります

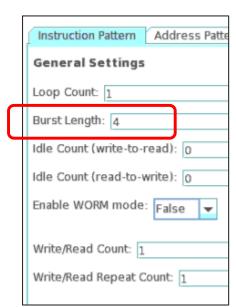

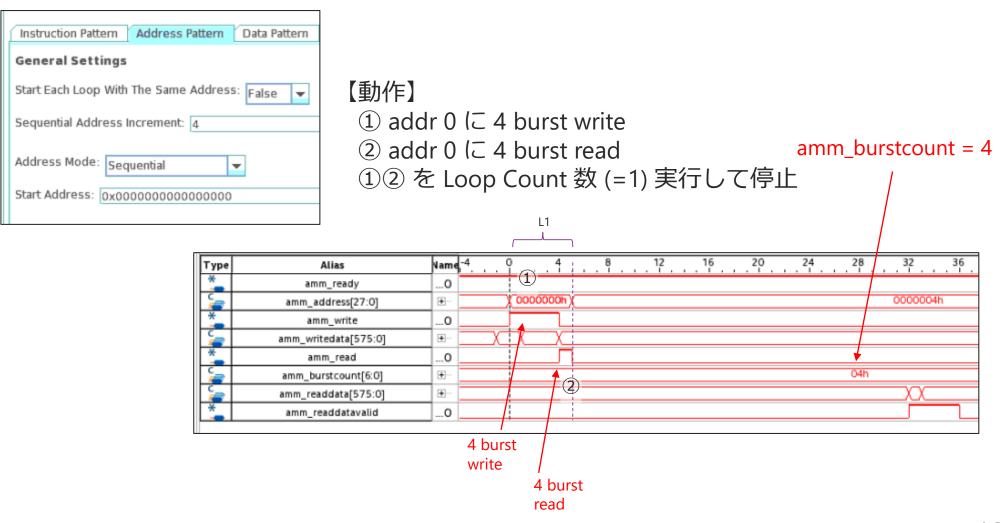

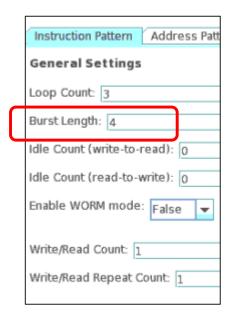

# **Burst Length (1)**

#### ● Burst 長を設定します

。 Burst Length = 4 の動作波形 (Loop Count = 1)

# **Burst Length (2)**

#### Burst 長を設定します

Burst Length = 4 の動作波形 (Loop Count = 3)

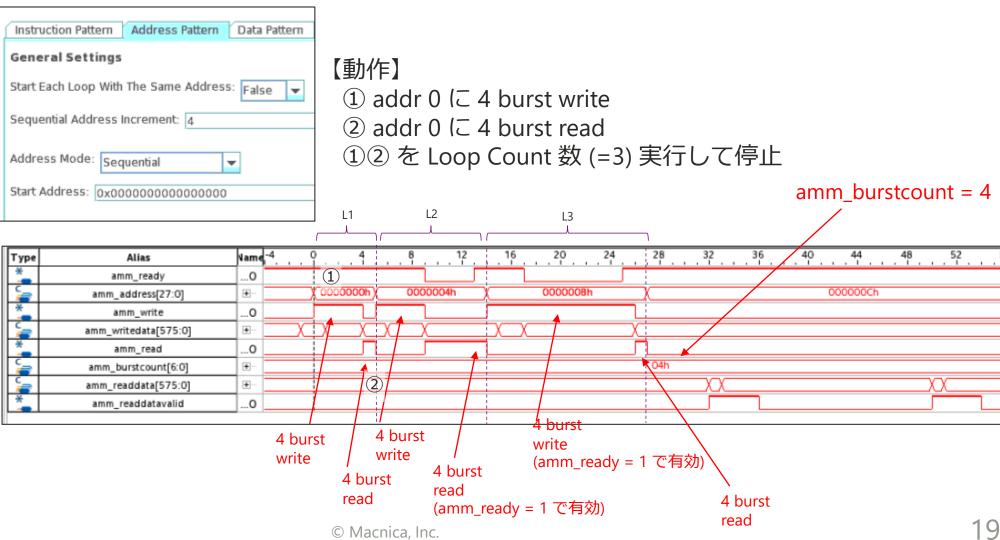

#### **Enable WORM mode**

- WORM (Write-Once-Read-Many) Mode

- リードデータが不一致となった場合、同一アドレスを再度リードします

- 両方のリードデータが同じ場合、ライト時の問題の可能性が高い

- 両方のリードデータが異なる場合、リード時の問題の可能性が高い

- 。 リードデータが期待値と一致の場合は再リードは実行されません

①② を Loop Count 数 (=4) 実行して停止

リードデータが期待値と一致したため、各リードは一回で完了

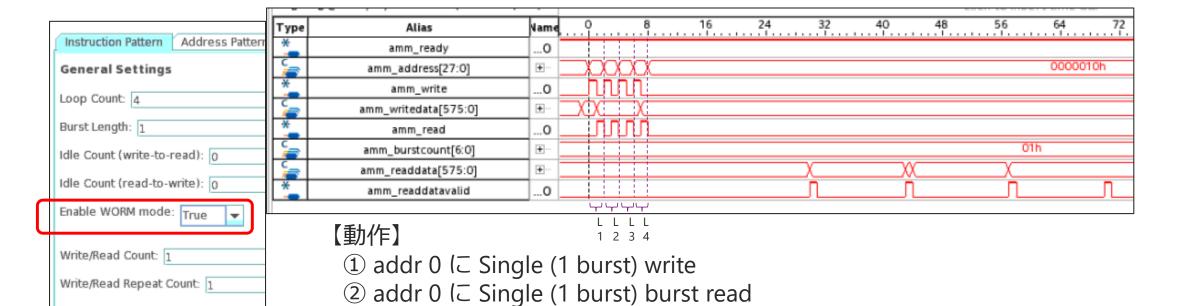

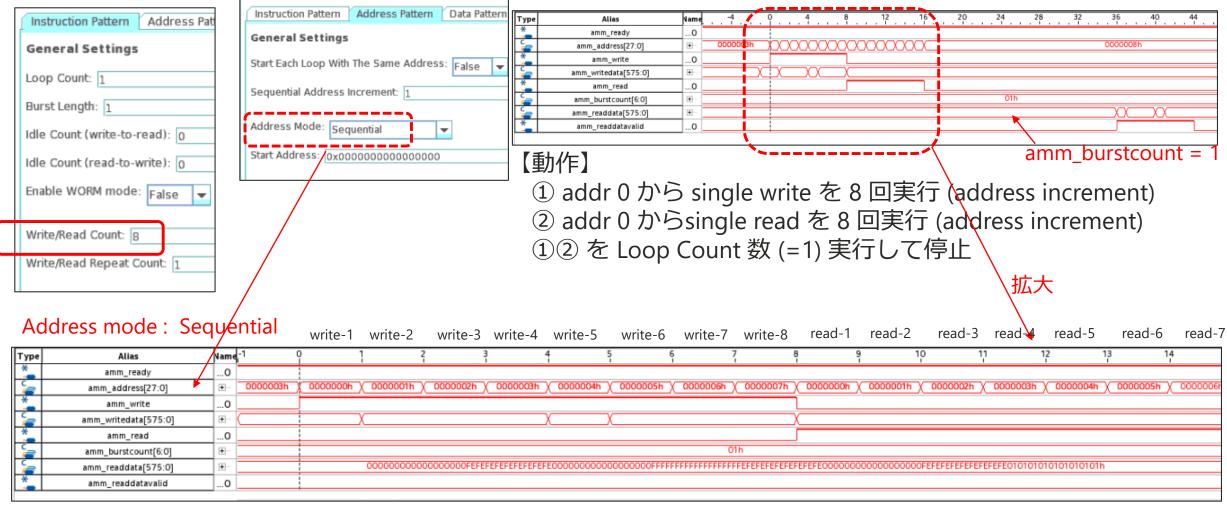

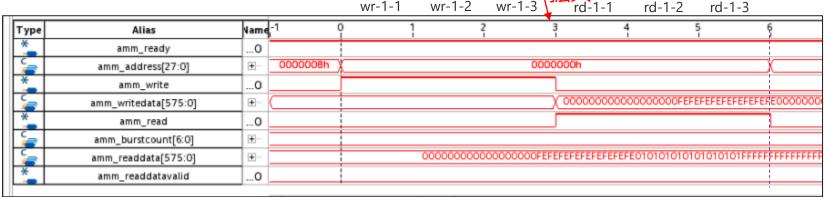

#### Write/Read Count (1)

- ライト/リードそれぞれの実行数を設定します

- 。 Write/Read Count = 3 の動作波形 (Loop Count = 1, Burst Length = 1)

© Macnica, Inc.

## Write/Read Count (2)

- ライト/リードそれぞれの実行数を設定します

- 。 Write/Read Count = 8 の動作波形 (Loop Count = 1, Burst Length = 1)

22

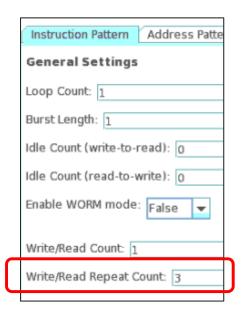

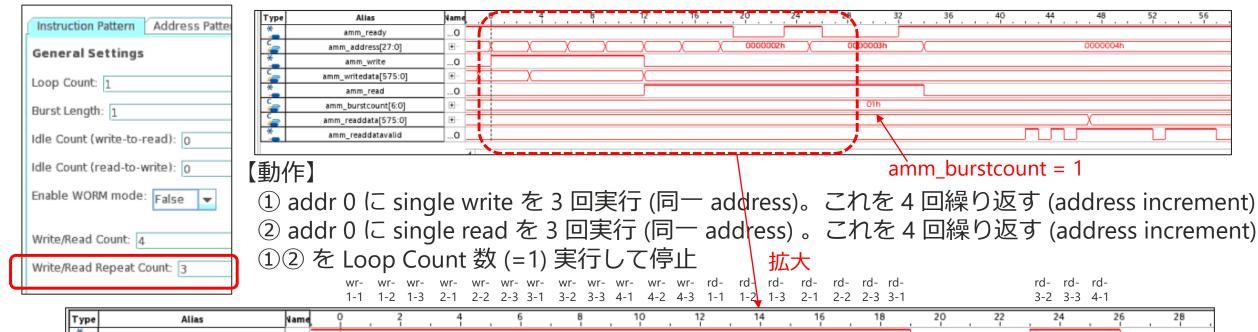

# Write/Read Repeat Count (1)

#### ● 同一アドレスにアクセスする回数を設定します

。 Write/Read Repeat Count = 3 の動作波形 (Loop Count = 1, Burst Length = 1)

- ① addr 0 に single write を 3 回実行 (同一 address)

- ② addr 0 に single read を 3 回業行 (同一 address)

- ①② を Loop Count 数 (=1) 実行して停止

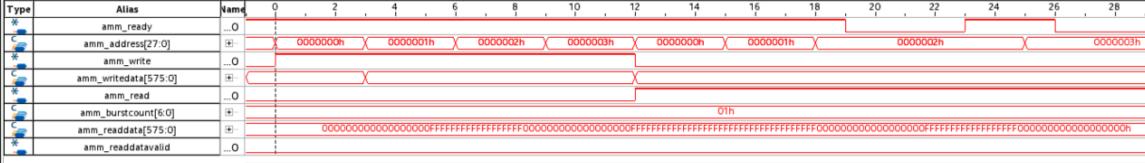

## Write/Read Repeat Count (2)

- 同一アドレスにアクセスする回数を設定します

- Write/Read Repeat Count = 3 の動作波形

- (Loop Count = 1, Burst Length = 1, Write/Read Count = 4)

00000004h

rd- rd-

3-2 3-3 4-1

© Macnica, Inc.

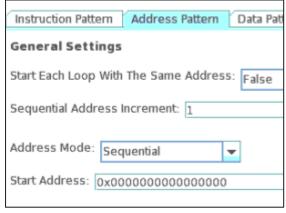

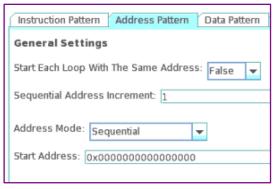

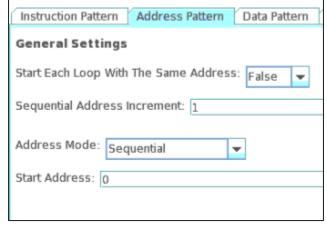

#### Address Pattern の設定項目について

| 項目                                                     | 説明                                                                      |

|--------------------------------------------------------|-------------------------------------------------------------------------|

| Start Each Loop with<br>The Same Address               | True 設定の場合、各ループの開始アドレスを同一にします。                                          |

| Sequential Address<br>Increment                        | Address Mode を Sequential にした場合のインクリメント・ステップを設定します。                     |

| Address Mode                                           | Address Mode を設定します。 ・Sequential ・Random ・Random Sequential             |

| Start Address                                          | 開始アドレスを設定します。                                                           |

| Num Rand-Seq<br>Address<br>(Random Sequential<br>Mode) | Address Mode を Random-Sequential にした場合の、<br>Sequential 動作を実行する回数を設定します。 |

© Macnica, Inc.

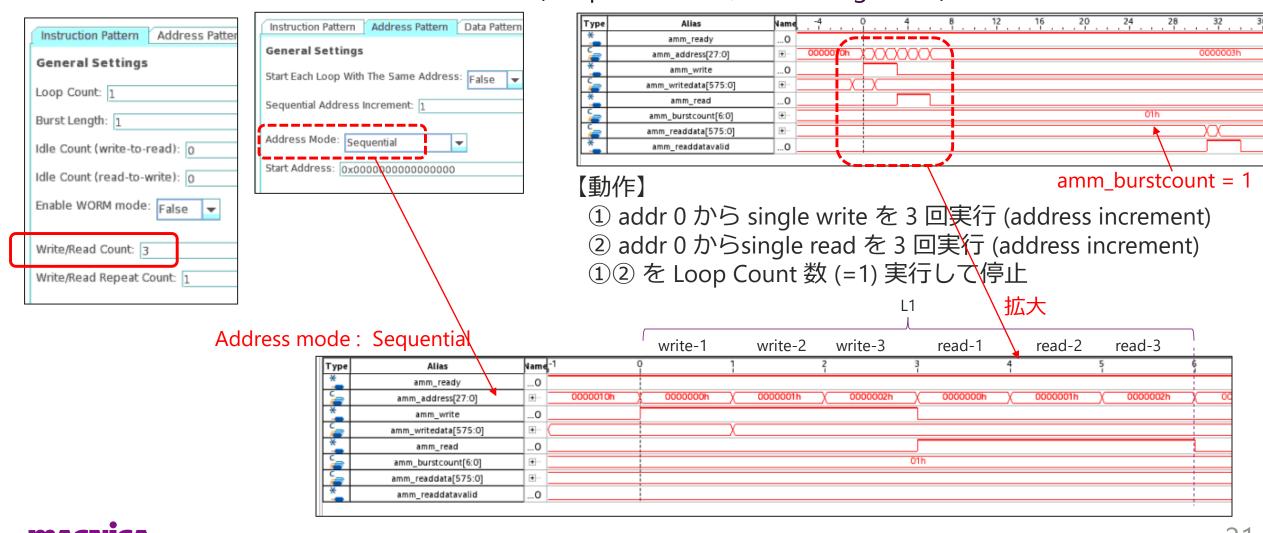

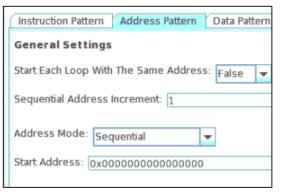

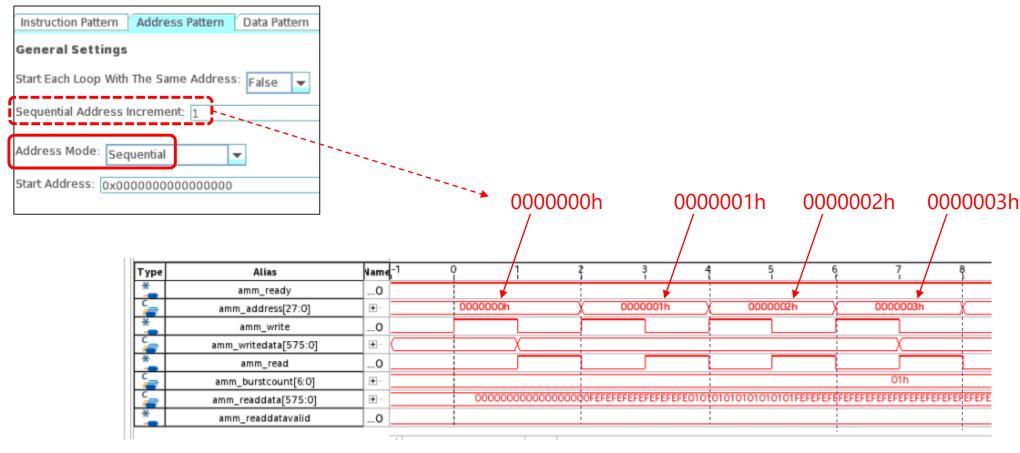

# **Address Mode: Sequential**

#### ● Address 値を インクリメントします

インクリメント動作のステップ値を設定します

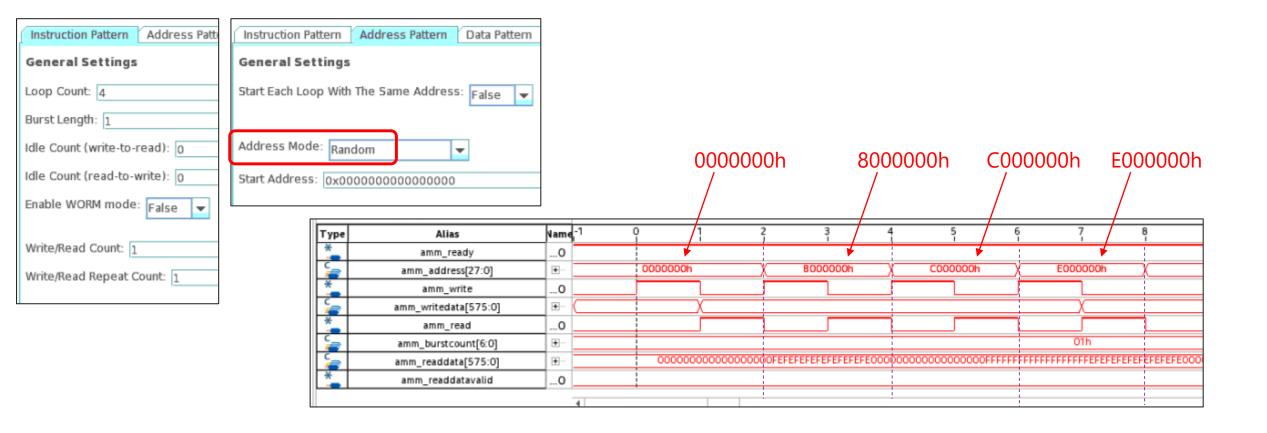

#### **Address Mode: Random**

● Address 値を Random に変更します

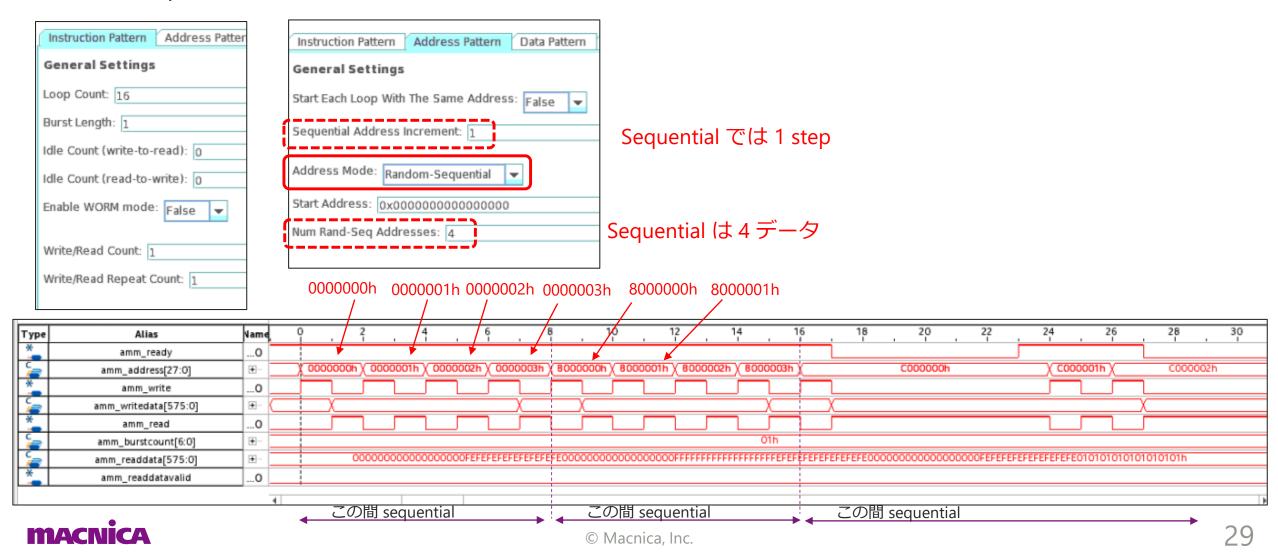

## **Address Mode: Random-Sequential**

- Address 値を Random と Sequential の組み合わせで変更します

- 。 Sequential のときのステップ値、回数を設定します

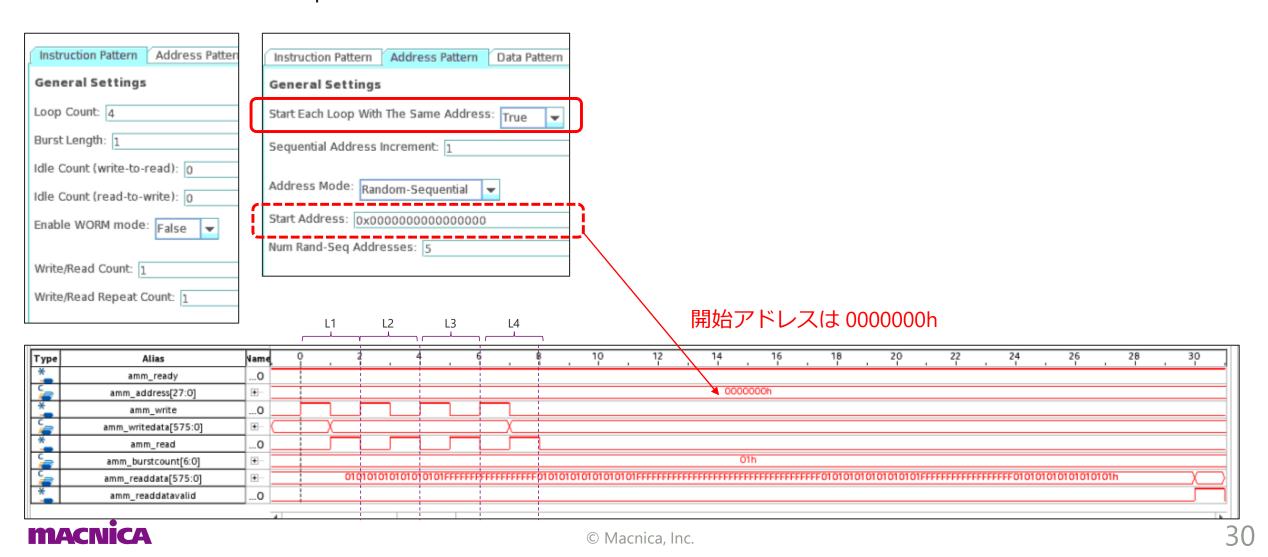

# **Select Each Loop With The Same Address**

- 各ループの開始アドレスを Start Address 設定値とします

- Select Each Loop With The Same Address = True

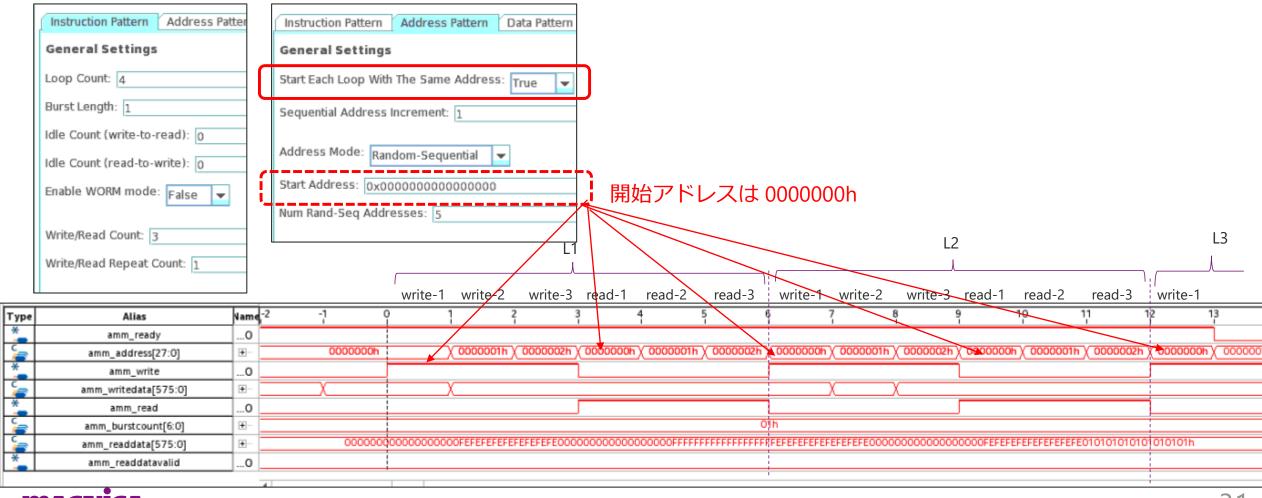

## **Select Each Loop With The Same Address**

- Select Each Loop With The Same Address = True

- Start Address = 0x0

- Loop Count = 4, Burst Length= 1, Write/Read Count = 3

**MACNICA**

3

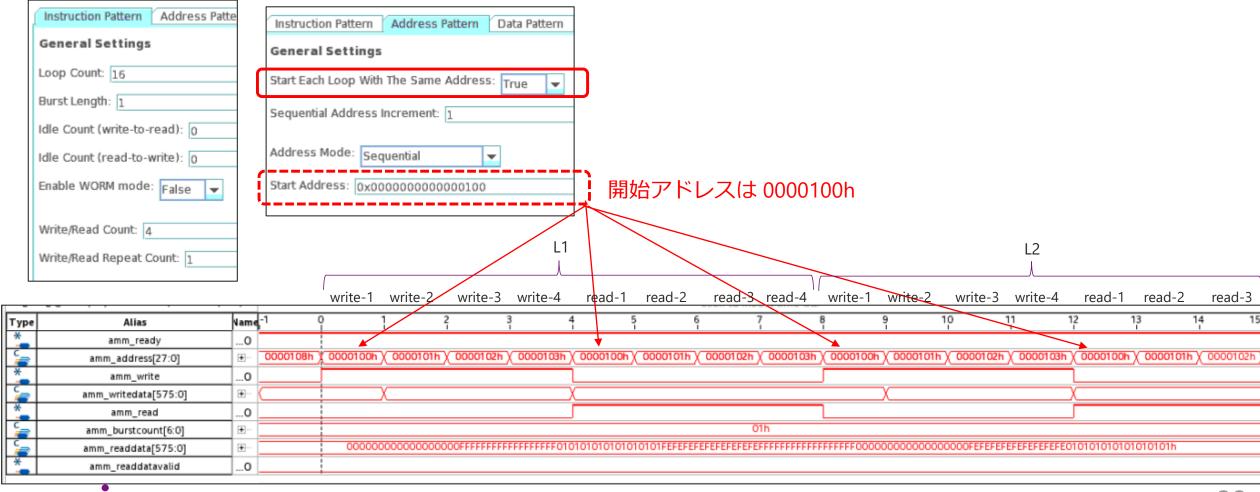

## **Select Each Loop With The Same Address**

- Select Each Loop With The Same Address = True

- Start Address = 0x100

- Loop Count = 16, Burst Length= 1, Write/Read Count = 3

**MACNICA**

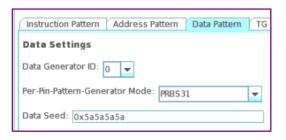

# Data Pattern MACA

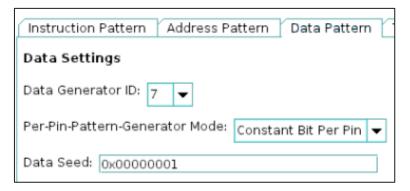

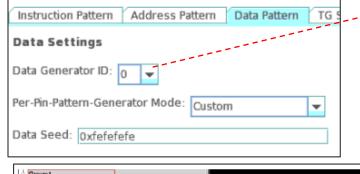

# Data Pattern タブについて

| 項目                                 | 説明                                                                                                                                    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Data Generator ID                  | 8 バースト動作設定時の ビートを指定します。 0-7 の間で選択して、それぞれのデータを設定することになります。 【例】 ID 0:8 バーストの最初のビートのデータ ID 1:8 バーストの 2 個目のビートのデータ ID 7:8 バーストの最後のビートのデータ |

| Per-Pin-Pattern-<br>Generator Mode | 各ピン毎のパターンを設定します。<br>(詳細は後述)                                                                                                           |

| Data Seed                          | 各データの Seed 値を設定します                                                                                                                    |

#### Data Pattern について

- DQ0 DQ7 について、8 バーストのパターンを設定します

- DQ0、DQ1、... DQ7 について、それぞれ個別に設定します

- DQ0 の 8bit を設定 ⇒ DQ0 が 8 バーストで出力するパターン

- DQ1 の 8bit を設定 ⇒ DQ1 が 8 バーストで出力するパターン

- DQ2 の 8bit を設定 ⇒ DQ2 が 8 バーストで出力するパターン

- DQ0 DQ7 以降は、この 8bit 単位の繰り返しとなります

- 。 DQ0 と DQ8, DQ16, DQ24, ... は同じ

- 。 DQ1 と DQ9, DQ17, DQ25, ... は同じ

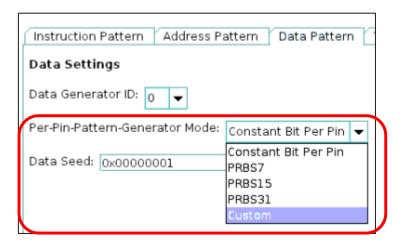

#### Per-Pin-Pattern-Generator-Mode

Per-Pin-Pattern-Generator-Mode、 および Data Seed は、 各 Data Generator ID (0 - 7) につい て個別に設定します

| Mode                 | 説明                                                                                                                                                  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed                | Data Seed の LSB 8bit を固定値として出力します。<br>【例】<br>Data Seed = $0x76543210$ の場合、<br>$0x10 \Rightarrow 0x10 \Rightarrow 0x10 \Rightarrow 0x10 \Rightarrow$ |

| PRBS 7               | Data Seed の LSB 8bit を入力 seed として PRBS パターンを<br>出力します。<br>多項式は、X <sup>7</sup> + X <sup>6</sup> + 1                                                  |

| PRBS 15              | Data Seed の LSB 16bit を入力 seed として PRBS パターンを<br>出力します。<br>多項式は、X <sup>15</sup> + X <sup>14</sup> + 1                                               |

| PRBS 31              | Data Seed 32bit を入力 seed として PRBS パターンを出力します。<br>多項式は、X <sup>31</sup> + X <sup>28</sup> + 1                                                         |

| Rotating<br>(custom) | Data Seed 32bit を、8bit ずつ LSB 側からを順に出力します<br>【例】<br>Data Seed = 0x76543210 の場合、<br>0x10 ⇒ 0x32 ⇒ 0x54 ⇒ 0x76 ⇒ 0x10 ⇒                               |

#### Data Pattern 設定例 (1)

```

Data Generator ID: 0: DQ[0] 0x00000001 Constant Bit Per Pin Data Generator ID: 1: DQ[1] 0x00000001 Constant Bit Per Pin Data Generator ID: 2: DQ[2] 0x00000001 Constant Bit Per Pin Data Generator ID: 3: DQ[3] 0x00000001 Constant Bit Per Pin Data Generator ID: 4: DQ[4] 0x00000001 Constant Bit Per Pin Data Generator ID: 5: DQ[5] 0x00000001 Constant Bit Per Pin Data Generator ID: 6: DQ[6] 0x00000001 Constant Bit Per Pin Data Generator ID: 7: DQ[7] 0x00000001 Constant Bit Per Pin

```

```

・8 バーストの 1 回目 : DQ[7:0] = 8'hFF (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 2 回目 : DQ[7:0] = 8'h00 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 3-7 回目 : DQ[7:0] = 8'h00 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

DQ = 72bit なので 9 個ずつ配置して、

amm_writedata[575:0] = {{9{8'h00} , {9{8'h00} ,

```

**MACNICA**

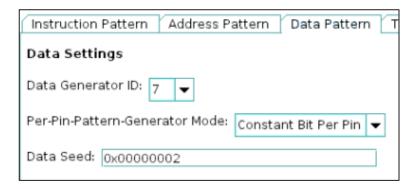

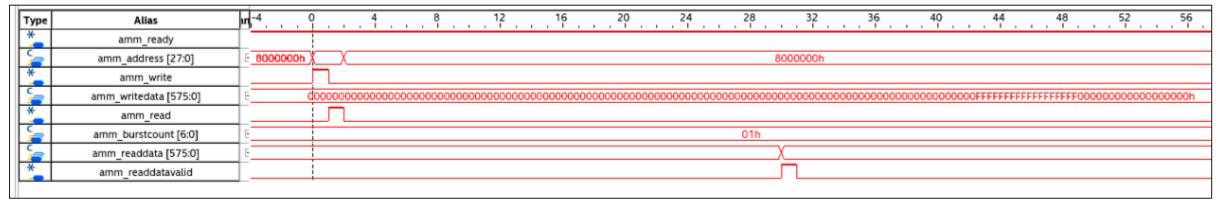

### Data Pattern 設定例 (2)

```

Data Generator ID: 0: DQ[0] 0x00000002 Constant Bit Per Pin Data Generator ID: 1: DQ[1] 0x00000002 Constant Bit Per Pin Data Generator ID: 2: DQ[2] 0x00000002 Constant Bit Per Pin Data Generator ID: 3: DQ[3] 0x00000002 Constant Bit Per Pin Data Generator ID: 4: DQ[4] 0x00000002 Constant Bit Per Pin Data Generator ID: 5: DQ[5] 0x00000002 Constant Bit Per Pin Data Generator ID: 6: DQ[6] 0x00000002 Constant Bit Per Pin Data Generator ID: 7: DQ[7] 0x00000002 Constant Bit Per Pin

```

```

・8 バーストの 1 回目 : DQ[7:0] = 8'h00 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 2 回目 : DQ[7:0] = 8'hFF (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 3-7 回目 : DQ[7:0] = 8'h00 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

DQ = 72bit なので 9 個ずつ配置して、

amm_writedata[575:0] = {{9{8'h00} , {9{8'h00} ,

```

**MACNICA**

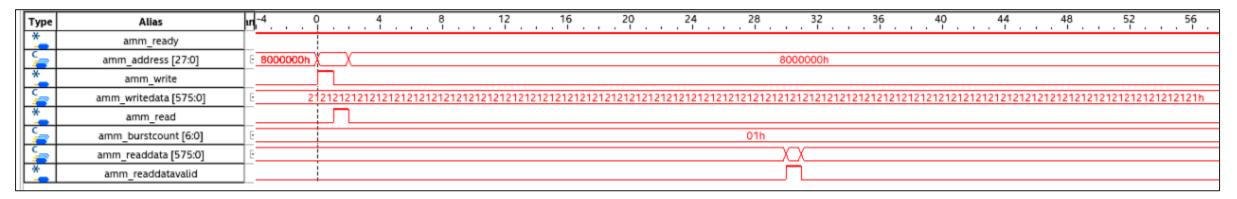

### Data Pattern 設定例 (3)

```

Instruction Pattern Address Pattern Data Pattern T

Data Settings

Data Generator ID: 0 ▼

Per-Pin-Pattern-Generator Mode: Constant Bit Per Pin ▼

Data Seed: 0x000000ff

```

```

Data Generator ID: 0: DQ[0] 0x000000FF Constant Bit Per Pin

Data Generator ID: 1: DQ[1] 0x000000FF Constant Bit Per Pin

Data Generator ID: 2: DQ[2] 0x00000000 Constant Bit Per Pin

Data Generator ID: 3: DQ[3] 0x00000000 Constant Bit Per Pin

Data Generator ID: 4: DQ[4] 0x00000000 Constant Bit Per Pin

Data Generator ID: 5: DQ[5] 0x00000000 Constant Bit Per Pin

Data Generator ID: 6: DQ[6] 0x00000000 Constant Bit Per Pin

Data Generator ID: 7: DQ[7] 0x00000000 Constant Bit Per Pin

```

```

・8 バーストの 1 回目 : DQ[7:0] = 8'h03 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 2 回目 : DQ[7:0] = 8'h03 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 3-7 回目: DQ[7:0] = 8'h03 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

DQ = 72bit なので 9 個ずつ配置して、

amm_writedata[575:0] = {{9{8'h03}, {9{8'h03}, {9{

```

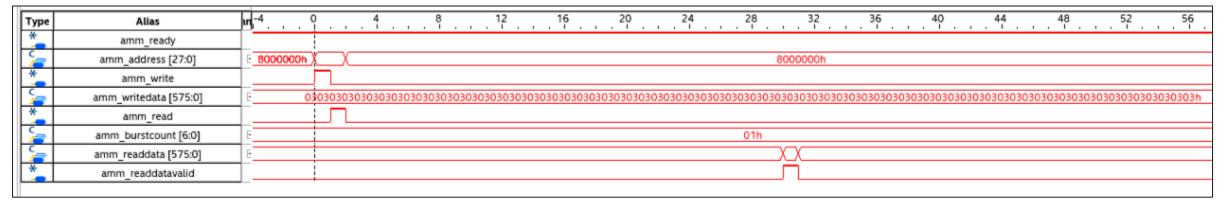

#### Data Pattern 設定例 (4)

```

Instruction Pattern Address Pattern Data Pattern T

Data Settings

Data Generator ID: 5 ▼

Per-Pin-Pattern-Generator Mode: Constant Bit Per Pin ▼

Data Seed: Ox000000FF

```

```

Data Generator ID: 0: DQ[0] 0x000000FF Constant Bit Per Pin

Data Generator ID: 1: DQ[1] 0x00000000 Constant Bit Per Pin

Data Generator ID: 2: DQ[2] 0x00000000 Constant Bit Per Pin

Data Generator ID: 3: DQ[3] 0x00000000 Constant Bit Per Pin

Data Generator ID: 4: DQ[4] 0x00000000 Constant Bit Per Pin

Data Generator ID: 5: DQ[5] 0x000000FF Constant Bit Per Pin

Data Generator ID: 6: DQ[6] 0x00000000 Constant Bit Per Pin

Data Generator ID: 7: DQ[7] 0x00000000 Constant Bit Per Pin

```

```

・8 バーストの 1 回目 : DQ[7:0] = 8'h21 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 2 回目 : DQ[7:0] = 8'h21 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

・8 バーストの 3-7 回目: DQ[7:0] = 8'h21 (= DQ[15:8] = DQ[23:16] = DQ[31:24] ... DQ[71:64] )

DQ = 72bit なので 9 個ずつ配置して、

amm_writedata[575:0] = {{9{8'h21}, {9{8'h21}, {9{

```

#### Traffic Preset Mode の選択

- Traffic Generator 2.0 では Preset Mode が選択可能です

- 。 プルダウンで選択可能です

# Preset について

| 項目                            | 説明                                                                                                     |

|-------------------------------|--------------------------------------------------------------------------------------------------------|

| Default                       | デフォルト・パターンが設定されます。<br>ループ回数 1 、 開始アドレス 0 などとなっています。<br>(本資料では設定画面の説明はございません)<br>データは 0x5a5a5a5a となります。 |

| Walking 1s                    | 各 DQS グループ内の DQ が 1つだけ 1 になり、それが 8<br>バースト動作中に各 DQ でシフトしていくパターンです。                                     |

| Walking 0s                    | 各 DQS グループ内の DQ が 1 つだけ 0 になり、それが 8<br>バースト動作中に各 DQ でシフトしていくパターンです。                                    |

| Read & Write Entire<br>Memory | 全アドレス領域に、Sequential mode で all '1' を設定する<br>パターンです。<br>バースト長は 64 に設定されます。                              |

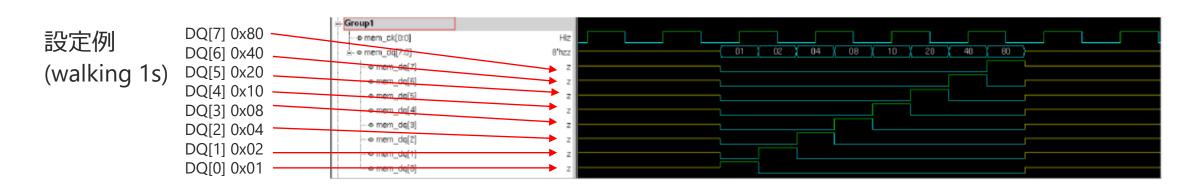

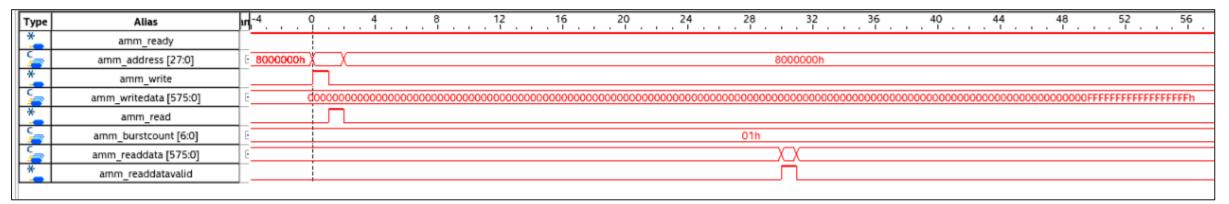

### **Traffic Preset Mode (1): Walking 1's**

● Walking 1's は、DQ[7:0] で 1 が シフトしていくパターンです

8 バーストの 1 回目: DQ[7:0] = 8'h01, 8 バーストの 2 回目: DQ[7:0] = 8'h02, .... {9{8'h80}} {9{8'h40}} {9{8'h20}} {9{8'h10}} {9{8'h10}} {9{8'h08}} {9{8'h04}} {9{8'h02}} {9{8'h02}}

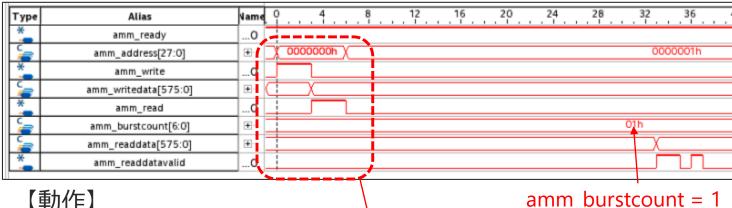

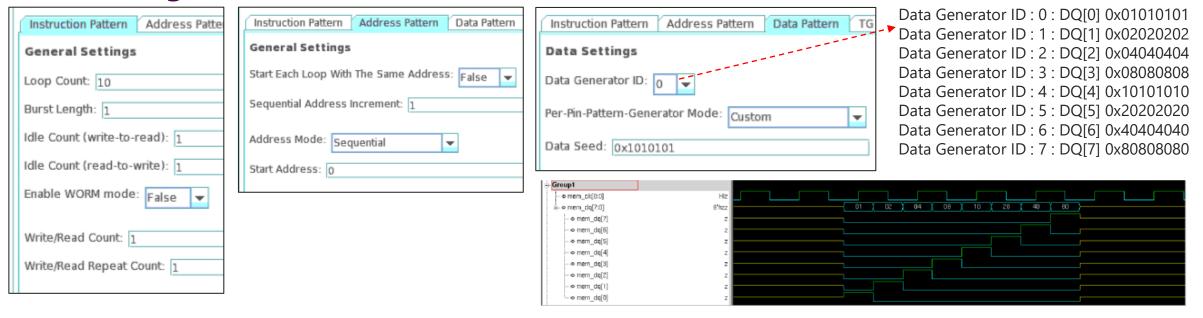

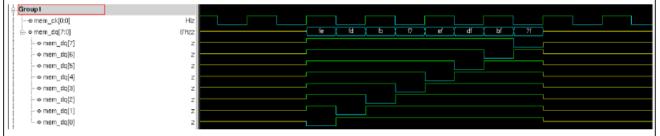

## **Traffic Preset Mode (2): walking 0's**

● Walking 0's は、DQ[7:0] で 0 が シフトしていくパターンです

Data Generator ID: 0: DQ[0] 0xFEFEFEFE

Data Generator ID: 1: DQ[1] 0xFDFDFDFD

Data Generator ID: 2: DQ[2] 0xFBFBFBFB

Data Generator ID: 3: DQ[3] 0xF7F7F7F7

Data Generator ID: 4: DQ[4] 0xEFEFEFEF

Data Generator ID: 5: DQ[5] 0xDFDFDFDF

Data Generator ID: 6: DQ[6] 0xBFBFBFBF

Data Generator ID: 7: DQ[7] 0x7F7F7F7F

8 バーストの 1 回目: DQ[7:0] = 8'hFE, 8 バーストの 2 回目: DQ[7:0] = 8'hFD, ....

{9{8'h7F}} {9{8'hBF}} {9{8'hDF}} {9{8'hEF}} {9{8'hF7}} {9{8'hFB}} {9{8'hFD}} {9{8'hFE}} Name 14 Alias Type amm\_ready 0000005h 0000006h 0000007h 0000008h 00000091 amm\_address[27:0] amm\_write amm\_writedata[575:0] .0 amm read amm\_burstcount[6:0] amm\_readdata[575:0] amm readdatavalid .0

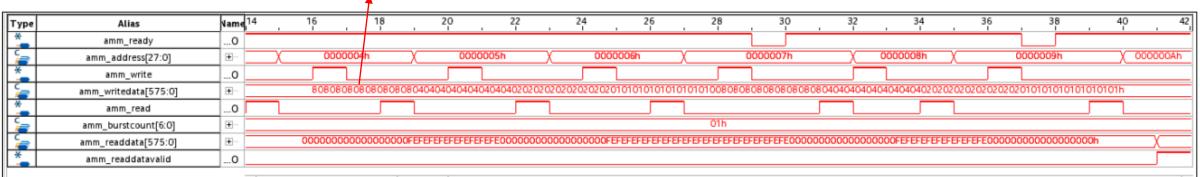

#### **Traffic Preset Mode (3): Read & Write Entire Memory**

- Read & Write Entire Memory は、全領域に FFh を ライト/リードします

- 。 64 バーストで ループして全領域にアクセスします

{72{8'hFF}} -32 -16 32 128 176 192 208 224 240 256 272 288 320 Alias ...0 amm ready 000000Ah 0000000h amm\_address[27:0] ...0 amm\_write amm\_writedata[575:0] ...0 amm\_burstcount[6:0] amm\_readdata[575:0] ...0 amm\_readdatavalid

# まとめ MACNICA

### まとめ

● Traffic Generator 2.0 では、ユーザー側でテスト・パターンの設定が可能です

● Traffic Preset Mode も用意されています

● テスト結果について、ビット毎に表示され、期待値と異なる場合エラー表示となります

#### 改版履歴

| Revision | 年月       | 概要   |

|----------|----------|------|

| 1.0      | 2021年10月 | 初版作成 |

|          |          |      |

弊社より資料を入手されたお客様におかれましては、下記の使用上の注意を一読いただいた上でご使用ください。

- 1. 本資料は非売品です。許可なく転売することや無断複製することを禁じます。

- 2. 本資料は予告なく変更することがあります。

- 3. 本資料の作成には万全を期していますが、万一ご不明な点や誤り、記載漏れなどお気づきの点がありましたら、弊社までご一報いただければ幸いです。

- 4. 本資料で取り扱っている回路、技術、プログラムに関して運用した結果の影響については、責任を負いかねますのであらかじめご了承ください。

- 5. 本資料は製品を利用する際の補助的な資料です。製品をご使用になる場合は、英語版の資料もあわせてご利用ください。

# MACNICA