1. 概要

Nios® V のブートは、Nios® II と同様に様々な方法があります。

この記事の内容は、SDM(Secure Device Manager)を搭載したデバイスを対象に、SDM に接続されている QSPI Flash ROM に Nios® V プロセッサーのコードを格納し、起動する方法をご紹介します。

SDM Boot に関しては、アルテラよりリファレンス・デザインが提供されております。このデザインをベースに環境を構築することが可能です。

参考資料: Stratix® 10 FPGA – SDM Bootloader for the Nios® V/m Processor Design Example

なお、本記事で扱う SDM Boot の構成をベースにした Sulfur ボード向け Reference Design を記事末尾に添付しています。

注記:

Stratix® 10 FPGA や Agilex™ ファミリーではセキュリティー機能が強化されていますが、これらのセキュリティー機能は SDM によって管理されます。Nios® V の SDM Boot を実施する際、SDM についての細かい知識は不要です。SDM の機能について興味のある方は下記の記事をご参照ください。

参考資料: Altera® Agilex™ FPGA 「セキュリティ」編

注記:

SDM ブートを使用するためには、FPGA のコンフィグレーション・モード(MSEL の設定)としてアクティブ・シリアル(AS-Fast もしくは AS-Normal)を選択する必要があります。Avalon-ST 方式など、アクティブ・シリアル以外のモードでコンフィグレーションされている場合、Nios® V プロセッサーは SDM ブートを実行することはできません。

Nios® V は SDM ブートのほかにも以下のブート方式に対応しています。それぞれ記事を用意しておりますので、詳細はそちらをご覧ください。

参考資料: Nios® V Boot Option ~ Generic Serial Flash Interface ~

参考資料: Nios® V Boot Option ~ On Chip RAM (XIP) ~ On-Chip Memory Boot ~

参考資料: Nios® V Boot Option ~ TCM Boot ~

1-1. 全体構成

下図に全体構成図を示します。

1-2. SDM ブートの流れ

SDM ブート は以下の流れで実行されます。

Nios® V プロセッサーは、オンチップメモリーから SDM ブートローダーを実行する

SDM ブートローダーは、SDM に接続されているコンフィグレーション Flash ROM に格納されている Nios® V プロセッサー向けソフトウェアを探す

SDM ブートローダーは、ソフトウェアをコンフィグレーション Flash ROM から On-Chip RAM や 外部 RAM にコピーする

コピー完了後、SDM ブートローダーからユーザー・アプリケーションにジャンプする

次章より実装方法をご紹介します。

2. ハードウェアの実装

この章ではハードウェアの実装方法を示します。ここでは Agilex™ 5 を例にしてご紹介します。

最低限必要な IP は下記の通りです(Quartus® Prime Pro Edition ソフトウェア・バージョン 25.3.1 の場合)。

Nios® V/m Micro controller IP

On-Chip Memory(RAM or ROM)IP(以下、On-Chip RAM と表記)

Mailbox Client IP

Platform Designer で構築すると下図のようになります。

この記事では、ユーザー・アプリケーションの拡張用に 各種ペリフェラルに接続するための PIO IP や、コンソール出力用に JTAG_UART IP を実装していますが、これらは必須ではありませんのでご注意ください。

また実装している各 IP の名前は視認性を上げるため下記のように設定しています:

Nios® V/m Micro controller IP : cpu

On-Chip Memory(RAM or ROM)IP : bootcopier_rom, bootcopier_ram, user_application_mem

Mailbox Client IP:mailbox

その他の IP の名前はこの記事に添付のデザインよりご確認ください。

最低限必要な上記 3つ の IP の パラメーター設定について次項で説明します。

2-1. Nios® V/m Processor

下図のように Traps, Exceptions, and Interrupts の項目で Reset Agent を "bootcopier_rom.s1" に設定してください。

注記:

Reset Agent : のプルダウンメニューを選択する際に、"bootcopier.s1" ポートが表示されないことがあります。その際は一度別のポートを選択後に、再度プルダウンメニューを開くことで選択可能になりますのでご注意ください。

注記:

Quartus® Prime のバージョンにより、Traps, Exceptions, and Interrupts 項目ではなく、Vector 項目の場合もありますのでご注意ください。

2-2. On-Chip Memory(RAM or ROM)IP

このデザインでは On-Chip RAM を 3 個使用します。以下にそれぞれの設定方法を説明します。

【図 4】、【図 5】、【図 6】 のようにソフトウェア実行に必要な Total Memory Size の設定と、On-Chip RAM に登録する初期値ファイルを指定するために、Memory Initialization の設定を行います。

2-2-1. bootcopier_rom の設定

Nios® II Processor では、memint.qip 使用する方法で登録ができましたが、Nios® V Processor で使用する RiscFree IDE では、meminit.qip を生成するコマンドが無いため、 上図のように "Enable non-default initialization file" にもチェックを入れて、< 任意の名前 >.hex ファイルのパスを登録する必要があります。

この記事では下記のように設定しています。

- Type : ROM(Read-only)

- Total memory size : 6144 Bytes

- User created initialization file : bootcopier_rom.hex

2-2-2. bootcopier_ram の設定

bootcopier_ram はデフォルト値で RAM を初期化します。この記事では下記のように設定しています。

- Type : RAM(Writable)

- Total memory size : 6144 Bytes

2-2-3. user_application_mem の設定

user_application_mem はデフォルト値で RAM を初期化します。この記事では下記のように設定しています。

- Type : RAM(Writable)

- Total memory size : 51200Bytes

2-3. Mailbox Client IP

Mailbox Client IP はデフォルトのまま使用します。

2-4. Quartus® Prime Settings

Assignments tab ⇒ Device ⇒ Device and Pin Options ⇒ Configuration を開いてください。

基板構成に応じて設定します。

- Configuration scheme: Active Serial x4(can use Configuration Device)

- Active serial clock source: FPGA を Configuration するときのクロック周波数を設定

3. ソフトウェアの実装

SDM Boot では、SDM Boot Loader を使用して User Application をワークメモリーに Load します。

この章では SDM Boot Loader の生成方法と User Application の Build 方法をご紹介します。

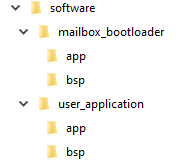

この記事では下図に示すディレクトリー構成を前提に説明します。

3-1. SDM Boot Loader

3-1-1. BSP の生成

Platform Designer より BSP Editor を起動して settings.bsp を作成します。作成方法がわからない場合は下記リンクをご参照ください。

参考資料: Ashling* RiscFree* IDE を使用した Nios® V プロジェクト開発手順

4. RiscFree* IDE での Nios® V プロセッサーの開発

BSP Editor の起動方法については Nios® II Processor と Nios® V/m Processor で違いがありますが、設定内容は同じであり hal の設定、hal.linker の設定、hal.make の設定、Linker Script の設定を行います。

- まず main タブにある hal、hal.kinker、hal.make を 【表 1】 と 【図 10】 ~ 【図 12】 を参考に設定します。

| Settings | 設定 |

| hal.max_file_descriptors | 4 |

| hal.log_port | None を選択します |

| hal.enable_exit hal.enable_clean_exit hal.c_plus_plus |

チェックを外します |

| hal.sys_clk_timer hal.timerstamp_timer hal.stdin hal.stdout hal.stderr |

None を選択します |

| hal.linker |

以下の設定にチェックを入れて有効にします allow_code_at_reset |

| hal.make.cflags_user_flags | -ffunction-sections -fdata-sections |

| hal.make.link_flags | -Wl,--gc-sections |

| hal.make.cflags_optimization | -Os |

- 次に BSP Software Package タブに移動し、altera_safeclib にチェックを入れます。

- Linker Script の設定は BSP Linker Script タブを選択し、下図のように .entry と .text 以外の Section を bootcopier_ram に設定します。

- 最後に BSP Drivers タブに移動し、Mailbox Cliant IP と Nios V/m Micro cotroller 以外の Driver を Enable 欄のチェックをはずして無効にしてください。

以上で BSP から Boot させるための設定は完了しました。[Generate BSP] ボタンをクリックして BSP を生成してください。

3-1-2. SDM Bootloader Application の生成

ここでは SDM Bootloader Application の生成方法を説明します。

SDM Bootloader Application は、本記事に付属する mailbox_bootloader.c、または下記リンクのソースコードをコピーしてご利用ください。

参考資料: 5.7.2.1.3. Software Design Flow (Bootloader via SDM Project)

"Create the Bootloader via SDM Application Project"

注記:

公開されているデザインは、Stratix® 10 SX SoC L-Tile development kit 向けのデザインであるため、Agilex™ 5 へのアプリケーションの流用はできません。

使用するデバイスによって Include するファイルが異なるため、mailbox_bootloader.c の編集を行います。この記事では Agilex™ 5 を利用するため、mailbox_bootloader.c 内の #inlucde を下記のように編集してください。

//#include "altera_s10_mailbox_client_flash.h" //Stratix10 or Agilex7 #include "intel_mailbox_client_flash.h" //Agilex5 or Agilex3

また、以下の MBOX_NAME と PAYLOAD_OFFSET の #define についても、ユーザーの仕様に合わせて編集が必要です。

// Design specific (customize here) #define MBOX_NAME "/dev/mailbox" #define PAYLOAD_OFFSET 0x200000

-

MBOX_NAME の変更:

system.h ファイル内の Mailbox Client IP の名称に合わせて、MBOX_NAME を変更します。

例 #define INTEL_MAILBOX_CLIENT_0_NAME "/dev/intel_mailbox_client_0"

-

PAYLOAD_OFFSET の変更:

QSPI フラッシュ上に格納される Nios® V アプリケーションの HEX ファイルの開始アドレスであり、SOF イメージの後ろの領域を指定してください。

「4-3. Configuration Devices」 で設定する QSPI の Partetion-2(P2)の Start Address と同じアドレスを設定する必要があります。

- SDM bootloader(mailbox_bootloader.c)を今回生成する software/mailbox_bootloader/app にコピーします。

- Nios® V Command Shell を起動し、以下コマンドを実行して CMakeLists.txt を作成します。

niosv-app --app-dir=software/mailbox_bootloader/app\

--bsp-dir=software/mailbox_bootloader/bsp\

--srcs=software/mailbox_bootloader/app- 次にアプリケーションをビルドします。

cmake -G "Unix Makefiles" -DCMAKE_BUILD_TYPE=Release -B \

software/mailbox_bootloader/app/Release -S \

software/mailbox_bootloader/appmake -C software/mailbox_bootloader/app/Release

- ビルド後、SDM bootloder(.elf)は以下のフォルダに生成されます。

| software/mailbox_bootloader/app/Release |

3-1-3. HEX File の生成と Memory の初期化

ソフトウェアのビルドが終了し ELF ファイルを生成したら、On-Chip RAM の初期値として登録する HEX ファイルを生成します。

- Nios® V Command shell を起動しプロジェクトまで移動します。移動後、以下のコマンドを入力して HEX ファイルを生成してください。

elf2hex software/mailbox_bootloader/app/release/app.elf \

-o bootcopier_rom.hex -b <base address of Bootloader ROM> \

-w <data width of Bootloader ROM> -e <end address of Bootloader ROM> -r 4- 生成された bootcopier_rom.hex は、bootcopier_rom の初期値として使用されます。Platform Designer にて指定した場所に bootcopier_rom.hex をコピーした後に、FPGA のコンパイルを実施してください。

注記:

Quartus® Prime をフル・コンパイルせずに、更新した HEX ファイルを SOF ファイルに反映させる方法は下記の資料をご参照ください。

参考資料: Nios® II - オンチップ・メモリからのブート手順

以上で SDM Bootloder の生成が完了しました。次のセクションでは User Application のビルド方法をご紹介します。

3-2. User Application

3-2-1. BSP の生成

Platform Designer より BSP Editor を起動して settings.bsp を作成します。作成方法がわからない場合は下記リンクをご参照ください。

参考資料: Ashling* RiscFree* IDE を使用した Nios® V プロジェクト開発手順

4. RiscFree* IDE での Nios® V プロセッサーの開発

BSP(settings.bsp)生成後、以降の設定を行います。

- hal.linker の設定は Main タブにある Settings ⇒ Advanced ⇒ hal の項目で、hal.linker オプションを下図のとおりに下記項目のチェックを入れます。

- enable_at_load

- enable_alt_load_copy_exceptions

- Linker Script の設定は BSP Linker Script タブを選択し、下図のとおりに .entry 以外の Section を "user_application_mem" に設定します。

3-2-2. Application の生成

Application プロジェクトを生成しビルドします。

ELF ファイルの生成までの手順は下記の記事をご参照ください。

参考資料: Ashling* RiscFree* IDE を使用した Nios® V プロジェクト開発手順

4-4. RiscFree* IDE の起動

3-2-3. HEX ファイルの生成

生成したアプリケーションは、JTAG Indirect Configuration(JIC)プログラミングと呼ばれる手法を用いて QSPI に書き込みます。JIC プログラミングを行うためには、JIC ファイル(.jic)が必要です。

ここでは JIC ファイル生成に必要な HEX ファイル(.hex)を生成します。

先程生成した ELF ファイルを以下コマンドを用いて HEX ファイルに変換します。

elf2flash --input software/user_application/app/debug/<user application>.elf \ --output flash.srec –epcs –-offset 0x0

riscv32-unknown-elf-objcopy --input-target srec \ --output-target ihex flash.srec \ <user application>.hex

次章にてプログラミングファイルの生成を行います。

4. プログラミングファイルの生成

生成された HEX ファイルを使用して JIC ファイルを生成します。JIC を生成するには Programing File Generator を起動します。 Programming File Generator では、 Output Files 、Input Files、Configuration Devices の設定を各タブで行います。

4-1. Output Files

このタブでは Generate 後のファイルのフォーマット、名前などを指定します。この記事では下記のように設定しています。

- Output Directry: 変更なし

- Name: output_file

- Description: JTAG Indirect Configuration File(.jic)ー> Memory Map File (.map)

4-2. Input Files

このタブでは JIC 生成に使用するファイルを設定します。

- まず [Add Bitstream] ボタンから、コンパイルして生成した SOF ファイルを登録します。

- 同様に [Add Raw Data] ボタンから、「3-2-3. HEX ファイルの生成」 で生成した HEX ファイルを登録します。登録後は、下図のように File Path に選択したファイルが表示されます。

- 登録した HEX ファイルは Bit swap をして、JIC を生成する必要があります。下図のように [Properties] ボタンから Input File Properties を表示し、Bit Swap を On にしてください

4-3. Configuration Devices

このタブでは、JIC 作成に関する各種設定を行います。

- まず書き込み対象の Flash デバイスの選択をします。下図の [Add Device] ボタンから所望の Flash デバイスを選択してください。

- 次に、登録された QSPI を選択し [Add Partition] ボタンから、QSPI のパーティションを作成します。SOF ファイルと HEX ファイルを格納するパーティションをそれぞれ作成するため、下記のように設定してください。

-

Name: P1

- Input file: 「4-2. Input Files」 で登録した、SOF ファイル

- Address Mode: Auto

-

Name: P2

- Input file: 「4-2. Input Files」 で登録した、HEX ファイル

- Address Mode: Start

- Start Address: mailbox_bootloader.c で定義した PAY LOAD offset

- パーティション登録後、Flash Loader の [Select] ボタンをクリックして、対象のデバイスを選択してください。

- 以上で各種設定は終了です。最後に [Generate] ボタンをクリックして下図の表示が出たら、JIC のファイルの生成は完了です。

5. Reference Design

本記事で紹介した Nios® V の SDM Boot 構成をベースに、 Sulfur ボード 向け Reference Design を用意しました。本デザインは Agilex™ 5 FPGA Eシリーズ を搭載した Sulfur ボードにて動作確認済みです。

なお、本デザインは記事内容の理解・検証を目的とした例であり、周辺回路やボード仕様が異なる環境へ流用する場合は、追加の調整が必要となります。

sulfur_niosv_m_sdmboot_QP25.3.1.zip

おわりに

この記事では、SDM を搭載したデバイスを対象に、SDM に接続されている QSPI Flash ROM に Nios® V プロセッサーのコードを格納して、起動する方法をご紹介しました。

Nios® V プロセッサーに関する情報については、下記メーカーのページより詳細をご確認いただけますので併せてご参照ください。

また、弊社では Nios® V に関する情報をまとめた「Nios® V まとめページ」をご用意しております。本記事以外にも有用な情報がありますので、こちらも併せてご確認ください。