可能です。HPS 専用 I/O を FPGA 側から制御するためのインタフェースとして、LOANIO というモードが利用可能です。

(Platform Designer (旧 Qsys) の HPS 設定 (Peripheral Pins タブの Peripherals Mux Table にて LANIOxx を選択))

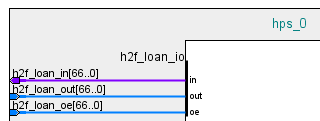

LoanIO が 1 ポート以上有効になると、HPS に以下のインタフェースが追加されますので、これらの信号を制御可能です。

h2f_loan_in[66:0]

h2f_loan_out[66:0]

h2f_loan_oe[66:0]

注意点

・HPS側でブートローダー(Preloader)を実行して、PinMux のレジスタ設定が行われた後でないと制御できません。

・PinMuxの設定が完了した時点で、FPGA側のコンフィギュレーションが行われていない場合には、

コンフィギュレーション完了までの期間は High 出力となります。

--------------------

カテゴリ:SoC

ツール:Quartus® Prime (Platform Designer)

デバイス:Cyclone® V